本章的實(shí)驗(yàn)任務(wù)是在 PL 端自定義一個(gè) AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進(jìn)行讀寫測試,讀寫的內(nèi)存大小是 4K 字節(jié)。

2025-11-24 09:19:42 3467

3467

本小節(jié)通過使用XPS中的定制IP向?qū)?ipwiz),為已經(jīng)存在的ARM PS 系統(tǒng)添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結(jié)構(gòu),并掌握AXI Lite IP的定制方法,為后續(xù)編寫復(fù)雜AXI IP打下基礎(chǔ)。同時(shí)本小

2012-12-23 15:39:12 19150

19150 作者:Mculover666 1.實(shí)驗(yàn)?zāi)康?用HDL語言+Vivado創(chuàng)建一個(gè)掛載在AXI總線上的自定義IP核 2.實(shí)驗(yàn)步驟 2.1.創(chuàng)建一個(gè)新的項(xiàng)目 ? ? 2.2.調(diào)用Create

2020-12-21 16:34:14 4566

4566

FPGA+ARM是ZYNQ的特點(diǎn),那么PL部分怎么和ARM通信呢,依靠的就是AXI總線。這個(gè)實(shí)驗(yàn)是創(chuàng)建一個(gè)基于AXI總線的GPIO IP,利用PL的資源來擴(kuò)充GPIO資源。通過這個(gè)實(shí)驗(yàn)迅速入門

2020-12-25 14:07:02 6724

6724

在某些情況下,通過嗅探 AXI 接口來分析其中正在發(fā)生的傳輸事務(wù)是很有用的。在本文中,我將為大家演示如何創(chuàng)建基本 AXI4-Lite Sniffer IP 以對特定地址上正在發(fā)生的讀寫傳輸事務(wù)進(jìn)行計(jì)數(shù)。

2022-07-08 09:35:34 1394

1394 由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊講解時(shí)序比較分散。所以筆者收藏AXI協(xié)議的幾種時(shí)序,方便編程。

2022-08-02 12:42:17 9562

9562 AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統(tǒng)外設(shè)上生成特定序列(流量)。它根據(jù)IP的編程和選擇的操作模式生成各種類型的AXI事務(wù)。是一個(gè)比較好用的AXI4協(xié)議測試源或者AXI外設(shè)的初始化配置接口。

2023-11-23 16:03:45 5162

5162

Xilinx的FIR IP核屬于收費(fèi)IP,但是不需要像 Quartus那樣通過修改license文件來破解。如果是個(gè)人學(xué)習(xí),現(xiàn)在網(wǎng)絡(luò)上流傳的license破解文件在破解Vivado的同時(shí)也破解

2025-03-01 14:44:19 2709

2709

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號(hào)的時(shí)鐘并行視頻數(shù)據(jù),即同步sync或消隱blank信號(hào)或者而后者皆有)轉(zhuǎn)換成AXI4-Stream接口形式,實(shí)現(xiàn)了接口轉(zhuǎn)換。該IP還可使用VTC核,VTC在視頻輸入和視頻處理之間起橋梁作用。

2025-04-03 09:28:14 2418

2418

https://gist.github.com/promach/251cbb3c9c9af401bf712dc4ccb76fb3為何這個(gè) AXI 代碼 不通過 AXI Protocol

2020-02-28 13:44:01

、通信模型圖4?10 AXI主設(shè)備與從設(shè)備之間的通信從上圖很容易看出,要通過AXI總線實(shí)現(xiàn)通信,我們需要一個(gè)主設(shè)備/上位機(jī)(Master)和一個(gè)從設(shè)備/下位機(jī)(Slave),并通過AXI總線將其相連。我們

2022-04-08 10:45:31

Arm AMBA協(xié)議集中,AXI協(xié)議是基于burst的嗎?

2022-09-28 10:21:03

發(fā)生IP核鎖定,一般是Vivado版本不同導(dǎo)致的,下面介紹幾種方法: 1 常用的方法 1)生成IP核的狀態(tài)報(bào)告 Report -》 Report IP Status 2)點(diǎn)擊

2021-01-08 17:12:52

Vivado中xilinx_courdic IP核(求exp指數(shù)函數(shù))使用

2021-03-03 07:35:03

Vivado浮點(diǎn)數(shù)IP核的握手信號(hào)

我們的設(shè)計(jì)方案中,F(xiàn)PU計(jì)算單元將收到的三條數(shù)據(jù)和使能信號(hào)同步發(fā)給20多個(gè)模塊,同時(shí)只有一個(gè)模塊被時(shí)鐘使能,進(jìn)行計(jì)算,但結(jié)果都會(huì)保留,發(fā)給數(shù)選。計(jì)算單元還需接受

2025-10-24 07:01:36

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因?yàn)楣こ讨泻芏?b class="flag-6" style="color: red">IP核不能用所以在重新生成過程中發(fā)現(xiàn)了這個(gè)問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

今天有空來學(xué)習(xí)一下xilinx的axi_iic ip。下面的鏈接是xilinx官網(wǎng)關(guān)于axi_iic的數(shù)據(jù)手冊,大家點(diǎn)一下就可以看了pg090-axi-iic pdf數(shù)據(jù)手冊先給我們這個(gè)ip的頂層

2022-01-18 07:00:13

,int b);最后經(jīng)過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調(diào)用自己寫的IP核(add函數(shù))我在vivado 中添加了自定義IP核與PS(處理系統(tǒng))我知道網(wǎng)上說用AXI Steam? 來連接

2016-01-28 18:40:28

,int b);最后經(jīng)過編譯可以生成VHDL等硬件描述文件與IP核文件.我想調(diào)用自己寫的IP核(add函數(shù))我在vivado 中添加了自定義IP核與PS(處理系統(tǒng))我知道網(wǎng)上說用AXI Steam? 來連接

2016-01-28 18:39:13

大家伙,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

vivado中,怎么將e203內(nèi)核源代碼封裝成ip核,并添加總線?

2025-11-10 07:22:49

請教一下,vivado怎么把帶ip核的工程進(jìn)行封裝,保證代碼不可見,可以通過端口調(diào)用。我嘗試了以下方法,ippackage,如果要在另一個(gè)程序里調(diào)用,也要提供源代碼;另一個(gè)方法是將網(wǎng)表文件edf文件與端口聲明結(jié)合,這種方法只能實(shí)現(xiàn)不帶ip核的封裝

2017-07-14 09:18:30

vivado三種常用IP核的調(diào)用當(dāng)前使用版本為vivado 2018.3vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)

2021-07-29 06:07:16

的情況時(shí),總會(huì)遇到一些以前未曾接觸過的新內(nèi)容,這些新內(nèi)容會(huì)讓我們感到陌生和恐懼,不知道該如何下手。

那么今天以xilinx vivado 為例分享學(xué)習(xí)FPGA 新IP核的正確打開方式。

一、常規(guī)

2023-11-17 11:09:22

時(shí),需要通過AXI互聯(lián)IP(AXI Interconnect)來實(shí)現(xiàn)多對多的拓?fù)浣Y(jié)構(gòu) ,如圖3所示。Interconnect擁有多個(gè) Master/Slave接口,并在內(nèi)部基于輪詢或者優(yōu)先級(jí)策略對多路數(shù)據(jù)進(jìn)行路由轉(zhuǎn)發(fā),可以實(shí)現(xiàn)系統(tǒng)內(nèi)部的高效通信。

圖3 多對多拓?fù)浣Y(jié)構(gòu)

相關(guān)視頻見B站 用戶名:專注與守望

2025-06-02 23:05:19

4和PCIE之間有什么聯(lián)系,敬請關(guān)注我們的連載系列文章。在本篇文章中暫時(shí)先不講解AXI4協(xié)議,先來分享例化AXI4的自定義IP核詳細(xì)步驟。一、 新建工程為了節(jié)省篇幅,新建工程部分就不詳細(xì)講解,以下為我們

2019-12-13 17:10:42

VDMA端口信號(hào)

S_AXI_LITE:PS端可以通過AXI_LITE協(xié)議對IP核進(jìn)行控制;

S_AXIS_S2MM:視頻流(AXI STREAM)輸入到IP核的FIFO中

2025-10-28 06:14:54

及程序分析三、自定義IP開發(fā)30_自定義IP原理介紹31_自定義IP之Vivado創(chuàng)建流程32_自定義IP之Vitis工程創(chuàng)建及程序分析四、雙核裸機(jī)開發(fā)33_雙核裸機(jī)中斷使用及雙核數(shù)據(jù)交互實(shí)驗(yàn)五

2022-07-21 10:34:51

(1個(gè)):是ARM多核架構(gòu)下定義的一種接口,中文翻譯為加速器一致性端口,用來管理DMA之類的不帶緩存的AXI外設(shè),PS端是Slave接口。我們可以雙擊查看ZYNQ的IP核的內(nèi)部配置,就能發(fā)現(xiàn)上述的三種

2018-01-08 15:44:39

。1 axi_gpio_led_demo案例1.1 案例功能案例功能:PS端通過AXI4-Lite總線發(fā)送命令至PL端AXI GPIO IP核,IP核再根據(jù)命令控制評(píng)估底板PL端LED5的狀態(tài)?圖

2021-05-28 14:28:28

ZYNQ自定義AXI總線IP應(yīng)用——PWM實(shí)現(xiàn)呼吸燈效果一、前言 在實(shí)時(shí)性要求較高的場合中,CPU軟件執(zhí)行的方式顯然不能滿足需求,這時(shí)需要硬件邏輯實(shí)現(xiàn)部分功能。要想使自定義IP核被CPU訪問

2020-04-23 11:16:13

的MODBUS 協(xié)議處理IP,而要使我們的MODBUS IP能夠靈活方便的進(jìn)行數(shù)據(jù)收發(fā)并和處理器進(jìn)行通信,必須為IP設(shè)計(jì)AXI接口,所以,因此掌握AXI IP核的創(chuàng)建流程及通信機(jī)制顯得尤為重要。要正確的封裝

2016-12-16 11:00:37

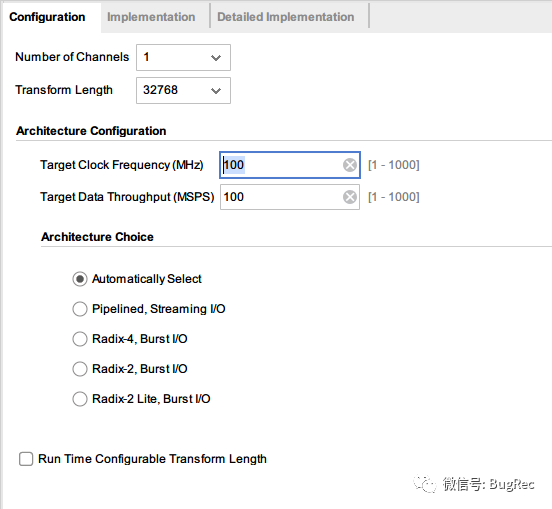

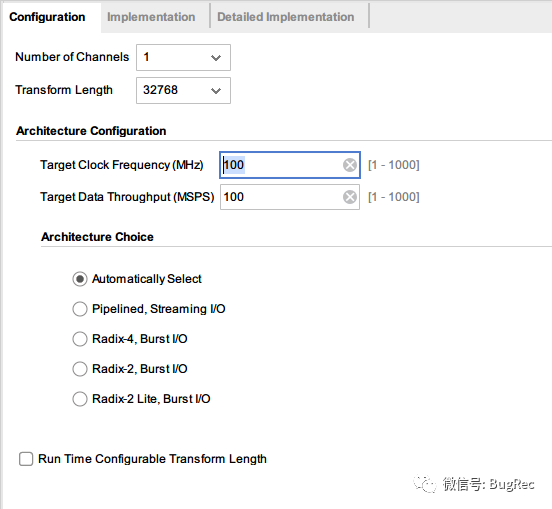

和HLS核之間進(jìn)行數(shù)據(jù)傳輸。它可以通過AXI1接口與PS部分的ARM Core和DDR進(jìn)行通信,以及通過AXI Stream接口與PL部分的FFT IP核。

FFT IP Core:這是一個(gè)基于IP核

2023-10-02 22:03:13

。關(guān)于如何實(shí)現(xiàn)AXI4通信協(xié)議,以及如何在設(shè)計(jì)中使用該協(xié)議進(jìn)行通信,我們將硬件設(shè)計(jì)部分進(jìn)行講解。9.2實(shí)驗(yàn)任務(wù)本章的實(shí)驗(yàn)任務(wù)是通過自定義一個(gè)AXI4接口的IP核,通過AXI接口對DDR3進(jìn)行讀寫測試

2020-10-22 15:16:34

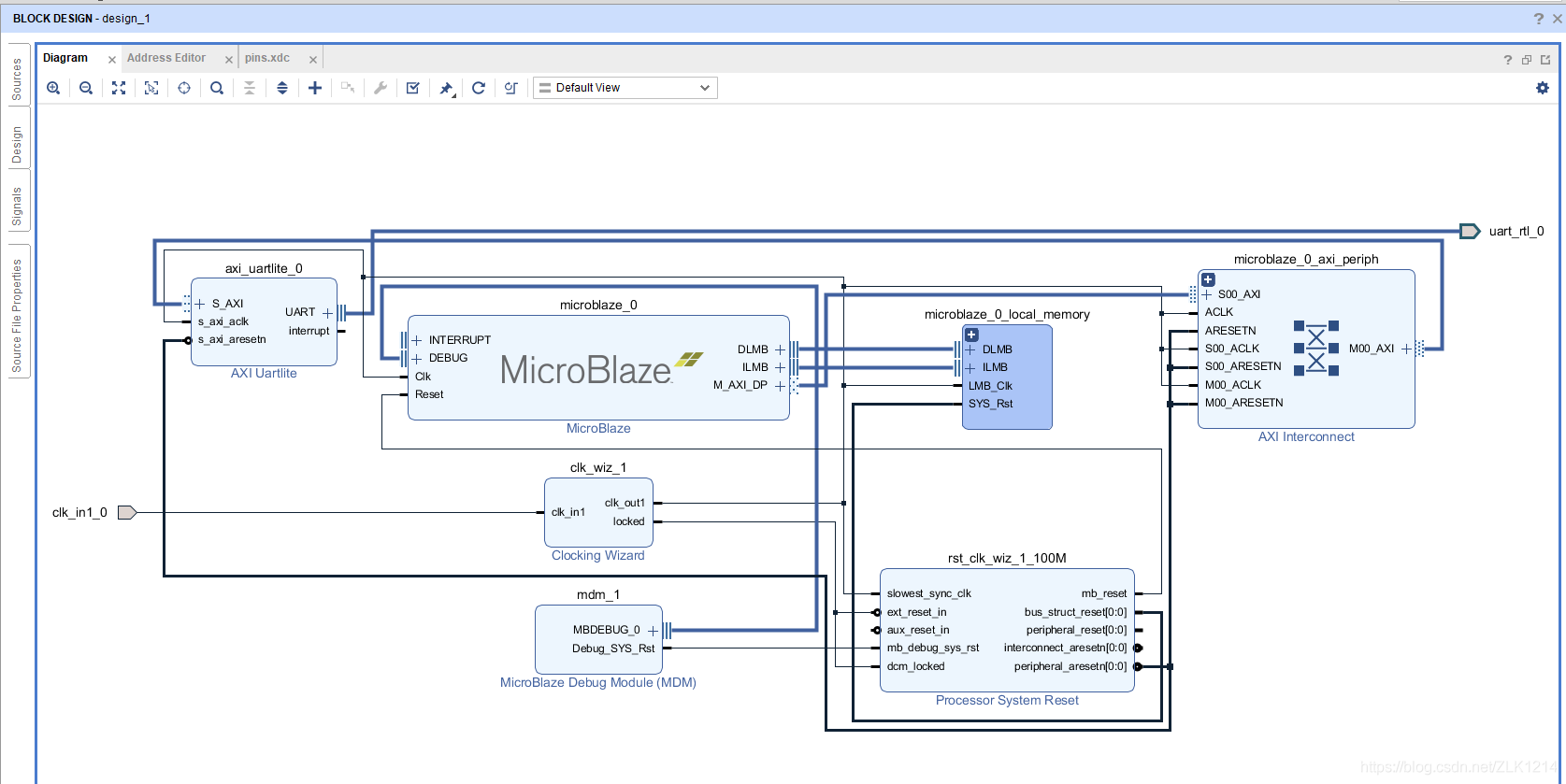

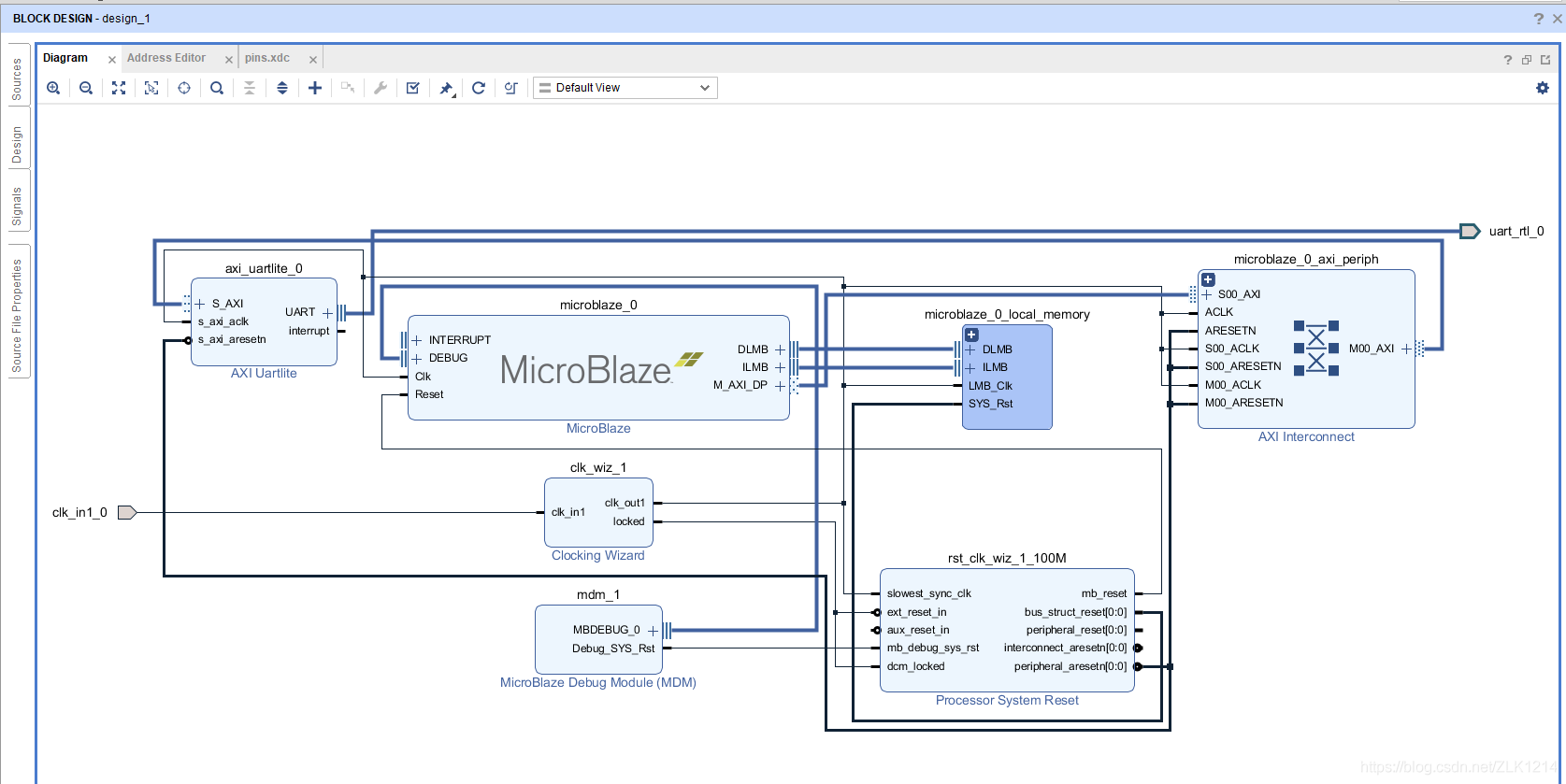

,即創(chuàng)建一個(gè)帶有AXI接口的IP核,該IP核通過AXI協(xié)議實(shí)現(xiàn)MicroBlaze軟核處理器和可編程邏輯的數(shù)據(jù)通信。AXI協(xié)議是一種高性能、高帶寬、低延遲的片內(nèi)總線,關(guān)于該協(xié)議的詳細(xì)內(nèi)容,我們會(huì)在

2020-10-19 16:04:35

,當(dāng)然也可以創(chuàng)建一個(gè)帶有AXI4接口的IP核,用于MicroBlaze軟核處理器和可編程邏輯的數(shù)據(jù)通信。本次實(shí)驗(yàn)選擇常用的方式,即創(chuàng)建一個(gè)帶有AXI接口的IP核,該IP核通過AXI協(xié)議實(shí)現(xiàn)

2020-10-17 11:52:28

Vivado軟件中,通過創(chuàng)建和封裝IP向?qū)У姆绞絹碜远xIP核,支持將當(dāng)前工程、工程中的模塊或者指定文件目錄封裝成IP核,當(dāng)然也可以創(chuàng)建一個(gè)帶有AXI4接口的IP核,用于PS和PL的數(shù)據(jù)通信。本次實(shí)驗(yàn)

2020-09-09 17:01:38

ap_none接口的IP核。在本章我們將通過呼吸燈實(shí)驗(yàn),來學(xué)習(xí)如何使用Vivado HLS工具生成一個(gè)帶有AXI4-Lite總線接口的IP核,并學(xué)習(xí)Vivado HLS工具C/RTL協(xié)同仿真平臺(tái)的使用,以及在

2020-10-10 17:01:29

和M_AXI_HPM0_LPD。 位于PS端的ARM直接有硬件支持AXI接口,而PL則需要使用邏輯實(shí)現(xiàn)相應(yīng)的AXI協(xié)議。Xilinx在Vivado開發(fā)環(huán)境里提供現(xiàn)成IP如AXI-DMA,AXI

2021-01-07 17:11:26

、ARM的AMBA等。因?yàn)?b class="flag-6" style="color: red">核的多樣性,使用完全相同的接口是不現(xiàn)實(shí)的,OCP將軟件中的分層概念應(yīng)用到IP核接口,提供一種具有通用結(jié)構(gòu)定義、可擴(kuò)展的接口協(xié)議,方便了IP核與系統(tǒng)的集成。OCP協(xié)議使IP核與系統(tǒng)

2019-06-11 05:00:07

封裝接口模塊;從Master出來并進(jìn)入Slave的箭頭表示請求命令,從Slave出來并進(jìn)入Master的箭頭表示響應(yīng);加黑的線段代表片上互連總線。兩個(gè)IP核通過接口通信的過程是:作為Master

2018-12-11 11:07:21

是對的,請糾正我,但我認(rèn)為這一步只需按一個(gè)按鈕)3 - 將IP內(nèi)核導(dǎo)入Vivado并: a-生成塊設(shè)計(jì)(這是我最不舒服的步驟,我會(huì)很高興獲得一些好的建議,因?yàn)樗惴ê軓?fù)雜且IP核不是基本的) b-合成,實(shí)現(xiàn)

2020-03-24 08:37:03

有人知道為什么MIG IP核中的AXI協(xié)議。為什么沒有AXI_WID這個(gè)信號(hào)呢。

2018-04-13 09:22:30

RT 學(xué)習(xí)CAN 發(fā)現(xiàn)PL端可以有現(xiàn)成的IP核使用,我的lincense 只支持 AXI-CAN 的調(diào)試使用,生成不了bit流,求一個(gè)可以生成bit的lincense,十分感謝!

2022-07-22 11:03:30

`玩轉(zhuǎn)Zynq連載21——Vivado中IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https://pan.baidu.com

2019-09-04 10:06:45

大家伙,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-16 11:42:55

嗨,我在Vivado 2016.3模塊設(shè)計(jì)中集成了PCIe DMA BAR0 AXI Lite接口和AXI IIC IP。在DMA IP端,它顯示S_AXI_Lite端口,但在AXI_IIC IP端

2020-05-14 09:09:35

在介紹IEEE802.11MAC 協(xié)議結(jié)構(gòu)的基礎(chǔ)上,給出協(xié)議開發(fā)的方法和步驟,提出IEEE802.11MAC 協(xié)議在32 位ARM7TDMI 微處理器S3C4510B 上的一種移植方案,開發(fā)出了嵌入式IEEE802.11MAC 協(xié)議的IP核。同時(shí)

2009-05-16 14:23:46 10

10 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言

2017-02-08 13:08:11 3085

3085

本小節(jié)通過使用XPS中的定制IP向?qū)?ipwiz),為已經(jīng)存在的ARM PS 系統(tǒng)添加用戶自定IP(Custom IP ),了解AXI Lite IP基本結(jié)構(gòu),并掌握AXI Lite IP的定制方法,為后續(xù)編寫復(fù)雜AXI IP打下基礎(chǔ)。

2017-02-10 20:37:12 6312

6312 本文先總結(jié)不同AXI IP核的實(shí)現(xiàn)的方法,性能的對比,性能差異的分析,可能改進(jìn)的方面。使用的硬件平臺(tái)是Zedboard。 不同的AXI總線卷積加速模塊的概況 這次實(shí)現(xiàn)并逐漸優(yōu)化了三個(gè)版本的卷積加速模塊,先簡要描述各個(gè)版本的主要內(nèi)容。

2018-06-29 14:34:00 8923

8923

IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言

2017-11-15 11:19:14 10744

10744 作者:薩其日娜 內(nèi)蒙古魯電電力工程有限公司 摘要: 應(yīng)用MicroBlaze軟核作為CPU的硬件平臺(tái),在此平臺(tái)上設(shè)計(jì)了基于AXI總線的通用實(shí)時(shí)時(shí)鐘IP核。給出了創(chuàng)建IP核的過程和導(dǎo)入IP核的方法

2017-11-17 16:34:42 4414

4414 本文包含兩部分內(nèi)容:1)AXI接口簡介;2)AXI IP核的創(chuàng)建流程及讀寫邏輯分析。 1AXI簡介(本部分內(nèi)容參考官網(wǎng)資料翻譯) 自定義IP核是Zynq學(xué)習(xí)與開發(fā)中的難點(diǎn),AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天咱們來聊一聊vivado 調(diào)用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 了解如何使用Vivado的創(chuàng)建和封裝IP功能創(chuàng)建可添加自定義邏輯的AXI外設(shè),以創(chuàng)建自定義IP。

2018-11-29 06:48:00 7675

7675

了解如何使用Vivado Design Suite IP Integrator有效地調(diào)試AXI接口。

本視頻介紹了如何使用該工具的好處,所需的調(diào)試步驟和演示。

2018-11-29 06:00:00 4497

4497 由于ZYNQ架構(gòu)和常用接口IP核經(jīng)常出現(xiàn) AXI協(xié)議,賽靈思的協(xié)議手冊講解時(shí)序比較分散。所以筆者收藏AXI協(xié)議的幾種時(shí)序,方便編程。

2019-05-12 09:10:33 11736

11736

自定義sobel濾波IP核 IP接口遵守AXI Stream協(xié)議

2019-08-06 06:04:00 4566

4566 ? Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 前年,發(fā)表了一篇文章《VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時(shí)遇到的一些問題及解決方案,發(fā)表之后經(jīng)過一年多操作上也有

2021-03-22 10:31:16 5360

5360 設(shè)計(jì)。最后介紹了基于AXI協(xié)議的設(shè)計(jì)實(shí)例,探討了利用IP復(fù)用技術(shù)和DesginWare IP搭建基于AXI協(xié)議的SOC系統(tǒng)。

2021-04-12 15:47:39 28

28 本講使用matlab產(chǎn)生待濾波信號(hào),并編寫testbench進(jìn)行仿真分析,在Vivado中調(diào)用FIR濾波器的IP核進(jìn)行濾波測試,下一講使用兩個(gè)DDS產(chǎn)生待濾波的信號(hào),第五講或第六講開始編寫verilog代碼設(shè)計(jì)FIR濾波器,不再調(diào)用IP核。

2021-04-27 18:18:51 5091

5091

vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如數(shù)學(xué)運(yùn)算(乘法器、除法器、浮點(diǎn)運(yùn)算器等)、信號(hào)處理(FFT、DFT、DDS等)。IP核類似編程中的函數(shù)庫(例如C語言中的printf()函數(shù)),可以直接調(diào)用,非常方便,大大加快了開發(fā)速度。

2021-04-27 15:45:12 25681

25681

使用Vivado Design Suite創(chuàng)建硬件。 3. 在Vitis 統(tǒng)一軟件平臺(tái)中編寫軟件并在板上運(yùn)行。 01 導(dǎo)出 IP 在AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,我們創(chuàng)建了 1 個(gè)包含 AXI4-Lite 接

2021-04-26 17:32:26 5439

5439

在一個(gè)項(xiàng)目中,當(dāng)你使用microblaze作為控制器來進(jìn)行系統(tǒng)調(diào)度的時(shí)候,一般是建議將所有模塊封裝成AXI形式的IP核,這樣好管理,也容易調(diào)試。

2021-04-27 11:17:36 8599

8599

學(xué)習(xí)內(nèi)容 近期設(shè)計(jì)需要用到AXI總線的IP,所以就對應(yīng)常用的IP進(jìn)行簡要的說明,本文主要對AXI互聯(lián)IP進(jìn)行介紹。 基礎(chǔ)架構(gòu)IP 基礎(chǔ)的IP是用于幫助組裝系統(tǒng)的構(gòu)建塊。基礎(chǔ)架構(gòu)IP往往是一個(gè)通用IP

2021-05-11 14:52:55 7870

7870

基于ARM的IEEE802-11bMAC層協(xié)議IP核設(shè)計(jì)(通信電源技術(shù)206期)-文檔為基于ARM的IEEE802-11bMAC層協(xié)議IP核設(shè)計(jì)總結(jié)文檔,是一份不錯(cuò)的參考資料,感興趣的可以下載看看,,,,,,,,,,,,,

2021-09-17 15:11:32 4

4 本文以浮點(diǎn)數(shù)Floating-point IP核將定點(diǎn)數(shù)轉(zhuǎn)換為浮點(diǎn)數(shù)為例,詳細(xì)講解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 13087

13087

AXI——Advanced eXtensible Interface,直譯過來就是先進(jìn)的可擴(kuò)展接口,是由ARM公司提出的,是一種高性能、高帶寬、低延遲的片內(nèi)總線。FPGA工程師會(huì)發(fā)現(xiàn)其大量運(yùn)用于FPGA設(shè)計(jì)中,Vivado中的接口類IP全部都配有AXI接口,可見其重要性。

2022-03-14 14:13:01 7555

7555 本文主要介紹關(guān)于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關(guān)內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測試工程做準(zhǔn)備。

2022-07-03 16:11:05 10565

10565 前面簡單學(xué)習(xí)了關(guān)于GPIO的操作,本次將使用PL 端調(diào)用 AXI GPIO IP 核, 并通過 AXI4-Lite 接口實(shí)現(xiàn) PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 6442

6442 在 AXI 基礎(chǔ)第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學(xué)習(xí)如何導(dǎo)出 IP

2022-08-02 09:43:05 1247

1247

前年,發(fā)表了一篇文章《VCS獨(dú)立仿真Vivado IP核的一些方法總結(jié)》(鏈接在參考資料1),里面簡單講述了使用VCS仿真Vivado IP核時(shí)遇到的一些問題及解決方案,發(fā)表之后經(jīng)過一年多操作上也有些許改進(jìn),所以寫這篇文章補(bǔ)充下。

2022-08-29 14:41:55 4676

4676 用于通過使用Xilinx進(jìn)行的相應(yīng)的開發(fā)來做FPGA實(shí)現(xiàn),它被用作FPGA 設(shè)計(jì)的IP 核之間的一種通信方式。

2022-10-10 09:22:22 11273

11273 今天介紹的是vivado的三種常用IP核:時(shí)鐘倍頻(Clocking Wizard),實(shí)時(shí)仿真(ILA),ROM調(diào)用(Block Memory)。

2023-02-02 10:14:01 5002

5002 上文FPGA IP之AXI4協(xié)議1_協(xié)議構(gòu)架對協(xié)議框架進(jìn)行了說明,本文對AXI4接口的信號(hào)進(jìn)行說明。

2023-05-24 15:05:46 2767

2767

上文FPGA IP之AXI4協(xié)議1_信號(hào)說明把AXI協(xié)議5個(gè)通道的接口信息做了說明,本文對上文說的信號(hào)進(jìn)行詳細(xì)說明。

2023-05-24 15:06:41 2083

2083

Arm? AMBA? 5 AXI 協(xié)議規(guī)范支持高性能、高頻系統(tǒng)設(shè)計(jì),用于管理器和從屬組件之間的通信。AMBA AXI5 協(xié)議擴(kuò)展了前幾代規(guī)范,并增加了幾個(gè)重要的性能和可擴(kuò)展性功能,這些功能使這些協(xié)議與 Arm AMBA CHI 緊密結(jié)合。 讓我們詳細(xì)看一下 AXI5 協(xié)議的一些功能。

2023-05-25 16:01:21 4495

4495 最近,需要使用VCS仿真一個(gè)高速并串轉(zhuǎn)換的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原語。而此前我只使用VCS仿真過Quartus的IP核。

2023-06-06 11:09:56 4032

4032

在仿真Vivado IP核時(shí)分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

AXI4協(xié)議是ARM的AMBA總線協(xié)議重要部分,ARM介紹AXI4總線協(xié)議是一種性能高,帶寬高,延遲低的總線協(xié)議。

2023-06-19 11:17:42 5677

5677

這里做最簡單的設(shè)置,打開Vivado,點(diǎn)開IP Catalog,找到FFT IP核。

2023-06-19 14:38:50 3580

3580

最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線進(jìn)行數(shù)據(jù)和指令傳輸。如果有多個(gè)設(shè)備需要使用AXI協(xié)議對AXI接口的BRAM進(jìn)行讀寫,總線之間該如何進(jìn)行仲裁,通信?

2023-06-19 15:45:14 14453

14453

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實(shí)現(xiàn)一個(gè)簡單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯(lián)結(jié)構(gòu)上,通過 ZYNQ 主機(jī)控制,后面對 Xilinx 提供的整個(gè) AXI4-Lite 源碼進(jìn)行分析。

2023-06-25 16:31:25 4882

4882

Vivado IP核提供了強(qiáng)大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7270

7270

外部存儲(chǔ)器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線用于

2023-08-31 11:25:41 11848

11848

在給Vivado中的一些IP核進(jìn)行配置的時(shí)候,發(fā)現(xiàn)有Shared Logic這一項(xiàng),這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

Xilinx公司的FPGA中有著很多的有用且對整個(gè)工程很有益處的IP核,比如數(shù)學(xué)類的IP核,數(shù)字信號(hào)處理使用的IP核,以及存儲(chǔ)類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 AMBA AXI4(高級(jí)可擴(kuò)展接口 4)是 ARM 推出的第四代 AMBA 接口規(guī)范。AMD Vivado Design Suite 2014 和 ISE Design Suite 14 憑借半導(dǎo)體產(chǎn)業(yè)首個(gè)符合 AXI4 標(biāo)準(zhǔn)的即插即用型 IP 進(jìn)一步擴(kuò)展了 AMD 平臺(tái)設(shè)計(jì)方法。

2024-10-28 10:46:42 1383

1383

10GBe/40GBe UDP 協(xié)議棧 IP 核、10GbE TCP/IP 協(xié)議棧 IP 核和 NVMe AXI IP 核。 ? ALINX 發(fā)布的 10GbE TCP/IP 協(xié)議棧 IP 核,能夠?qū)崿F(xiàn)

2024-10-30 17:39:43 1459

1459

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論