本章的實(shí)驗(yàn)任務(wù)是在 PL 端自定義一個(gè) AXI4 接口的 IP 核,通過(guò) AXI_HP 接口對(duì) PS 端 DDR3 進(jìn)行讀寫(xiě)測(cè)試,讀寫(xiě)的內(nèi)存大小是 4K 字節(jié)。

2025-11-24 09:19:42 3467

3467

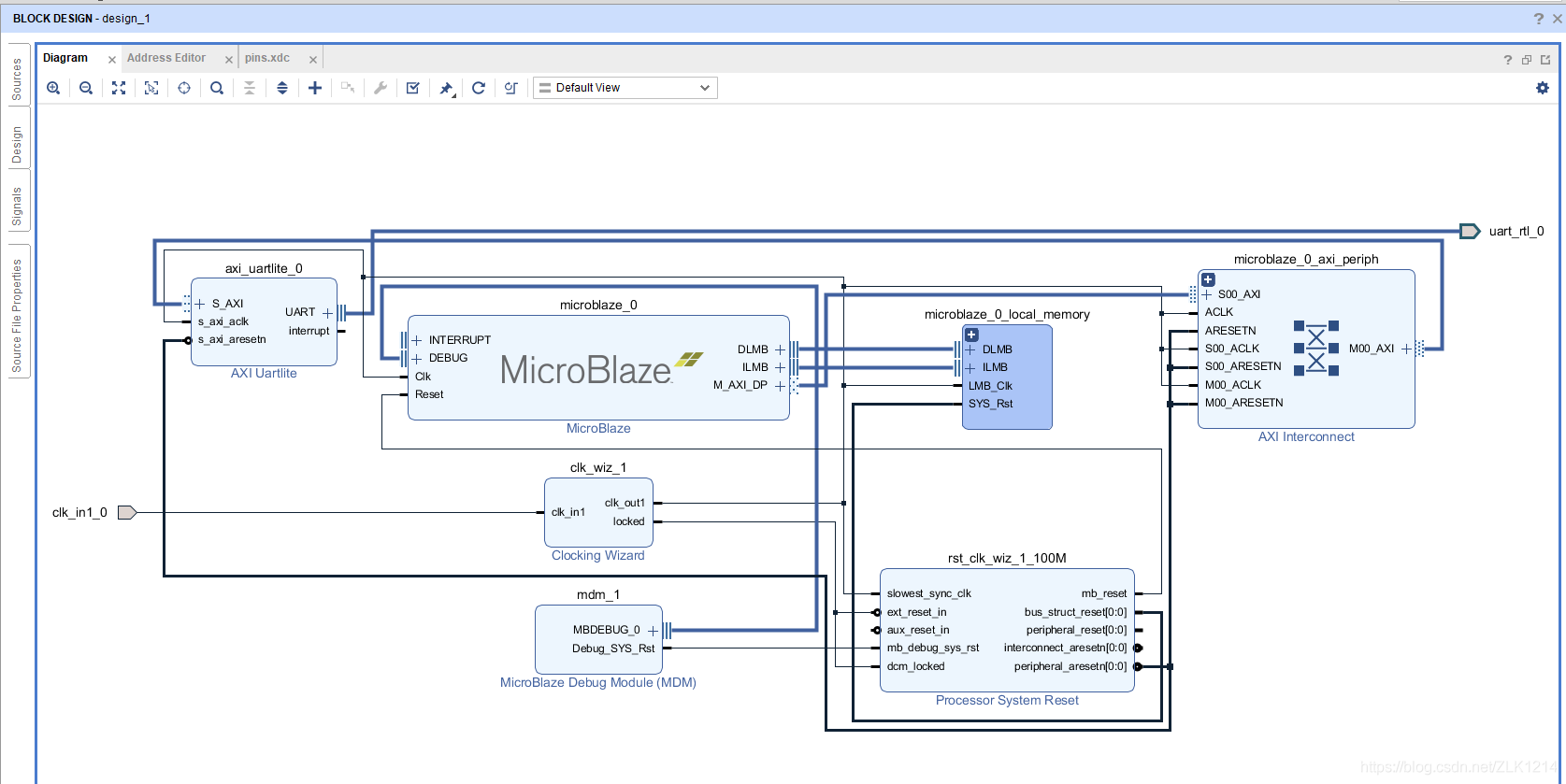

microblaze和jtag-to-axi(jtag2axi)雖然也提供了訪(fǎng)問(wèn)axi總線(xiàn)的能力,但是依賴(lài)于xilinx平臺(tái)。而uart-to-axi(uart2axi4)橋接器并不依賴(lài)任何平臺(tái)

2025-12-02 10:05:43 1842

1842

FPGA+ARM是ZYNQ的特點(diǎn),那么PL部分怎么和ARM通信呢,依靠的就是AXI總線(xiàn)。這個(gè)實(shí)驗(yàn)是創(chuàng)建一個(gè)基于AXI總線(xiàn)的GPIO IP,利用PL的資源來(lái)擴(kuò)充GPIO資源。通過(guò)這個(gè)實(shí)驗(yàn)迅速入門(mén)

2020-12-25 14:07:02 6724

6724

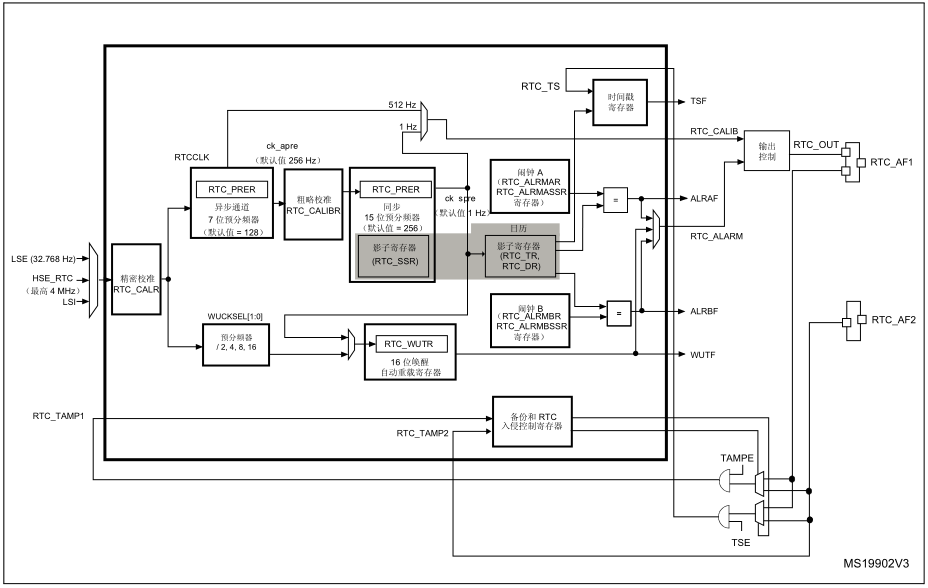

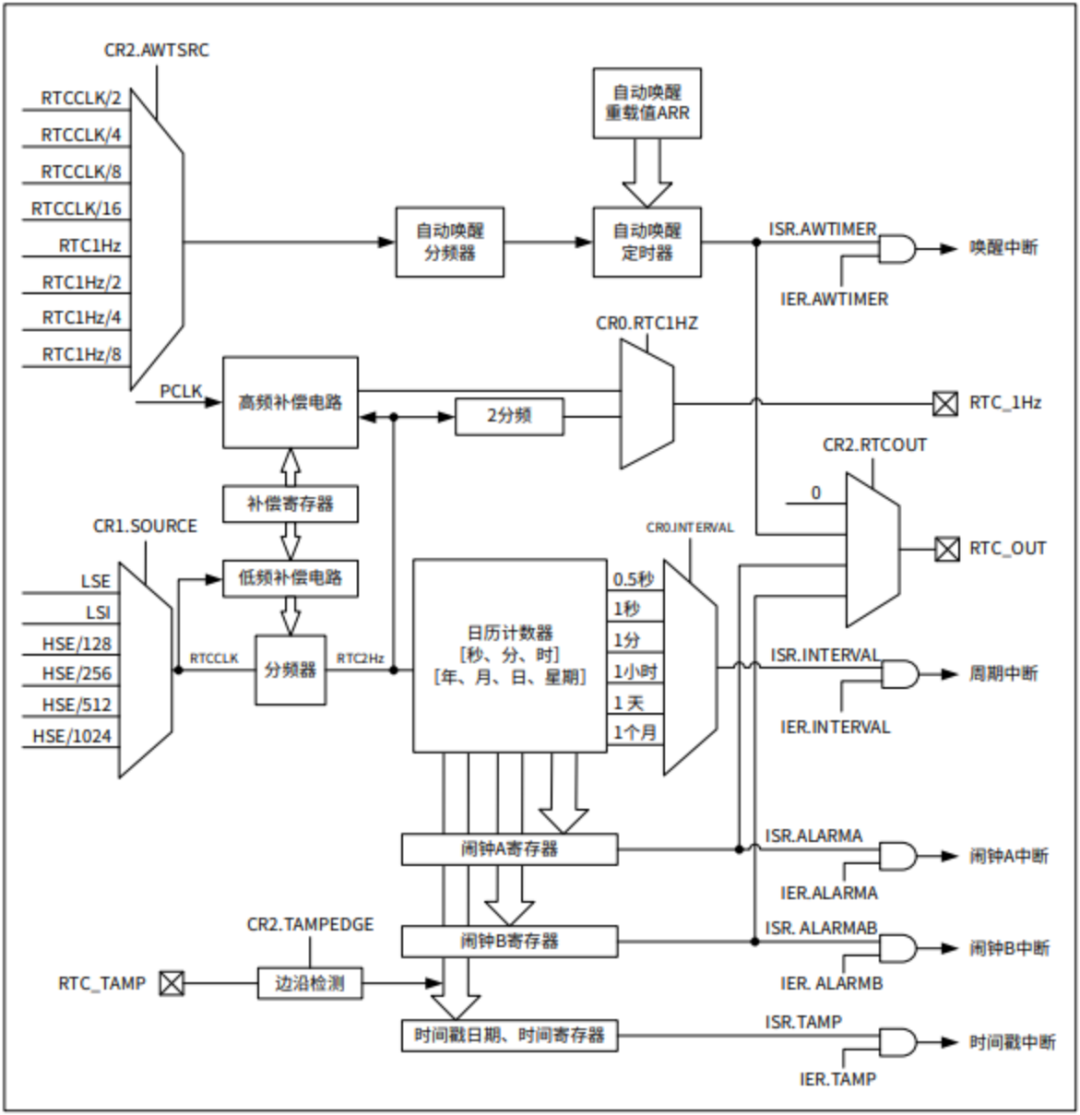

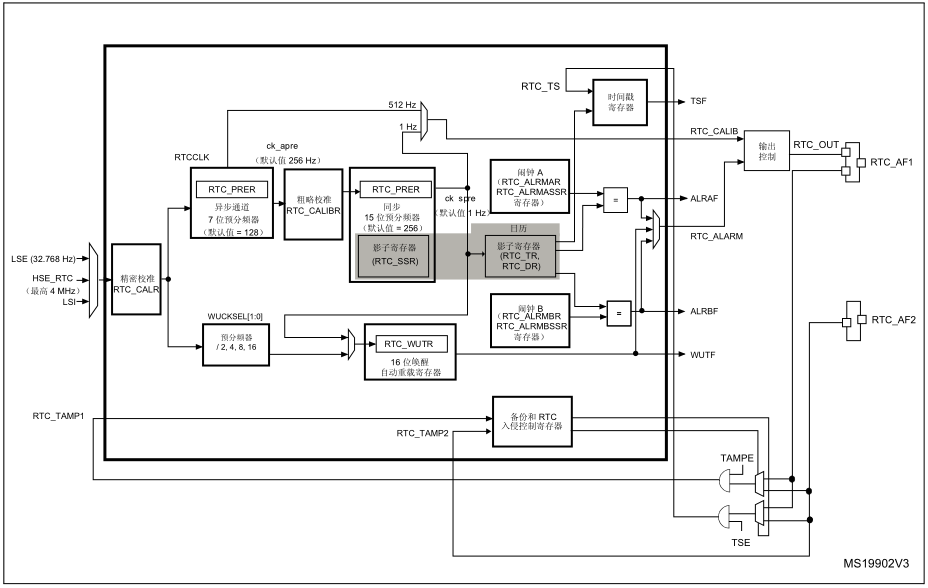

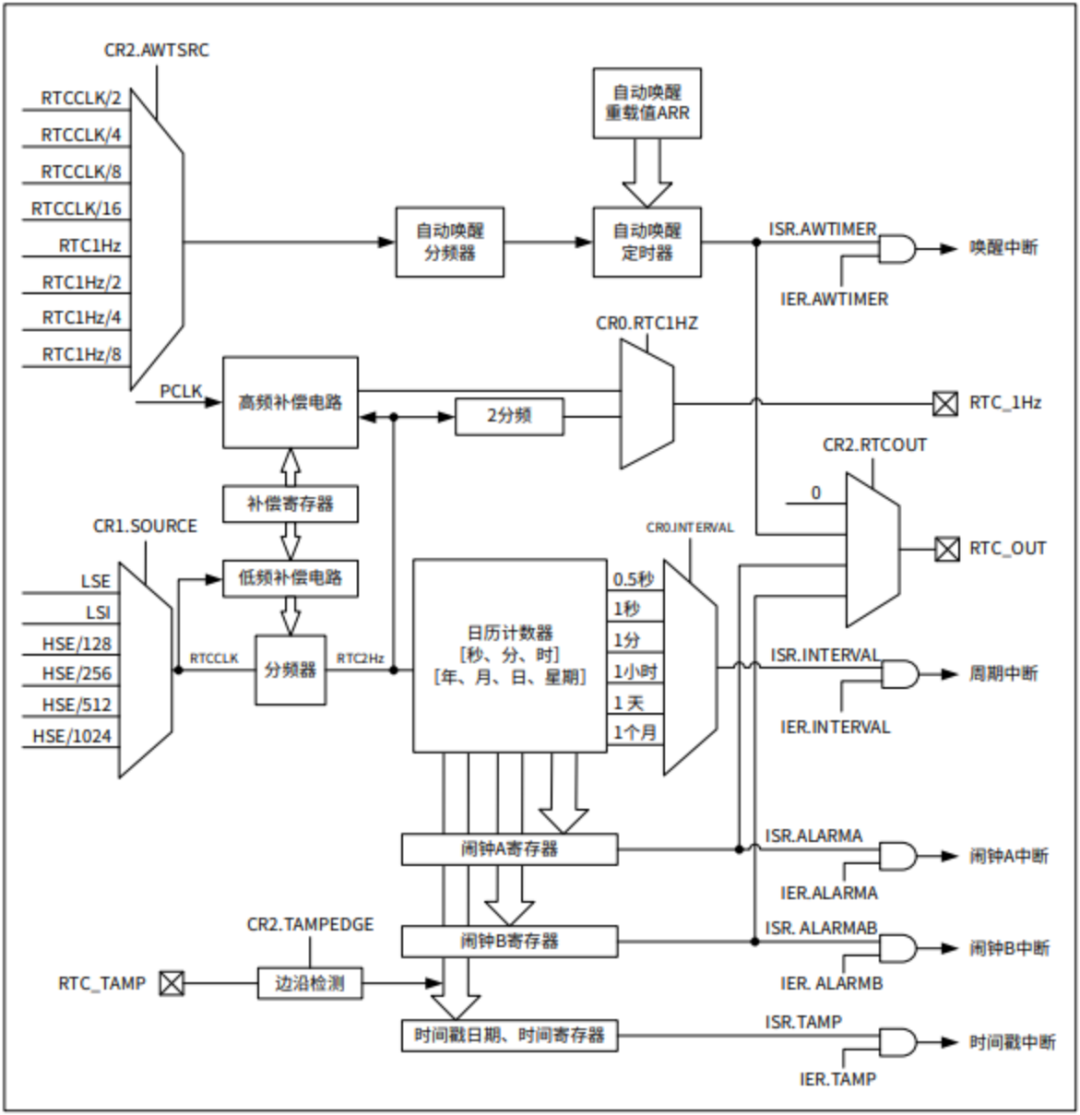

STM32處理器內(nèi)部集成了實(shí)時(shí)時(shí)鐘控制器(RTC),因此在實(shí)現(xiàn)實(shí)時(shí)時(shí)鐘功能時(shí),無(wú)須外擴(kuò)時(shí)鐘芯片即可構(gòu)建實(shí)時(shí)時(shí)鐘系統(tǒng)。

2023-07-22 15:41:20 6243

6243

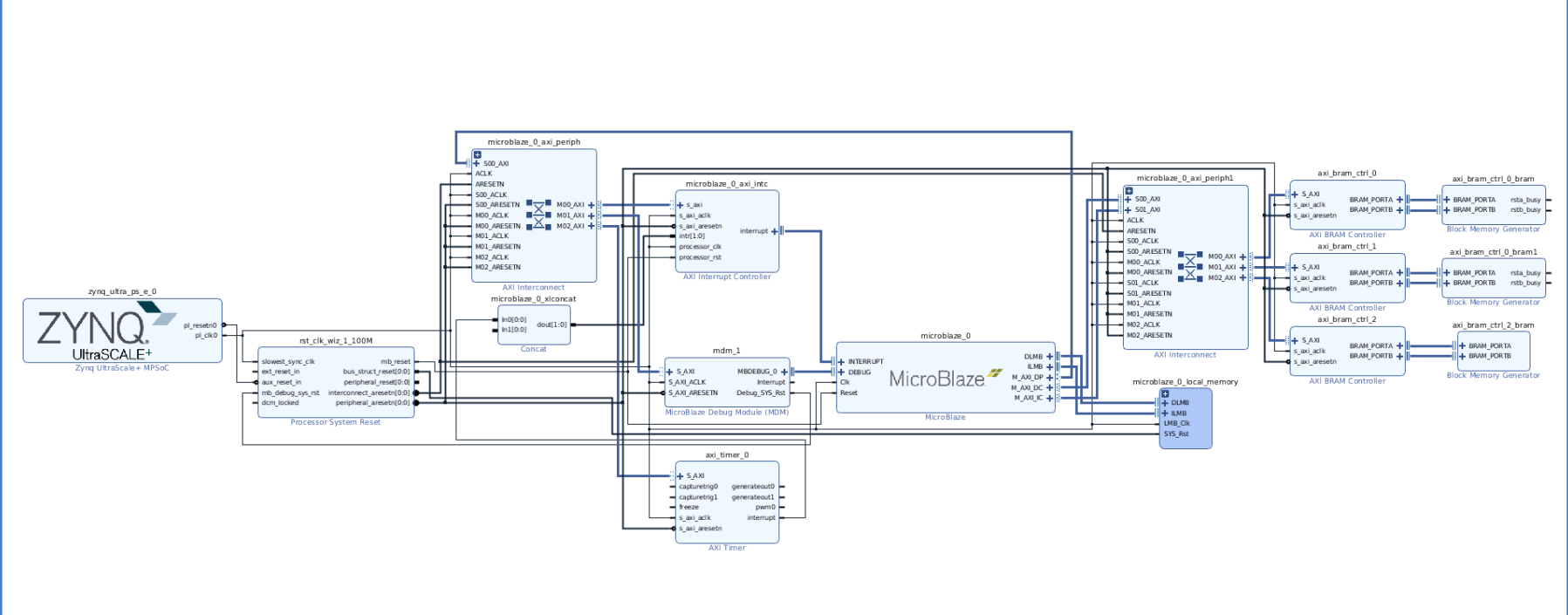

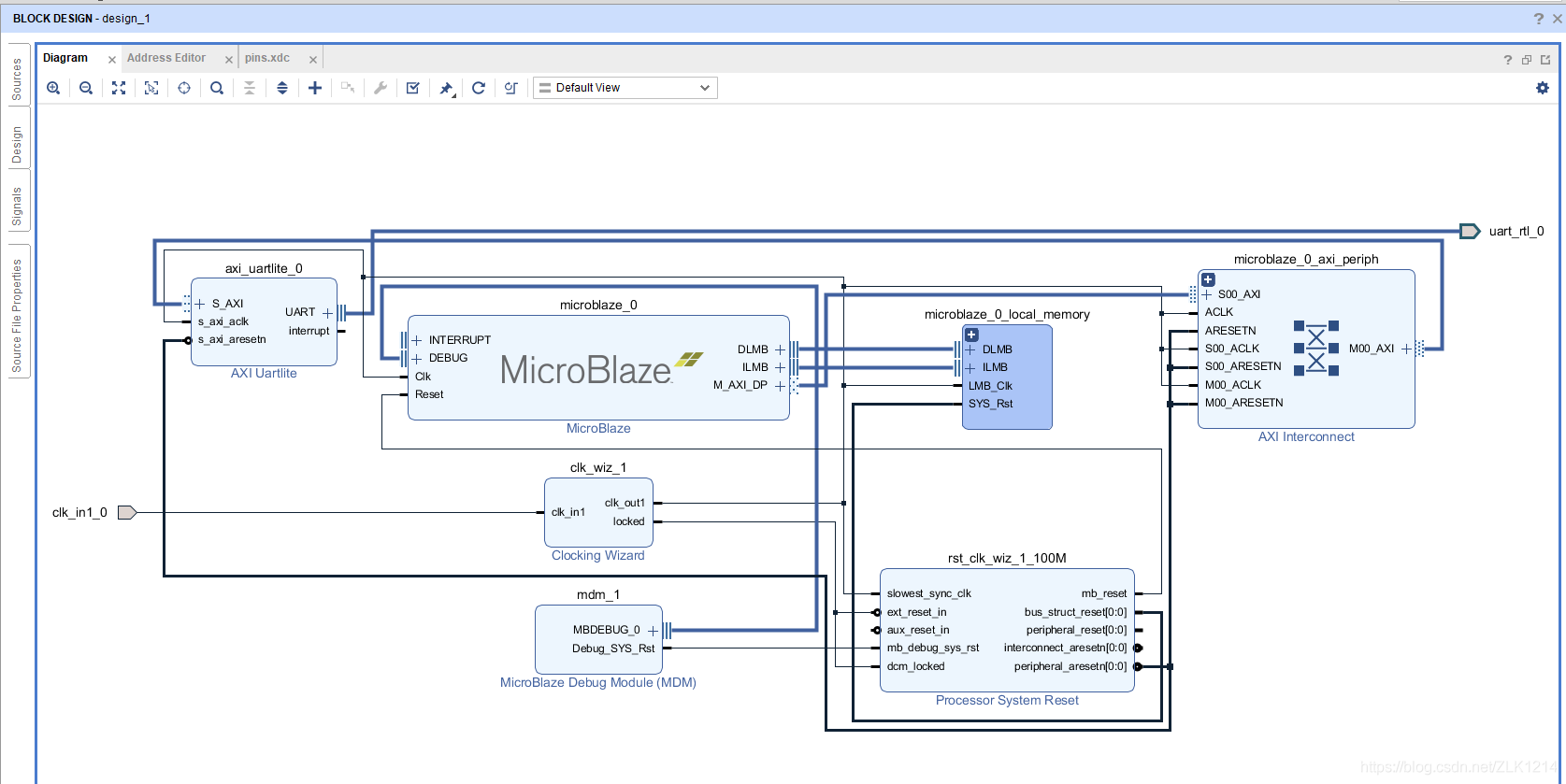

本系統(tǒng)中,Basys3的MicroBlaze模塊調(diào)用基于AXI協(xié)議的UART IP核,通過(guò)AXI總線(xiàn)實(shí)現(xiàn)MicroBlaze-UART之間的通信,完成串口打印。

2023-08-02 09:32:06 2459

2459

Video In to AXI4-Stream IP核用于將視頻源(帶有同步信號(hào)的時(shí)鐘并行視頻數(shù)據(jù),即同步sync或消隱blank信號(hào)或者而后者皆有)轉(zhuǎn)換成AXI4-Stream接口形式,實(shí)現(xiàn)了接口轉(zhuǎn)換。該IP還可使用VTC核,VTC在視頻輸入和視頻處理之間起橋梁作用。

2025-04-03 09:28:14 2418

2418

形式發(fā)送到顯示緩存中; 在AXI系統(tǒng)總線(xiàn)下,搭建軟核的關(guān)鍵部分步驟如下;1、添加GPIO外設(shè); 2、單擊YES;添加IP; 3、 將channel1 的位寬設(shè)置為2;其它默認(rèn);單擊OK; 4

2014-04-10 09:30:17

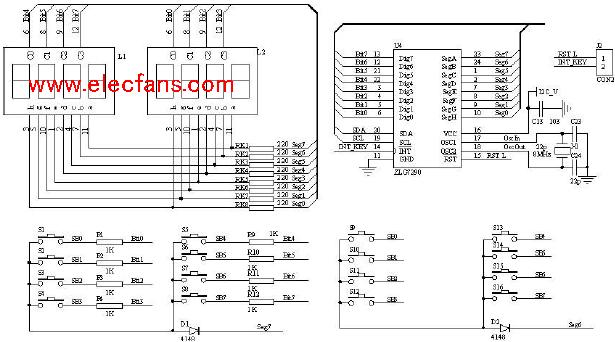

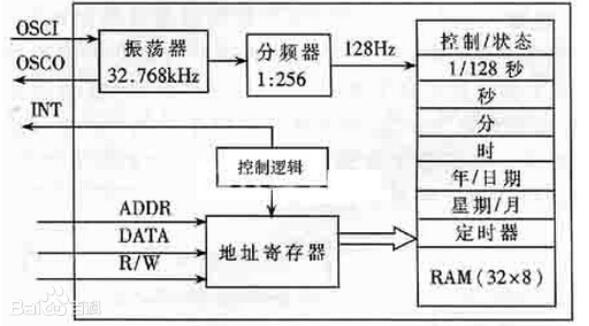

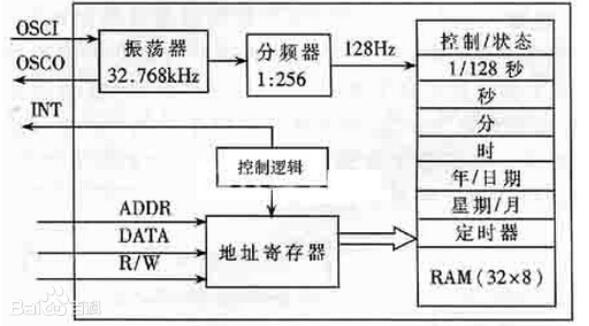

藍(lán)橋杯單片機(jī)比賽系列5實(shí)時(shí)時(shí)鐘RTCRTC原理相關(guān)電路時(shí)鐘寄存器代碼解釋修改代碼自寫(xiě)代碼實(shí)現(xiàn)代碼RTC原理相關(guān)電路實(shí)時(shí)時(shí)鐘芯片采用DS1302,需要三個(gè)引腳和單片機(jī)相連。DS1302有自己的指令協(xié)議

2022-01-17 07:40:19

定義:實(shí)時(shí)時(shí)鐘的縮寫(xiě)是RTC(Real Time Clock).實(shí)時(shí)時(shí)鐘是一個(gè)獨(dú)立的定時(shí)器。RTC模塊擁有一組連續(xù)計(jì)數(shù)的計(jì)數(shù)哭奮,在相應(yīng)軟件配置下,可提供時(shí)鐘日歷的功能。修改計(jì)數(shù)器的值可以重新設(shè)置系統(tǒng)當(dāng)前的時(shí)間和日期。...

2021-08-09 06:18:01

想要設(shè)計(jì)一款實(shí)時(shí)時(shí)鐘電路設(shè)計(jì),有沒(méi)有相關(guān)的案例參考啊?

2021-04-07 06:04:24

實(shí)時(shí)時(shí)鐘(RTC)是什么?實(shí)時(shí)時(shí)鐘RTC的寄存器有哪些?

2021-10-09 07:08:15

IP核均采用AXI總線(xiàn)接口,已經(jīng)不再支持native接口。故做除法運(yùn)算的重點(diǎn)從設(shè)計(jì)算法電路轉(zhuǎn)變成了調(diào)用AXI總線(xiàn)IP核以及HDL中有符號(hào)數(shù)的表示問(wèn)題,極大降低了開(kāi)發(fā)難度。以下就上述兩個(gè)方面進(jìn)行探討

2018-08-13 09:27:32

FSL總線(xiàn)IP核及其在MicroBlaze系統(tǒng)中的應(yīng)用

2015-01-18 21:01:20

的fifo接口),用戶(hù)只要操作fifo接口,無(wú)需關(guān)心PCIE的內(nèi)部驅(qū)動(dòng)。為了便于讀者更加明白,可以深入了解PCIE,我們將會(huì)制作一個(gè)PCIE的連載系列。今天,首先說(shuō)一下自定義AXI4的IP核,至于AXI

2019-12-13 17:10:42

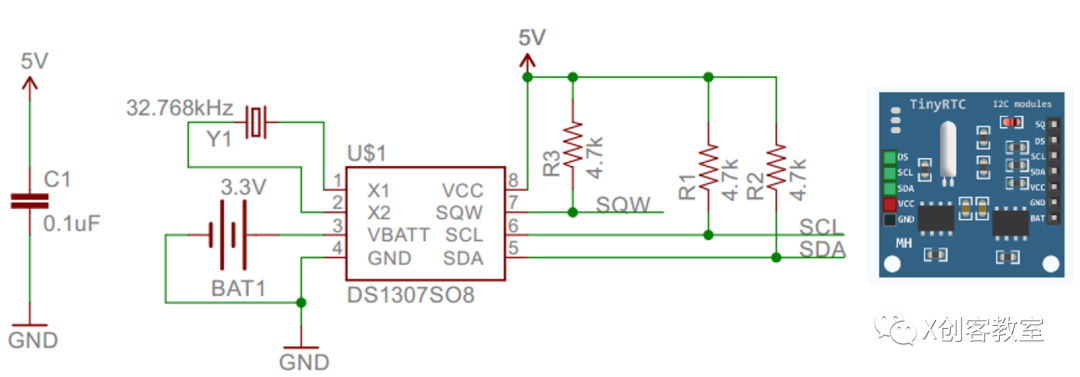

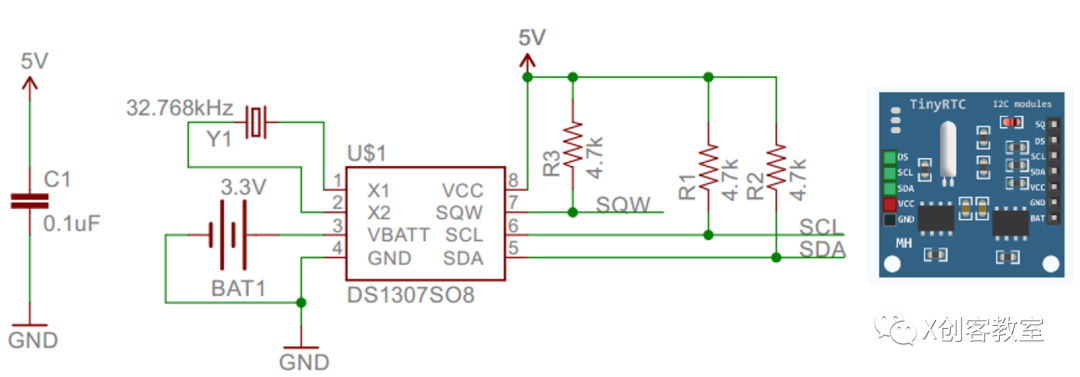

實(shí)時(shí)時(shí)鐘模塊(I2C總線(xiàn))

2023-03-24 14:48:54

RTC實(shí)時(shí)時(shí)鐘怎么使用?cubemx中如何配置RTC?如何在keil中編寫(xiě)程序?

2022-01-18 07:33:54

實(shí)時(shí)時(shí)鐘的縮寫(xiě)是RTC(Real_Time Clock)實(shí)時(shí)時(shí)鐘是一個(gè)獨(dú)立的定時(shí)器。RTC模塊擁有一組連續(xù)計(jì)數(shù)的計(jì)數(shù)器,在相應(yīng)軟件配置下,可提供時(shí)鐘日歷的功能。修改計(jì)數(shù)器的值可以重新設(shè)置系統(tǒng)當(dāng)前

2022-01-26 07:53:26

本帖最后由 mr.pengyongche 于 2013-4-30 03:14 編輯

實(shí)時(shí)時(shí)鐘與系統(tǒng)時(shí)鐘:系統(tǒng)時(shí)鐘:簡(jiǎn)單的說(shuō),就是芯片系統(tǒng)內(nèi)部的時(shí)鐘,程序運(yùn)行的速度是由它來(lái)決定的。RTC:實(shí)時(shí)時(shí)鐘, 如果供電,它會(huì)按照自己的精確等級(jí)運(yùn)行的,主要用來(lái)做日期時(shí)間的顯示用綜上:

2012-12-15 20:25:23

RTC實(shí)時(shí)時(shí)鐘1. RTC實(shí)時(shí)時(shí)鐘簡(jiǎn)介2. 硬件設(shè)計(jì)3. 軟件設(shè)計(jì)3.1 STM32CubeMX設(shè)置3.2 MDK-ARM編程4. 下載驗(yàn)證

2021-08-18 06:55:38

VDMA端口信號(hào)

S_AXI_LITE:PS端可以通過(guò)AXI_LITE協(xié)議對(duì)IP核進(jìn)行控制;

S_AXIS_S2MM:視頻流(AXI STREAM)輸入到IP核的FIFO中

2025-10-28 06:14:54

文件名大小更新時(shí)間WS2812實(shí)時(shí)時(shí)鐘程序\APP\24Cxx\24cxx.c54102019-04-05WS2812實(shí)時(shí)時(shí)鐘程序\APP\24Cxx

2021-07-13 07:33:57

ZYNQ自定義AXI總線(xiàn)IP應(yīng)用——PWM實(shí)現(xiàn)呼吸燈效果一、前言 在實(shí)時(shí)性要求較高的場(chǎng)合中,CPU軟件執(zhí)行的方式顯然不能滿(mǎn)足需求,這時(shí)需要硬件邏輯實(shí)現(xiàn)部分功能。要想使自定義IP核被CPU訪(fǎng)問(wèn)

2020-04-23 11:16:13

stm實(shí)時(shí)時(shí)鐘在串口調(diào)試中,為啥1.2能輸入,3和4就不行了??急。。。。。

2014-04-26 19:34:46

是Vivado中十分常用的自定義IP核,使用AXI接口的IP,能夠方便的連接到軟核(MicroBlaze)或硬核(Zynq)的總線(xiàn)上,方便軟核或硬核對(duì)其進(jìn)行讀寫(xiě)操作。本設(shè)計(jì)的重點(diǎn)是使用FPGA邏輯設(shè)計(jì)獨(dú)立

2016-12-16 11:00:37

什么是實(shí)時(shí)時(shí)鐘(RTC)?實(shí)時(shí)時(shí)鐘(RTC)的基本功能是什么?實(shí)時(shí)時(shí)鐘(RTC)晶體誤差的主要來(lái)源有哪些?如何更改RTC的時(shí)間?

2021-07-19 08:44:30

基于FPGA的實(shí)時(shí)時(shí)鐘設(shè)計(jì)

2017-12-06 20:40:17

實(shí)時(shí)時(shí)鐘RTC是什么?如何去使用STM32的實(shí)時(shí)時(shí)鐘RTC呢?有哪些注意事項(xiàng)?

2021-11-22 08:05:18

有人知道為什么MIG IP核中的AXI協(xié)議。為什么沒(méi)有AXI_WID這個(gè)信號(hào)呢。

2018-04-13 09:22:30

,ar)共用一組信號(hào)的接口(arw,w,b,r)。關(guān)于總線(xiàn)互聯(lián)的設(shè)計(jì)凡是設(shè)計(jì)中用到Axi4總線(xiàn)的設(shè)計(jì)總離不開(kāi)總線(xiàn)互聯(lián)。在Xilinx FPGA使用中,VIvado針對(duì)Axi4總線(xiàn)提供了豐富的IP,對(duì)于

2022-08-02 14:28:46

microblaze通過(guò)串口讀寫(xiě)FPGA內(nèi)部axi4總線(xiàn)上的寄存器

2020-12-23 06:16:11

MSM6242B 直接總線(xiàn)連接的CMOS實(shí)時(shí)時(shí)鐘,日歷的典型應(yīng)用和應(yīng)用筆記

2009-05-19 16:57:48 18

18 X12XX系列實(shí)時(shí)時(shí)鐘的特點(diǎn)及應(yīng)用:

2009-05-22 13:25:24 18

18 RX8025SA 32.7689KHz ±5 ppm 時(shí)鐘模塊是愛(ài)普生的一款額定頻率32.7689KHz,接口為I2C,月偏差為±13 s的實(shí)時(shí)時(shí)鐘模塊,SOP-14腳封裝實(shí)時(shí)時(shí)鐘模塊,14腳貼片

2022-12-07 09:40:21

介紹了基于MicroBlaze 軟核處理器的可編程片上系統(tǒng)結(jié)構(gòu)。提出了一種LCD 控制器IP 核的設(shè)計(jì)方法。該控制器具有片上外設(shè)總線(xiàn)接口,和其它標(biāo)準(zhǔn)IP 核一起組成以MicroBlaze 為核心的片上系

2009-08-31 10:58:53 11

11 FM31 系列,F(xiàn)M3808,FM30C256 集成了處理器外圍器件,它集成了FRAM 非易失性存儲(chǔ)器和實(shí)時(shí)時(shí)鐘于一體。實(shí)時(shí)時(shí)鐘在VDD 掉電以后自動(dòng)切換到后備電源。在使用后備電源的情況下,實(shí)

2010-03-04 10:44:07 79

79 HT49 MCU RTC(實(shí)時(shí)時(shí)鐘)的使用介紹文件編碼:HA0024s本文主要介紹HT49 系列單片機(jī)實(shí)時(shí)時(shí)鐘的使用方法。簡(jiǎn)單介紹HT49R50A-1 系列提供了實(shí)時(shí)時(shí)鐘,主要用于產(chǎn)生周期性的中

2010-03-26 08:37:34 12

12 實(shí)時(shí)時(shí)鐘模DS1302程序列子 /*********************************************************************//* 實(shí)時(shí)時(shí)鐘模塊 時(shí)鐘芯片型號(hào):DS1302 *//*//*****************

2010-07-08 16:26:07 143

143 本文詳述了一種基于AMBA總線(xiàn)接口的IIC總線(xiàn)控制器IP核設(shè)計(jì),給出了該IP核的系統(tǒng)結(jié)構(gòu)以及各個(gè)子模塊的詳細(xì)設(shè)計(jì)方法,并對(duì)該IP核進(jìn)行了功能仿真、FPGA原型驗(yàn)證,可測(cè)性設(shè)計(jì)以

2010-07-17 16:20:22 21

21 1 RTC結(jié)構(gòu)特點(diǎn)實(shí)時(shí)時(shí)鐘的基本功能是保持跟蹤時(shí)間和日

2006-04-17 20:04:26 2094

2094

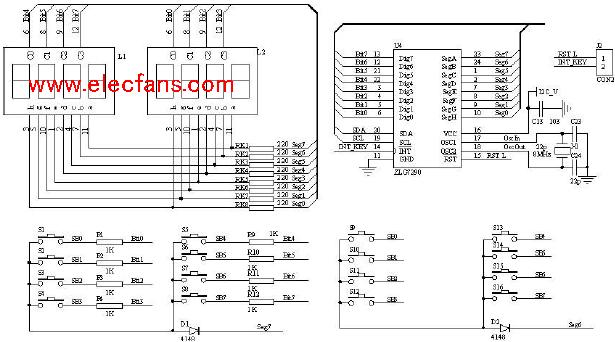

I2C 總線(xiàn)實(shí)驗(yàn)(實(shí)時(shí)時(shí)鐘、EEPROM 和ZLG7290 的實(shí)驗(yàn))

一. 實(shí)驗(yàn)?zāi)康募由钣脩?hù)對(duì)I2C 總線(xiàn)的理解,熟悉I2C 器件的使用

2008-09-22 16:58:40 4493

4493

1. 概述MM58167B作為總線(xiàn)型微處理系統(tǒng)中的實(shí)時(shí)時(shí)鐘源,其內(nèi)部包括一個(gè)可尋址的實(shí)時(shí)計(jì)數(shù)器、56 bit片內(nèi)RAM和

2010-11-11 17:12:06 1144

1144

文章采用TOP-DOWN 的方法設(shè)計(jì)了 AMBA 總線(xiàn)IP 核!它包括AHB 和APB兩個(gè)子IP 核 所有AMBA結(jié)構(gòu)模塊均實(shí)現(xiàn)了RTL級(jí)建模

2011-07-25 18:10:52 93

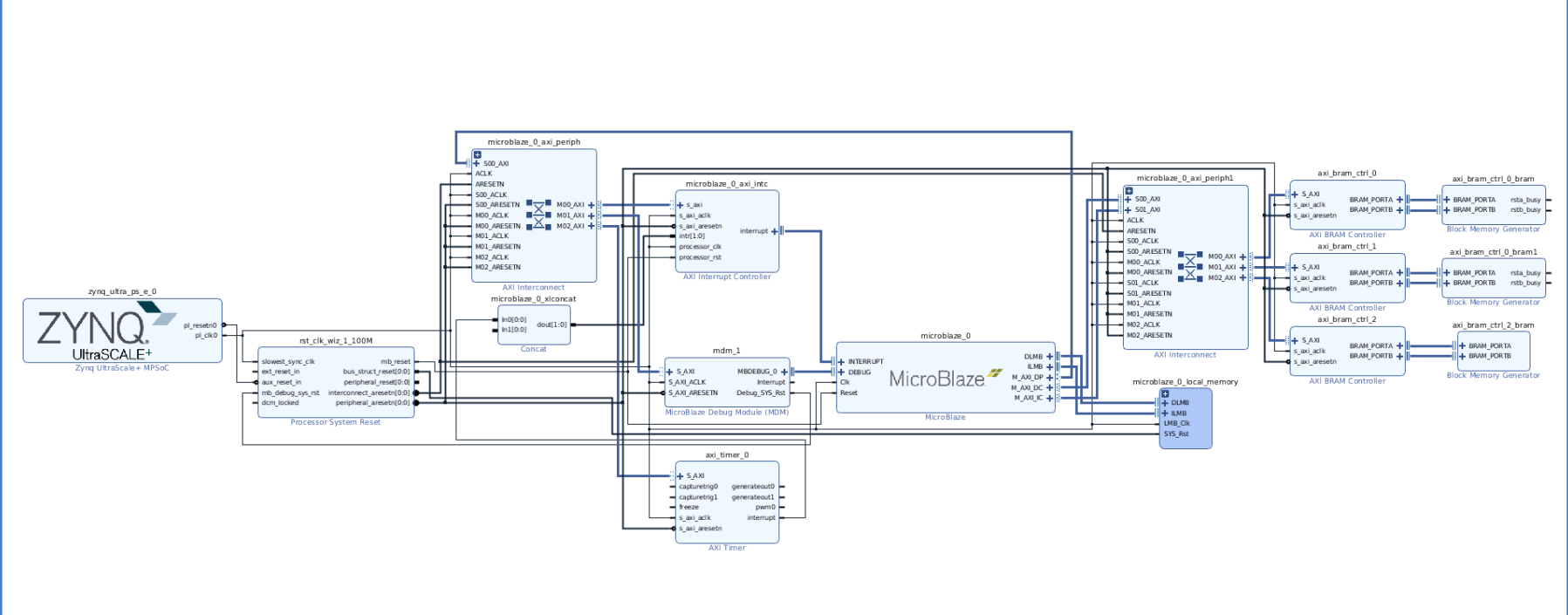

93 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實(shí)現(xiàn)基于AXI總線(xiàn)的雙核嵌入式系統(tǒng)設(shè)計(jì)以及共享實(shí)現(xiàn)LED燈的時(shí)控.

2012-03-09 14:17:01 91

91 的 RX-8130CE是EPSON公司于近日新推出的一款嵌入32.768kHz晶振單元并擁有I2C總線(xiàn)接口的實(shí)時(shí)時(shí)鐘模塊。

2015-10-14 09:10:21 4485

4485 分析RX-8025實(shí)時(shí)時(shí)鐘的工作原理和Linux的I2C總線(xiàn)驅(qū)動(dòng)程序,構(gòu)建了高速公路視頻監(jiān)控系統(tǒng)下基于I2C實(shí)時(shí)時(shí)鐘控制系統(tǒng),完成了基于ARM和Linux的I2C驅(qū)動(dòng)程序設(shè)計(jì)、I2C應(yīng)用程序

2015-12-28 09:52:34 17

17 ARM嵌入式應(yīng)用程序架構(gòu)設(shè)計(jì)實(shí)例精講--ARM基礎(chǔ)應(yīng)用實(shí)驗(yàn)03實(shí)時(shí)時(shí)鐘

2016-07-08 11:08:19 0

0 電子專(zhuān)業(yè)單片機(jī)相關(guān)知識(shí)學(xué)習(xí)教材資料——ARM基礎(chǔ)應(yīng)用實(shí)驗(yàn)03實(shí)時(shí)時(shí)鐘

2016-09-13 17:23:28 0

0 microblaze基本結(jié)構(gòu) 3.實(shí)現(xiàn)microblaze調(diào)用uart模塊,完成串口打印功能。 實(shí)驗(yàn)原理:本系統(tǒng)中,Basys3的Microblaze模塊調(diào)用基于AXI協(xié)議的uart IP核,通過(guò)

2017-02-08 15:05:36 1318

1318

本文先總結(jié)不同AXI IP核的實(shí)現(xiàn)的方法,性能的對(duì)比,性能差異的分析,可能改進(jìn)的方面。使用的硬件平臺(tái)是Zedboard。 不同的AXI總線(xiàn)卷積加速模塊的概況 這次實(shí)現(xiàn)并逐漸優(yōu)化了三個(gè)版本的卷積加速模塊,先簡(jiǎn)要描述各個(gè)版本的主要內(nèi)容。

2018-06-29 14:34:00 8923

8923

基于實(shí)時(shí)時(shí)鐘模塊 時(shí)鐘芯片DS1302

2017-10-16 11:35:07 40

40 AXI總線(xiàn)的MicroBlaze雙核SoPC系統(tǒng)設(shè)計(jì)

2017-10-31 08:54:44 8

8 基于AXI4Stream總線(xiàn)協(xié)議,在Xilinx公司提供的FPGA上實(shí)現(xiàn)了一個(gè)具有缺陷像素校正、色彩濾波陣列插值、圖像降噪實(shí)時(shí)圖像采集與顯示功能的視頻系統(tǒng)。AXI4Stream總線(xiàn)協(xié)議由ARM公司

2017-11-17 08:58:01 5344

5344 1、在工作流導(dǎo)向面板中的IP Integrator中,點(diǎn)擊Create Block Design。(表示你要開(kāi)始構(gòu)建帶有IP核的框圖了)

2、Add IP,找到MicroBlaze,添加到

2017-11-17 11:16:00 19749

19749 本文包含兩部分內(nèi)容:1)AXI接口簡(jiǎn)介;2)AXI IP核的創(chuàng)建流程及讀寫(xiě)邏輯分析。 1AXI簡(jiǎn)介(本部分內(nèi)容參考官網(wǎng)資料翻譯) 自定義IP核是Zynq學(xué)習(xí)與開(kāi)發(fā)中的難點(diǎn),AXI IP核又是十分常用

2018-06-29 09:33:00 17729

17729

本文主要介紹了時(shí)鐘芯片有哪些、時(shí)鐘芯片結(jié)構(gòu)與工作原理,其次介紹了時(shí)鐘芯片布線(xiàn)與時(shí)鐘芯片的作用,最后介紹了時(shí)鐘芯片選型以及愛(ài)普生實(shí)時(shí)時(shí)鐘芯片規(guī)格書(shū)與選型手冊(cè)。

2018-01-29 08:44:20 41781

41781

IP核的全稱(chēng)是: AXI4-STREAM FIFO 設(shè)置注意事項(xiàng):一定要選擇異步時(shí)鐘,也就是雙時(shí)鐘,如下: 關(guān)于其他配置: TLAST 一般要選擇的,作為邊界界定。其他可以不選。深度不必太深,因?yàn)橹黄鸬酱┰?b class="flag-6" style="color: red">時(shí)鐘區(qū)域的作用。

2018-03-26 14:40:00 5859

5859

對(duì)于一些測(cè)控系統(tǒng)或者手持式設(shè)備,經(jīng)常需要顯示以及設(shè)定時(shí)間。目前,市場(chǎng)上有多種實(shí)時(shí)時(shí)鐘芯片提供了這類(lèi)功能。這種可編程的實(shí)時(shí)時(shí)鐘芯片內(nèi)置了可編程的日歷時(shí)鐘以及一定的RAM存儲(chǔ)器,用于設(shè)定以及保存時(shí)間

2018-03-16 15:31:38 14

14 本文首先闡述了rtc實(shí)時(shí)時(shí)鐘和單片機(jī)時(shí)鐘的區(qū)別,其次介紹了單片機(jī)中時(shí)鐘概念與單片機(jī)內(nèi)外部時(shí)鐘方式,最后介紹了實(shí)時(shí)時(shí)鐘作用與硬件結(jié)構(gòu)。

2018-05-14 15:48:10 62467

62467 本文檔的主要內(nèi)容詳細(xì)介紹的是microblaze IP核使用說(shuō)明資料合集免費(fèi)下載包括了(微啟動(dòng)快速啟動(dòng)指南)(PG116微火焰MCS)(UG940 VVADO教程嵌入式設(shè)計(jì))(用于成本敏感應(yīng)用程序的WP499微閃存)(XAPP1180)(自述文件)

2018-07-20 08:00:00 48

48 實(shí)時(shí)時(shí)鐘的縮寫(xiě)是RTC(Real_Time Clock)。RTC 是集成電路,通常稱(chēng)為時(shí)鐘芯片。

實(shí)時(shí)時(shí)鐘芯片是日常生活中應(yīng)用最為廣泛的消費(fèi)類(lèi)電子產(chǎn)品之一。它為人們提供精確的實(shí)時(shí)時(shí)間,或者為電子系

2018-08-24 08:00:00 13

13 Xilinx公司的MicroBlaze 32位軟處理器核是支持CoreConnect總線(xiàn)的標(biāo)準(zhǔn)外設(shè)集合。MicroBlaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,非常適合設(shè)計(jì)針對(duì)網(wǎng)絡(luò)、電信、數(shù)據(jù)通信和消費(fèi)市場(chǎng)的復(fù)雜嵌入式系統(tǒng)。

2018-12-05 17:18:05 13

13 自定義sobel濾波IP核 IP接口遵守AXI Stream協(xié)議

2019-08-06 06:04:00 4566

4566 AXI-Lite或AXI4轉(zhuǎn)接。PS與PL之間的物理接口有9個(gè),包括4個(gè)AXI-GP接口和4個(gè)AXI-HP接口、1個(gè)AXI-ACP接口。 Xilinx提供的從AXI到AXI-Stream轉(zhuǎn)換的IP核有:AXI-DMA,AXI-Datam

2020-11-02 11:27:51 5032

5032

實(shí)時(shí)時(shí)鐘的縮寫(xiě)是RTC(Real_Time Clock)。RTC 是集成電路,通常稱(chēng)為時(shí)鐘芯片。

2020-11-16 17:10:14 8192

8192

本文介紹了AMBA 3.0 AXI的結(jié)構(gòu)和特點(diǎn),分析了新的AMBA 3.0 AXI協(xié)議相對(duì)于AMBA 2. 0的優(yōu)點(diǎn)。它將革新未來(lái)高性能SOC總線(xiàn)互連技術(shù),其特點(diǎn)使它更加適合未來(lái)的高性能、低延遲

2021-04-12 15:47:39 28

28 在一個(gè)項(xiàng)目中,當(dāng)你使用microblaze作為控制器來(lái)進(jìn)行系統(tǒng)調(diào)度的時(shí)候,一般是建議將所有模塊封裝成AXI形式的IP核,這樣好管理,也容易調(diào)試。

2021-04-27 11:17:36 8599

8599

學(xué)習(xí)內(nèi)容 近期設(shè)計(jì)需要用到AXI總線(xiàn)的IP,所以就對(duì)應(yīng)常用的IP進(jìn)行簡(jiǎn)要的說(shuō)明,本文主要對(duì)AXI互聯(lián)IP進(jìn)行介紹。 基礎(chǔ)架構(gòu)IP 基礎(chǔ)的IP是用于幫助組裝系統(tǒng)的構(gòu)建塊。基礎(chǔ)架構(gòu)IP往往是一個(gè)通用IP

2021-05-11 14:52:55 7870

7870

現(xiàn)在流行的串行時(shí)鐘電路很多,如DS1302、 DS1307、PCF8485等。這些電路的接口簡(jiǎn)單、價(jià)格低廉、使用方便,被廣泛地采用。本文介紹的實(shí)時(shí)時(shí)鐘電路DS1302是DALLAS公司的一種具有涓細(xì)

2021-05-18 09:34:23 6929

6929 一、RTC實(shí)時(shí)時(shí)鐘特征與原理 查看STM32中文手冊(cè) 16 實(shí)時(shí)時(shí)鐘(RTC)(308頁(yè)) RTC (Real Time Clock):實(shí)時(shí)時(shí)鐘 實(shí)時(shí)時(shí)鐘是一個(gè)獨(dú)立的定時(shí)器。RTC模塊擁有一組連續(xù)

2021-06-30 15:54:18 11998

11998 STM32CubeMX | 40 - 實(shí)時(shí)時(shí)鐘RTC的使用(日歷和鬧鐘)

2021-11-23 18:06:59 19

19 實(shí)時(shí)時(shí)鐘的縮寫(xiě)是RTC(Real_Time Clock)實(shí)時(shí)時(shí)鐘是一個(gè)獨(dú)立的定時(shí)器。RTC模塊擁有一組連續(xù)計(jì)數(shù)的計(jì)數(shù)器,在相應(yīng)軟件配置下,可提供時(shí)鐘日歷的功能。修改計(jì)數(shù)器的值可以重新設(shè)置系統(tǒng)當(dāng)前

2021-12-02 16:51:18 7

7 RTC是什么–簡(jiǎn)介RTC,英文全稱(chēng):Real-time clock,中文名稱(chēng):實(shí)時(shí)時(shí)鐘,是指可以像時(shí)鐘一様輸出實(shí)際時(shí)間的電子設(shè)備,一般會(huì)是集成電路,因此也稱(chēng)為時(shí)鐘芯片。實(shí)時(shí)時(shí)鐘芯片是日常生活中

2021-12-04 18:06:06 19

19 2012.1.11 讀取實(shí)時(shí)時(shí)鐘: 1、 RTCRDY 為0時(shí),不能取讀取實(shí)時(shí)時(shí)鐘 RT0PS源于ACLK,為了實(shí)時(shí)時(shí)鐘日歷的正確的運(yùn)行,ACLK必須是32768Hz。(易出錯(cuò)) 定時(shí)

2021-12-16 16:56:55 10

10 RTC實(shí)時(shí)時(shí)鐘1. RTC實(shí)時(shí)時(shí)鐘簡(jiǎn)介2. 硬件設(shè)計(jì)3. 軟件設(shè)計(jì)3.1 STM32CubeMX設(shè)置3.2 MDK-ARM編程4. 下載驗(yàn)證

2021-12-24 19:15:46 17

17 本文以浮點(diǎn)數(shù)Floating-point IP核將定點(diǎn)數(shù)轉(zhuǎn)換為浮點(diǎn)數(shù)為例,詳細(xì)講解AXI DMA IP核的使用方法。

2022-02-16 16:21:37 13087

13087

本文主要介紹關(guān)于AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核相關(guān)內(nèi)容。為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測(cè)試工程做準(zhǔn)備。

2022-07-03 16:11:05 10565

10565 MicroBlaze可以使用AXI BRAM存放數(shù)據(jù)和指令。有些客戶(hù)軟件很大,需要把AXI BRAM的空間做到最大。AXI BRAM底層是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM個(gè)數(shù),決定了AXI BRAM的大小。

2022-08-02 10:09:05 4186

4186

AXI (高性能擴(kuò)展總線(xiàn)接口,Advanced eXtensible Interface)是ARM AMBA 單片機(jī)總線(xiàn)系列中的一個(gè)協(xié)議,是計(jì)劃用于高性能、高主頻的系統(tǒng)設(shè)計(jì)的。AXI協(xié)議是被優(yōu)化

2022-10-10 09:22:22 11273

11273 電子發(fā)燒友網(wǎng)站提供《帶定時(shí)器的實(shí)時(shí)時(shí)鐘.zip》資料免費(fèi)下載

2022-11-01 11:34:46 0

0 電子發(fā)燒友網(wǎng)站提供《ESP32 Feather實(shí)時(shí)時(shí)鐘開(kāi)源分享.zip》資料免費(fèi)下載

2022-12-09 10:05:16 1

1 DA1468x SoC 的實(shí)時(shí)時(shí)鐘 (RTC) 概念

2023-03-15 20:16:32 0

0 實(shí)時(shí)時(shí)鐘(RTC: Real-Time Clock)是集成電路,通常稱(chēng)為時(shí)鐘芯片。目前實(shí)時(shí)時(shí)鐘芯片大多采用精度較高的晶體振蕩器作為時(shí)鐘源。

2023-05-08 10:45:45 3679

3679

最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線(xiàn)進(jìn)行數(shù)據(jù)和指令傳輸。如果有多個(gè)設(shè)備需要使用AXI協(xié)議對(duì)AXI接口的BRAM進(jìn)行讀寫(xiě),總線(xiàn)之間該如何進(jìn)行仲裁,通信?

2023-06-19 15:45:14 14453

14453

外部存儲(chǔ)器接口( EMIF )通信常用于FPGA和DSP之間的數(shù)據(jù)傳輸,即將FPGA作為DSP的外部SRAM、或者協(xié)同處理器等。Xilinx提供了AXI-EMC IP核,將其掛載到AXI總線(xiàn)用于

2023-08-31 11:25:41 11848

11848

本文開(kāi)源一個(gè)FPGA項(xiàng)目:基于AXI總線(xiàn)的DDR3讀寫(xiě)。之前的一篇文章介紹了DDR3簡(jiǎn)單用戶(hù)接口的讀寫(xiě)方式:《DDR3讀寫(xiě)測(cè)試》,如果在某些項(xiàng)目中,我們需要把DDR掛載到AXI總線(xiàn)上,那就要通過(guò)MIG IP核提供的AXI接口來(lái)讀寫(xiě)DDR。

2023-09-01 16:20:37 7275

7275

CW32實(shí)時(shí)時(shí)鐘(RTC)介紹

2023-10-24 15:36:07 2038

2038

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關(guān)IP核中,經(jīng)常見(jiàn)到AXI總線(xiàn)接口,AXI總線(xiàn)又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 2142

2142

I2C總線(xiàn)接口的實(shí)時(shí)時(shí)鐘/日歷芯片封裝:SOP8_150MIL

2022-08-19 16:00:10 1

1 DS1307時(shí)鐘模塊:** DS1307串行實(shí)時(shí)時(shí)鐘(RTC)是低功耗,全二進(jìn)制編碼的十進(jìn)制(BCD)時(shí)鐘/日歷以及56字節(jié)的NV SRAM。

2023-11-01 16:49:05 3589

3589

電子發(fā)燒友網(wǎng)站提供《基于51單片機(jī)的實(shí)時(shí)時(shí)鐘設(shè)計(jì).rar》資料免費(fèi)下載

2024-01-02 10:15:59 43

43 電子發(fā)燒友網(wǎng)站提供《基于51單片機(jī)的實(shí)時(shí)時(shí)鐘設(shè)計(jì).rar》資料免費(fèi)下載

2024-01-12 10:43:47 13

13 電子發(fā)燒友網(wǎng)站提供《使用實(shí)時(shí)時(shí)鐘庫(kù).pdf》資料免費(fèi)下載

2024-10-22 10:09:41 0

0 10GBe/40GBe UDP 協(xié)議棧 IP 核、10GbE TCP/IP 協(xié)議棧 IP 核和 NVMe AXI IP 核。 ? ALINX 發(fā)布的 10GbE TCP/IP 協(xié)議棧 IP 核,能夠?qū)崿F(xiàn)

2024-10-30 17:39:43 1459

1459

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論