在創(chuàng)新加速的浪潮中,為更好地響應(yīng)客戶群需求,芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,致力于為高性能數(shù)據(jù)傳輸和復(fù)雜計(jì)算需求提供高帶寬、低延遲的解決方案。發(fā)布的第一批 IP 核包括 10GBe/40GBe UDP 協(xié)議棧 IP 核、10GbE TCP/IP 協(xié)議棧 IP 核和 NVMe AXI IP 核。

ALINX 發(fā)布的 10GbE TCP/IP 協(xié)議棧 IP 核,能夠?qū)崿F(xiàn)符合 IEEE802.3 標(biāo)準(zhǔn)的完整協(xié)議棧,支持高達(dá) 9000 字節(jié)的 MTU,特別適用于需要大規(guī)模數(shù)據(jù)傳輸和實(shí)時(shí)視頻處理的應(yīng)用場景。

10GbE TCP/IP 協(xié)議棧 IP 核注重?cái)?shù)據(jù)傳輸?shù)目煽啃裕邆渫暾?TCP 傳輸控制機(jī)制,包括流量控制、重傳和保序,以確保數(shù)據(jù)的完整性和準(zhǔn)確性。支持最多兩條TCP 連接的設(shè)計(jì)使其能夠在數(shù)據(jù)庫同步、文件傳輸?shù)葢?yīng)用中提供強(qiáng)勁穩(wěn)定的傳輸性能。

ALINX 發(fā)布的 NVMe AXI IP 核,專注于加速存儲訪問,通過 PCIe 接口連接外部 NVMe SSD,支持自動鏈路初始化和 3000MB/s 的讀寫速率,充分滿足高性能存儲應(yīng)用的需求。該 IP 核便于集成到 Xilinx 架構(gòu)中,在數(shù)據(jù)中心和高性能計(jì)算應(yīng)用中大幅提升存儲效率。

憑借高效的設(shè)計(jì)和完備的技術(shù)支持服務(wù),芯驛電子 ALINX 的 IP 核將幫助客戶在復(fù)雜的計(jì)算和存儲環(huán)境中實(shí)現(xiàn)性能優(yōu)化與快速部署,推動企業(yè)在競爭激烈的市場中持續(xù)創(chuàng)新與突破。

以下為產(chǎn)品特性介紹,完整用戶手冊請聯(lián)系銷售工程師獲取。

10GbE TCP/IP協(xié)議棧IP核

產(chǎn)品特性

根據(jù) OSI 分層模型實(shí)現(xiàn)符合 IEEE802.3 標(biāo)準(zhǔn)的 ARP、IPV4、ICMP、TCP 協(xié)議棧

支持 ARP,用于獲取或發(fā)送 MAC 地址

支持 ICMP,用于響應(yīng) Ping 命令

作為 TCP 的 server,響應(yīng) client 的建聯(lián)請求、斷聯(lián)請求,也可主動發(fā)起斷聯(lián)請求

ARP 報(bào)文應(yīng)答支持所有來查詢的應(yīng)答,但只維護(hù)一個業(yè)務(wù)所用的 ARP 表

ARP 表未建立時(shí),不響應(yīng)建聯(lián)請求

ARP 表已建立時(shí),接受到配置的 TCP 監(jiān)聽請求后才會響應(yīng)建聯(lián)請求

10Gps 以太網(wǎng)連接,支持 TCP,IP 的校驗(yàn)和的產(chǎn)生與校驗(yàn),CRC 由 MACIP 計(jì)算產(chǎn)生

基于 Xilinx 10G MAC IP 開發(fā),支持最大 MTU 高達(dá) 9000 Bytes,最小 64 Bytes 的數(shù)據(jù)傳輸

TCP 數(shù)據(jù)報(bào)文的發(fā)送、接收、應(yīng)答及心跳包的維護(hù)

TCP 傳輸中保序、重傳、確認(rèn)、快重傳

TCP 傳輸中基于接收和發(fā)送窗口的流量控制

TCP 建聯(lián)后,接收到客戶端 RST 報(bào)文時(shí),直接斷開連接

最多支持兩條 TCP 連接

用戶接口為 AXI4stream 接口,協(xié)議棧利用 MACIP 產(chǎn)生的時(shí)鐘 156.25MHz,10Gps 數(shù)據(jù)總線寬度 64 bit

TCP_IP 協(xié)議棧 IP core 內(nèi)部數(shù)據(jù)為 8Bytes 對齊處理

應(yīng)用場景

各類需要高速數(shù)據(jù)傳輸、高吞吐量的網(wǎng)絡(luò)通信應(yīng)用場景:

數(shù)據(jù)中心與云計(jì)算

4K/8K 視頻傳輸與處理

高性能嵌入式系統(tǒng)

網(wǎng)絡(luò)測試設(shè)備與網(wǎng)絡(luò)監(jiān)測

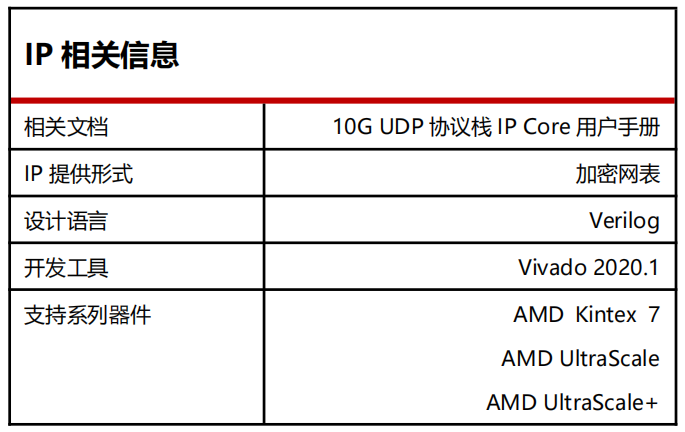

10GbE UDP協(xié)議棧IP核

產(chǎn)品特性

根據(jù) OSI 分層模型實(shí)現(xiàn)符合 IEEE802.3 標(biāo)準(zhǔn)的 ARP、IPV4、ICMP、UDP 協(xié)議棧

支持 ARP,用于獲取或發(fā)送 MAC 地址

支持 ICMP,用于響應(yīng) Ping 命令

ARP 報(bào)文應(yīng)答支持所有來查詢的應(yīng)答,可以緩存 10 個 ARP 表

ARP 表未建立時(shí),不會發(fā)送 UDP 數(shù)據(jù)包

10Gps 以太網(wǎng)連接,支持 UDP,IP 的校驗(yàn)和的產(chǎn)生與校驗(yàn),CRC 由 MACIP 計(jì)算產(chǎn)生

基于 Xilinx 10G MAC IP 開發(fā),支持最大 MTU 高達(dá) 9000 Bytes,最小 64 Bytes 的數(shù)據(jù)傳輸

用戶接口為 AXI4stream 接口,協(xié)議棧利用 MACIP 產(chǎn)生的時(shí)鐘 156.25MHz,10Gbps 數(shù)據(jù)總線寬度 64 bit

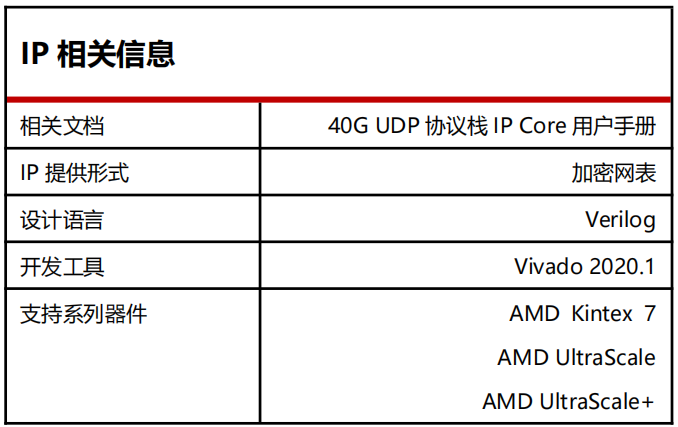

40GbE UDP協(xié)議棧IP核

產(chǎn)品特性

根據(jù) OSI 分層模型實(shí)現(xiàn)符合 IEEE802.3 標(biāo)準(zhǔn)的 ARP、IPV4、ICMP、UDP 協(xié)議棧

支持 ARP,用于獲取或發(fā)送 MAC 地址

支持 ICMP,用于響應(yīng) Ping 命令

ARP 報(bào)文應(yīng)答支持所有來查詢的應(yīng)答,可以緩存 10 個 ARP 表

ARP 表未建立時(shí),不會發(fā)送 UDP 數(shù)據(jù)包

40Gbps 以太網(wǎng)連接,支持 UDP,IP 的校驗(yàn)和的產(chǎn)生與校驗(yàn),CRC 由 MACIP 計(jì)算產(chǎn)生

基于 Xilinx 40G MAC IP 開發(fā),支持最大 MTU 高達(dá) 9000 Bytes,最小 64 Bytes 的數(shù)據(jù)傳輸

用戶接口為 AXI4stream 接口,協(xié)議棧利用 MACIP 產(chǎn)生的時(shí)鐘 312.5MHz,40Gbps 數(shù)據(jù)總線寬度 256 bit

應(yīng)用場景

大規(guī)模數(shù)據(jù)中心和云計(jì)算

媒體和娛樂領(lǐng)域?qū)崟r(shí)視頻處理與傳輸

大規(guī)模 AI 與機(jī)器學(xué)習(xí)集群

工業(yè)物聯(lián)網(wǎng)和自動化

科研、醫(yī)療成像、基因測序等

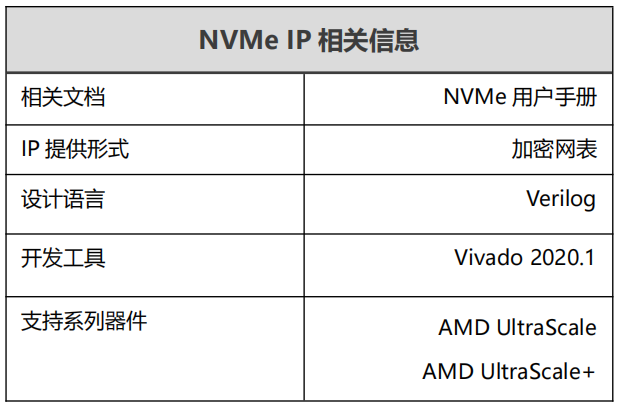

NVMe AXI IP

產(chǎn)品特性

實(shí)現(xiàn)不依靠 CPU 通過 PCIe 訪問外部內(nèi)存 NVMe SSD

支持命令:Identify, Write, Read, and Flush

支持 PCIe Gen 1.0,2.0,3.0,4.0

兼容 NVM Express 1.4 協(xié)議

自動初始化 NVMe 和 PCIe 鏈路硬件模塊

自動的提交和完成命令

支持最大每個隊(duì)列 65535 個 I/O 命令

基于 PCIe3.0 X4 讀寫速率均可達(dá)到 3000MB/s

MPSMIN(最小內(nèi)存頁傳輸大小):4Kbyte

MDTS(最大數(shù)據(jù)傳輸大小):至少 128Kbyte 或者沒有限制

LBA 單元:512 字節(jié)或者 4096 字節(jié)

NVMe IP 支持兩個版本,包括 AXI FULL 版本和 AXI Stream 版本

實(shí)現(xiàn)的參考設(shè)計(jì):XCZU19EG+FMC子板(FH1402)+SAMSUNG 980 M.2 SSD

提供完備的技術(shù)支持與定制化設(shè)計(jì)服務(wù)

應(yīng)用場景

智能監(jiān)控

醫(yī)療設(shè)備

審核編輯 黃宇

-

FPGA

+關(guān)注

關(guān)注

1660文章

22408瀏覽量

636211 -

IP核

+關(guān)注

關(guān)注

4文章

344瀏覽量

51944

發(fā)布評論請先 登錄

NVMe over Fabrics 國產(chǎn) IP:高性能網(wǎng)絡(luò)存儲解決方案

基于AXI DMA IP核的DDR數(shù)據(jù)存儲與PS端讀取

使用AXI4接口IP核進(jìn)行DDR讀寫測試

Xilinx高性能NVMe Host控制器IP+PCIe 3.0軟核控制器IP,純邏輯實(shí)現(xiàn),AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

VDMA IP核簡介

Vivado浮點(diǎn)數(shù)IP核的握手信號

ram ip核的使用

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

NVMe IP高速傳輸卻不依賴便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

VIVADO自帶Turbo譯碼器IP核怎么用?

NVMe IP之AXI4總線分析

NVMe控制器IP設(shè)計(jì)之接口轉(zhuǎn)換

一文詳解Video In to AXI4-Stream IP核

芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,覆蓋 TCP/UDP/NVMe AXI IP 核

芯驛電子 ALINX 推出全新 IP 核產(chǎn)品線,覆蓋 TCP/UDP/NVMe AXI IP 核

評論