。 Pynq降低了開發人員的門檻,但知其然也知其所以然,開發效率將會更高。因此,在進入PYNQ的python開發之前,我們先來學習ZYNQ的PL與PS開發,為接下來的學習提供良好的基礎。 本部分的學習

2020-12-25 14:11:50 9769

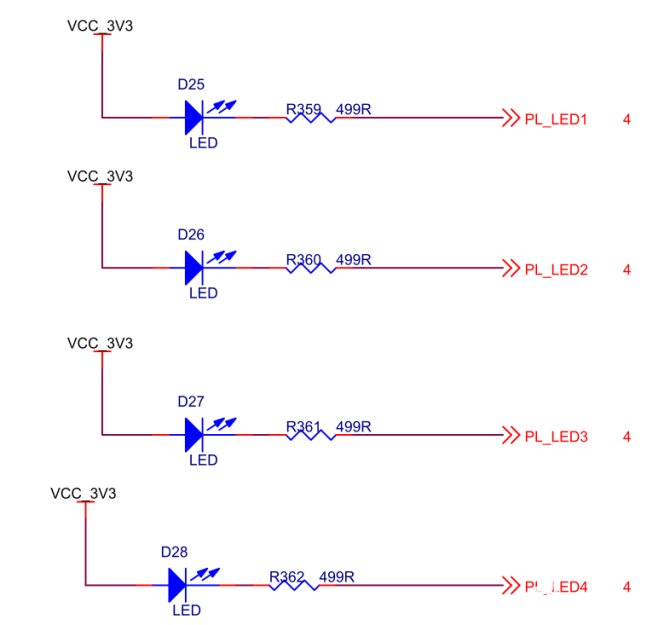

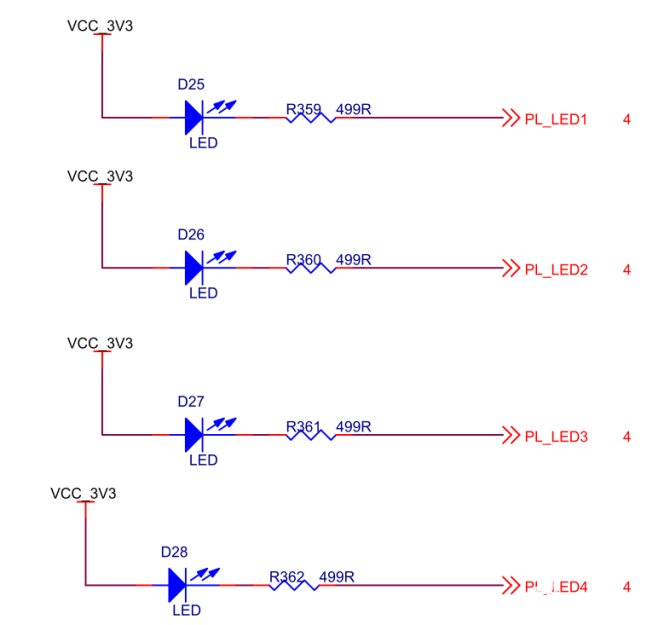

9769 對于ZYNQ來說PL(FPGA)開發是至關重要的,這也是ZYNQ比其他ARM的有優勢的地方,可以定制化很多ARM端的外設,在定制ARM端的外設之前先讓我們通過一個LED例程來熟悉PL(FPGA)的開發流程,熟悉Vivado軟件的基本操作,這個開發流程和不帶ARM的FPGA芯片完全一致。

2021-01-21 13:28:08 18886

18886

使用zynq最大的疑問就是如何把PS和PL結合起來使用,在其他的SOC芯片中一般都會有GPIO,本實驗使用一個AXI GPIO的IP核,讓PS端通過AXI總線控制PL端的LED燈,實驗雖然簡單,不過可以讓我們了解PL和PS是如何結合的。

2021-02-01 10:06:00 7851

7851

PL和PS的高效交互是zynq soc開發的重中之重,我們常常需要將PL端的大量數據實時送到PS端處理,或者將PS端處理結果實時送到PL端處理,常規我們會想到使用DMA的方式來進行,但是各種協議非常

2021-01-30 09:54:00 16464

16464

/005899fe6815 二、ZYNQ7020 分為PS端、PL端 PS: 處理系統 (Processing System) , 就是與 FPGA 無關的 ARM 的 SOC 的部分。 PL: 可編程邏輯

2021-05-12 10:25:31 19446

19446

本文主要介紹ZYNQ PS + PL異構多核案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 3710

3710

本帖最后由 Tronlong創龍科技 于 2021-6-7 08:48 編輯

?本文主要介紹ZYNQ PS + PL異構多核案例的使用說明,適用開發環境:Windows 7/10 64bit

2021-05-28 14:28:28

ZYNQ 分為 PS 和 PL 兩部分,那么器件的引腳(Pin)資源同樣也分成了兩部分。ZYNQ PS 中的外設可以通過 MIO(Multiuse I/O,多用輸入/輸出)模塊連接到 PS 端的引腳

2022-02-08 07:27:16

ZYNQ學習筆記_ZYNQ簡介和Hello WorldZYNQ介紹PS和PL的連接ZYNQ開發工具鏈在PS端編寫Hello World程序ZYNQ介紹ZYNQ-7000系列是基于Xilinx開發環境

2022-02-17 07:37:36

嗨,我必須找出zynq 7020 PS和zynq PL如何通話,特別是我必須找到將在ARM中處理的SDK C代碼。你能用一個明確的C代碼告訴我,它解釋了數據如何從PS轉移到PL,這是ARM用來做這個的基本程序嗎?謝謝

2020-05-08 09:37:11

史上最簡單Spring Boot教程:第四篇SpringBoot之freemarker模板(四)

2019-08-30 08:59:34

rk3568硬件開發筆記(第四篇 ) 固態硬盤電路設計 開發板上使用標準 PCIe3.0 連接座,可安裝外部 PCIe 板卡進行通信。?工作模式:Root Complex(RC)。?鏈路支持 4

2023-03-06 08:46:45

這是本次測評的第四篇,本篇主要介紹,采用57BYG250D步進電機進行開發板的測試,本次供電采用DC24V,采用32步分辨率方式驅動。測得電機極限最高速度時,驅動CLK為88Khz,恢復轉動頻率為16Khz。停轉待機電流為80mA。

2021-01-25 22:05:19

輸入到PL的管腳上一個時鐘信號,另一種方法則是使用PS提供給PL的時鐘信號。從ZYNQ的技術手冊里我們得知,PS部分可以提供給PL四路相對獨立的時鐘信號(它們之間不保證時序上的關系),因此我們的任務就是

2015-06-01 11:54:12

原子公眾號,獲取最新資料第十四章基于BRAM的PS和PL的數據交互在ZYNQ SOC開發過程中,PL和PS之間經常需要做數據交互。對于傳輸速度要求較高、數據量大、地址連續的場合,可以通過AXI DMA來

2020-09-04 11:08:46

錯誤。然后,我在SDK中編程PS端,led閃爍正確的頻率!我的問題,當鎖定Zynq PL時鐘? PS程序之后?需要多長時間?是不是意味著,PL配置期間LED閃爍錯誤,在非易失性Flas Boot中編程PS期間(或之后)閃爍?謝謝的Berker

2020-08-27 15:09:19

/Adam-Taylor-s-MicroZed-Chronicles-Part-180-All-about-the-Xilinx/ba-p/756988但該芯片自帶板,Zynq 7020屬于Zynq家族。是否可以在電路板上使用它?如果沒有,支持reVision的官方(Xilinx / AVNet / ...)主板的最低成本是多少?籌碼怎么樣?

2019-10-10 06:25:58

你好我在Zynq 7010設計上添加了一個UART 16550 IP,中斷直接連接到Zynq INTC。在petalinux中導入硬件設計后,pl.dtsi結構似乎沒問題,但是當我編譯圖像并啟動板

2020-04-08 07:50:34

`玩轉Zynq連載19——[ex02]基于Zynq PL的歡快流水燈 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網盤鏈接:https

2019-08-28 09:26:47

),而必須把MIO0和MIO9保留給GPIO MIO使用。完成配置后,重新編譯PL工程,確保當前配置產生.bit文件。 2 導出PS硬件配置和新建SDK工程參考文檔《玩轉Zynq-工具篇:導出PS硬件配置

2019-10-10 11:21:06

://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw提取碼:ld9c 1 Zynq的GPIO概述參考文檔《玩轉Zynq-基礎篇:Zynq PS的GPIO外設.pdf》。關于

2019-10-12 17:35:16

至芯科技之altera 系列FPGA教程 第四篇 新建工程

2016-08-11 03:17:52

請問zynq 怎么實現PS與PL數據交互,然后通過UART串口打印出來?前輩們做過的指導我一下。

2020-08-03 15:53:30

XAPP1251說明顯示,可以在Zynq ARM處理器上運行XVC服務器來控制FPGA中的JTAG端口。但是,我不清楚,是否可以在同一個FPGA中控制PL JTAG?可以使用運行在設備PS部分上

2020-07-30 13:51:19

本文通過實例詳細解析如何利用Zynq-7000的PL和PS進行交互。實際上,Zynq就是兩大功能塊:雙核Arm的SoC和FPGA。根據Xilinx提供的手冊,PS: 處理系統 (Processing System) , 就是與FPGA無關的A

2012-12-12 13:40:22 58287

58287

By Adam Taylor 到目前為止的文章中,我們已經研究了MicroZed開發板上使用以太網的數據傳輸問題。我們還沒有涉及片上外設通信的問題:實時時鐘,非易失內存以及獨特的傳感器。這些通信涉及到I2C或者SPI總線。

2017-01-13 11:07:11 1045

1045 在Adam Taylor玩轉MicroZed系列的前期部分中,我們介紹了IP棧的概念。(見Adam Taylor玩轉MicroZed系列第79部分:Zynq SoC以太網第3部分)接下來就是在我們的設計中使用該協議棧了。SDK開發環境允許我們創建BSP的時候包含一個輕量級的IP棧(lwIP)。

2017-01-13 11:17:11 1413

1413

By Adam Taylor 在本系列博客的前兩部分中,我們研究了帶有Zynq SoC PS(處理器系統)的以太網MAC(介質訪問控制層),包括深入探討了一個MAC使用范例。以太網MAC是一個基礎的構建模塊,它允許我們實現一個IP棧,然后因此給我們的工程創建聯網條件。

2017-01-13 11:24:11 1018

1018 By Adam Taylor 在約束系列的最后,我們講講關聯布局宏(RPM)的約束。RPM允許你在FPGA的布局中將DSP、FF、LUT和RAMS等資源組合在一起。與PBlocks不同,RPM并不

2017-11-10 14:49:02 1165

1165 分享下PS與PL之間數據傳輸比較另類的實現方式,實現目標是: 1、傳輸時數據不能滯留在一端,無論是1個字節還是1K字節都能立即發送; 2、PL端接口為FIFO接口; PS到PL的數據傳輸流程: PS

2017-02-08 01:00:11 2324

2324

By Adam Taylor 在過去一周中,我接到了很多不同人的來信,他們正在使用以Zynq為基礎的開發工具。他們非常想知道怎么樣去把MicroZed系列博客教程應用到他們所選擇的硬件平臺上。加上

2017-02-08 02:12:49 745

745

By Adam Taylor 在先前的博客中我們研究過I/O約束,下一個合乎邏輯的步驟就是研究如何在我們的設計中用FPGA進行放置和布線約束。使用放置約束的原因如下:為了幫助實現時序,或者為了在

2017-02-08 02:22:11 404

404 通過前面的學習,我們已經對Zynq系列的PL和PS部分已經有了相當多的了解。其中有關約束的部分我們曾經提到過但是沒有重點關注。約束可以添加特定的信息到你的設計,并在綜合工具和實現工具中可以得到實現

2017-02-08 03:58:43 1001

1001

上周的博客中我們完成了硬件的搭建,并且把硬件部分導入到SDK,見Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通過寫一個簡單的程序

2017-02-08 05:53:11 565

565

上周的博客中我們學習了Zynq SoC的AXI DMA,我解釋了怎樣利用AXI DMA控制器將數據從PL搬運到PS。在本期博客中我們將學習怎樣完成硬件的搭建。 首先我們要更深入的了解一下AXI

2017-02-08 08:10:39 527

527 有意思的方面,就是它能夠將數據從PL(可編程邏輯)部分移動至存儲器中——例如片上存儲器或者DDR SDRAM,而存儲器是映射到PS的地址空間上的。 作為工程師我們一直想這樣做,將在Zynq PL部分實現的硬件存儲器映射到PS部分的地址空間中,這是非常有用的,因為這樣做可以允

2017-02-08 08:14:11 336

336

通過EMIO布線到PL; c)新增了四通道的高速GTR收發器; d)DDR控制更新到可支持DDR4L-2400速率。 (1)MIO資源 Zynq UltraScale+具有78個可配置復用的MIO,這些MIO可用作將PS內的相關外設控制器引出,同時

2017-02-08 08:29:11 1469

1469

在本系列上一篇博客中,我們學習了解了使用XMD和XSDB來調試我們的應用和系統。然而為了確保我們的應用在性能上是優化的,另一個非常重要的方面就是對應用程序進行詳細分析。 分析不同于調試,就分析功能

2017-02-08 09:53:00 263

263 在此系列博客的前面幾期中,我們已經可以運行示例應用并獲得用于分析的程序運行數據。運行分析器可以生成一個gmon.out格式的文件,它包含了分析數據。當應用程序運行自然結束或者通過SDK來終止應用程序

2017-02-08 09:56:49 370

370

在上一篇的MicroZed系列博客中,我們學習了兩種與XADC進行通信的方法:Zynq SoC 的AXI或者DevC接口。通過在每個驅動程序中輸出XADC的基地址,我演示了這兩種XADC通信方法

2017-02-08 09:58:42 413

413 討論,這個問題解決之后我們將回來繼續學習PicoBlaze。 前面的博客中提到,有多種方式可以實現XADC與Zynq之間的交互,除了JTAG接口: 1.我們可以借助DevC接口實現XADC與PS(處理器系統)之間的直接交互,使用這種方式時,Zynq SoC的PL(可編程邏輯)部分不需要進行配置。然

2017-02-08 10:04:11 400

400 前面的幾篇博客中,我們通過介紹怎樣驅動CCD的一些知識了解了PicoBlaze的一些特點,同時也知道了通過Zynq PS(處理器系統)可是實現PicoBlaze的動態可重配置,我覺得在這次博客當中

2017-02-08 11:11:37 250

250 作者:Adam Taylor 在上一篇博客中我們已經知道了如何動態更新PicoBlaze的運行程序,現在我們要學習一個完成的設計應用。一個非常相關的應用就是驅動CCD(電荷耦合元件)圖像傳感器,因為

2017-02-08 12:31:33 279

279 正如我上周所講,Petalinux是Xilinx針對Zynq SoC提供的Linux官方版本。為了攫取該版本最大資源,我們需要創建自己的版本。這就需要我們在Linux環境下進行開發。現在,并不是

2017-02-08 13:58:08 384

384 如果在我們的虛擬機上已經安裝好了SDK,我們就得使用Linux操作系統來建立我們自己的應用程序。這通常需要對 Zynq SoC的硬件重新進行定義。 首先,我們要做的就是確保將VIVADO設計套件以及

2017-02-08 13:58:11 645

645 我必須承認這是一篇我從來不希望要寫的博客。當我開始寫玩轉MicroZed時,我還不確定每周一篇寫到52篇。達到這樣的里程碑并擁有150,000的瀏覽量,我想回顧過去的一年在Zynq SoC上涵蓋

2017-02-08 15:35:37 306

306 作者:Adam Taylor 在上一篇博客中我們了解了Zynq SoC的OCM(片上存儲器) ,利用它可以實現在AMP模式下內部處理器內核之間的通信。現在我們將寫一些程序代碼將這個設備(OCM)利用

2017-02-08 15:38:12 1089

1089 作者:Adam Taylor 在最近的幾篇博客中,我們花了主要精力講解操作系統和AMP(非對稱多進程處理),接下來我們希望看到Linux系統在microzed板上運行。我們目前還沒有討論

2017-02-08 15:42:12 944

944

作者:Adam Taylor 上篇博客中我們看到了在ZynqSoC的兩塊ARM Cortex-A9 MPCore處理器之間共享數據。我提到方法可以改進——使得更加高效——我們可以使用軟件中斷來進行兩

2017-02-08 15:47:34 470

470 介紹完操作系統后我將會在Zynq SoC上演示,我打算首先在MicroZed上實現的操作系統就是Micrium公司的uC/OSiii。這是一個硬式實時操作系統,可以點擊這里下載。 該OS已經用于大量

2017-02-08 18:26:11 345

345 最近的幾篇關于MicroZed系列的博客中我們介紹并了解了RTOS(實時操作系統)的概念,既然已經介紹了基本知識,是時候在MicroZed開發板上實現運行我們的第一個操作系統。我們將使

2017-02-08 18:27:06 602

602

作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 在我前面的一篇博客(查看Adam Taylor玩轉MicroZed系列40:MicroZed操作系統第二部分)中,大家已經見識了

2017-02-08 18:27:11 387

387 我本來打算在這篇博客中繼續介紹探討運行于Zynq SoC上的操作系統。然而由于上周有人提問過一些關于Zynq SoC外設XADC,中斷和alarms的問題,我認為我們應該快速的了解一下以及我們怎樣

2017-02-08 18:30:02 655

655

在這期博客前面的幾期,我們介紹了驅動Adafruit Neopixels設計實例的解決方案架構。我們使用Vivado方塊圖設計這個解決方案(具體可以查看Adam Taylor玩轉MicroZed系列

2017-02-08 19:05:11 541

541

作者:Steve Leibson, 賽靈思戰略營銷與業務規劃總監 By Adam Taylor 我們采用基于Zynq的MicroZed板來實現Adafruit NeoPixel驅動器,前后花了8周

2017-02-08 19:06:11 379

379 到目前為止,我們已經從Zynq/MicroZed系列博客中看到了很多設計的例子,但是這些設計都沒有使用到操作系統。裸板系統對于目前我們博客中涉及到的例子已經足夠滿足設計要求了,但是如果我們想使用更加

2017-02-08 19:09:11 326

326 最近我拿到了一塊MicroZed I/O 擴展板卡,這個擴展板補充完善了MicroZed系統化模塊(SOM)設計方法,通過分解位于MicroZed開發板背面的兩個小型的I/O引腳集管上的I/O引腳來

2017-02-08 20:20:29 554

554 Adam Taylor's博客系列講解在基于ARM的Zynq SoC芯片可編程邏輯上實現定點數學函數計算。 我們已經在MicroZed 系列的前期博客中學習了在PL(可編程邏輯)內實現定點運算,現在

2017-02-09 02:07:37 447

447

NeoPixel RGB LED陣列”)在這篇博文中,我將要描述這個設計方案的硬件部分,然后在下一篇博文中描述該方案的整體架構。這個設計方案用到了Zynq SoC中的PS(處理器系統)和PL(可編程邏輯

2017-02-09 03:41:03 585

585

。 與我們在本博客系列中的方法一樣:加上所生成的頭文件作為BSP的一部分。這些頭文件提供了宏和函數,我們可以用來驅動DMA 。我們將在這個示例中加入: Xscugic.h和xil_exceptions.h

2017-02-09 05:47:33 384

384

Adam Taylor's博客系列講解基于ARM的Zynq SoC芯片可編程邏輯實現定點算法以提高性能。 這個博客系列每周發布,迄今為止已經發布了6個月,我們在Zynq SoC處理器系統(PS)中

2017-02-09 07:58:12 412

412 因為MicroZed是個低成本的開發套件,所以在板子上除了給PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供時鐘信號外,并沒有為PL部分提供單獨的晶振。

2017-02-09 14:16:11 4978

4978

我們先來了解一下上節中介紹的Zynq SoC PS/PL接口,我創建一個很簡單的外設,使用的是DSP48E1的DSP邏輯片,依靠這個外設第一個寄存器內的控制字執行乘法,加法或減法。

2017-02-10 12:04:41 843

843

《一步一步學ZedBoard & Zynq》系列第二篇,目的是為了學習不使用ARM PS情況下,只對Zynq PL的編程方法,同時學習Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 4268

4268 到現在為止,我們知道如何在基于Zynq SoC的系統中例化PicoBlaze 軟核處理器。在這篇博客,我們將繼續探索更多關于如何生成PicoBlaze 程序以及如何使用JTAG接口更新程序而不是重新編譯整個設計。

2017-02-11 07:01:06 1217

1217 Zynq SoC的處理系統提供額外功能讓我們可以建立一個更加靈活的Zynq 程序下載系統以適應更多工作。

2017-02-11 07:03:11 1451

1451

在以前發布的玩轉MicroZed系列博客中,我們建立了一個基于Zynq的系統,通過使用雙端口RAMS和BRAM(塊RAM)控制器將兩個PicoBlaze處理器核連接到Zynq的PS部分,現在我們將學習一下怎樣實現更新存儲在雙端口RAM中的PicoBlaze處理器的程序。

2017-02-11 07:05:11 1370

1370

如何獲得FreeRTOS演示并且在MicroZed上運行。FreeRTOS由Real Time Engineering公司開發,為小容量和極快運行速度的嵌入式系統提供幫助。

2017-02-11 10:03:12 1936

1936

在上一篇博客中成功地演示了FreeRTOS并在基于Zynq的MicroZed板上運行之后,顯然我們想要能夠編寫我們自己的應用程序。因此,我們將首先舉一個簡單的例子。我們將配置Zynq SoC的XADC并且在串行鏈路上輸出結果。

2017-02-11 10:03:13 1448

1448 相比較經典的FPGA,Zynq-7000系列最大的特點是將處理系統PS和可編程資源PL分離開來,固化了PS系統的存在,實現了真正意義上的SOC(System On Chip)。 1.

2017-11-18 05:11:01 20176

20176

Zynq SoC架構的主要優勢之一就是能夠通過在器件的可編程邏輯內構建外設來加快處理速度。 這是Adam Taylor 計劃編寫的Zynq-7000 All Programmable SoC實際操作

2018-01-12 03:50:33 1273

1273

Zynq在PS和PL之間有9個AXI接口。

2018-12-30 09:45:00 8291

8291 在ps的控制下,可以實現安全或非安全的配置所有ps和pl。通過zynq提供的JTAG接口,用戶可以在外部主機的控制下對zynq進行配置,zynq不支持最開始就配置pl的過程。

2019-05-15 11:41:31 8873

8873

ZYNQ中包含了兩個部分,雙核的arm和FPGA。根據XILINX提供的手冊,arm模塊被稱為PS,而FPGA模塊被稱為PL。

2020-03-15 17:13:00 8302

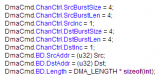

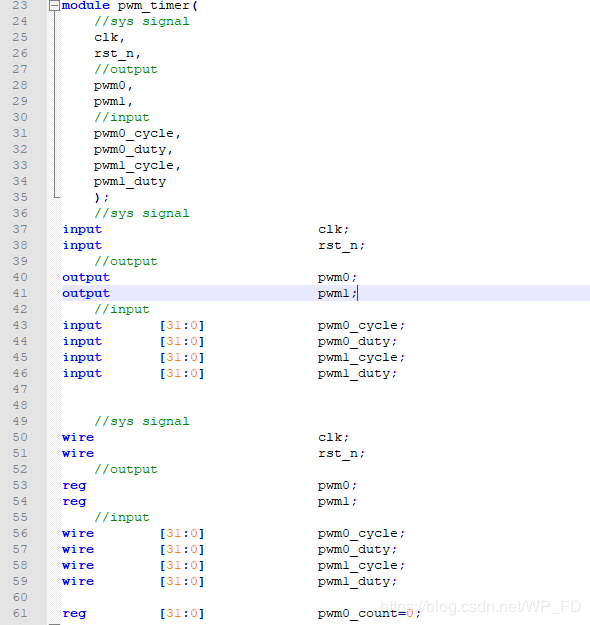

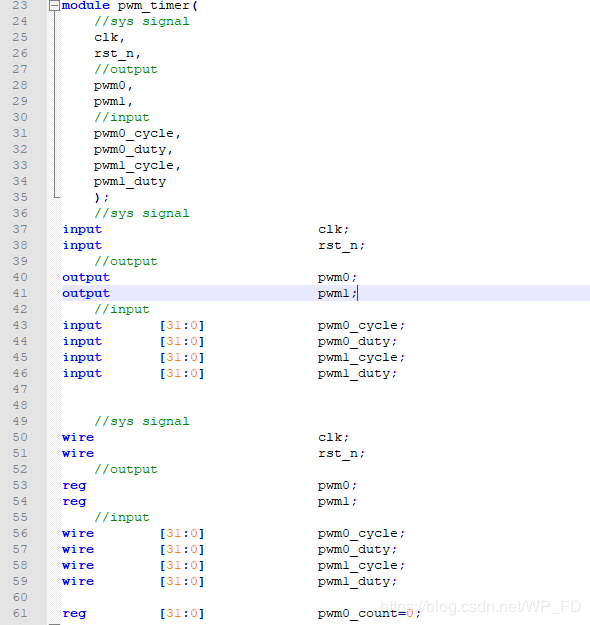

8302 在 ZYNQ進階之路1 中我們講解了PL端LED流水燈的工程的建立,編碼,綜合和下載!本節主題,PL端PWM輸出設計,講解怎么用ZYNQ PL端簡單實現2通道PWM波輸出,其中工程創建過程以及綜合

2020-11-25 15:06:36 2272

2272

Xilinx 用兩個 96 位獨特器件標識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統 (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2022-02-08 14:19:49 2342

2342

Xilinx 用兩個 96 位獨特器件標識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統 (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2021-01-23 06:32:33 10

10 ZYNQ7000系列FPGA的PS自帶兩個IIC接口,接口PIN IO可擴展為EMIO形式即將IO約束到PL端符合電平標準的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2021-01-28 08:05:27 26

26 剛學ZYNQ的時候,看到里面反復提到PS和PL,還以為PS是PhotoShop的意思,PL是哪種型號的簡稱。 稍微了解之后才知道,ZYNQ是ARM和FPGA的組合,PS是programming

2021-06-18 16:09:46 11175

11175 作者:Michael Peffers

?

歡迎閱讀《模擬線路》(Analog Wire) 上《獲得連接》博客系列的第四篇文章!在上篇博客中,我們討論了高電平的抖動問題,深入了解了隨機抖動 (RJ

2021-11-10 09:43:18 466

466

ZYNQ 分為 PS 和 PL 兩部分,那么器件的引腳(Pin)資源同樣也分成了兩部分。ZYNQ PS 中的外設可以通過 MIO(Multiuse I/O,多用輸入/輸出)模塊連接到 PS 端的引腳

2021-12-04 18:51:06 16

16 ZYNQ學習筆記_ZYNQ簡介和Hello WorldZYNQ介紹PS和PL的連接ZYNQ開發工具鏈在PS端編寫Hello World程序ZYNQ介紹ZYNQ-7000系列是基于Xilinx開發環境

2021-12-22 19:11:29 10

10 的協議,可用于寄存器式控制/狀態接口。例如,Zynq XADC 使用 AXI4-Lite 接口連接到 Zynq PS。

2022-05-10 09:52:12 4732

4732 這篇文章記錄ZYNQ7020的PS端的基本開發流程,關于PL端的開發流程,參考之前文章,這里放個超鏈接。

2022-07-24 18:12:57 12418

12418 MPSoC含有PS、PL;在PS和PL之間有大量接口和信號線,比如AXI、時鐘、GPIO等。缺省情況下,PS和PL之間有接口和信號線被關閉。加載bit后,軟件才會打開PS和PL之間的接口和信號線

2022-08-02 09:45:03 1412

1412 Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進化版本。Zynq是賽靈思發布的集成PL(FPGA)和PS設計的最早的一代產品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點.

2022-08-15 09:16:38 3750

3750 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實現的。需要注意的是,與傳統的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進行直接啟動配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 2023

2023 電子發燒友網站提供《將Zynq PS和PL與內存映射寄存器集成.zip》資料免費下載

2022-12-06 15:14:29 2

2 Zynq-7000系列芯片的邏輯資源(PL)是不同的,Z-7020以下是基于A7 FPGA的,Z-7030以上是基于K7的,資源數量有所不同。而我們使用的Zedboard是Z-7020的。

2022-12-22 09:44:09 3421

3421 S_AXI_ACP_FPD接口實現了PS 和PL 之間的低延遲連接,通過這個128位的接口,PL端可以直接訪問APU的L1和L2 cache,以及DDR內存區域。故PL側可以直接從cache中拿到APU的計算結果,同時也可以第一時間將邏輯加速運算的結果送至APU。

2023-02-01 15:36:53 4694

4694 ZYNQ 芯片分為 PL 和 PS, PS 端的 IO 分配相對是固定的,不能任意分配,雖然 PS 端的 ARM 是硬核,但是在 ZYNQ 當中也要將 ARM 硬核添加到工程當中才能使用,FPGA

2023-08-11 09:36:34 13623

13623

前言本文主要介紹PS+PL端異構多核案例的使用說明,適用開發環境:Windows7/1064bit、XilinxVivado2017.4、XilinxSDK2017.4。案例位于產品資料“4-軟件

2023-01-03 15:50:37 19

19 半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 1646

1646

【北京迅為】i.mx8mm嵌入式linux開發指南第四篇 嵌入式Linux系統移植篇第六十九章uboot移植

2024-10-22 14:46:33 1629

1629

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之間的數據交互是系統設計的核心。

2025-10-15 10:33:19 737

737

電子發燒友App

電子發燒友App

評論