以下文章來源于FPGA開源工作室,作者Leee

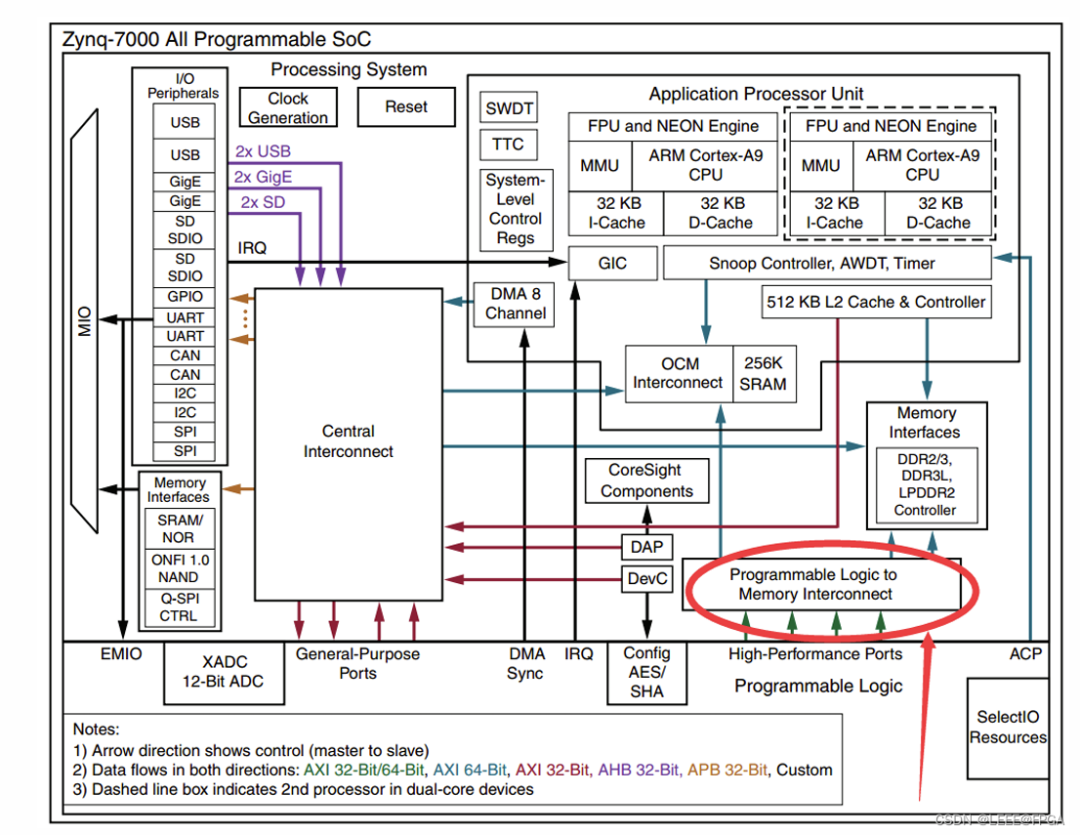

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之間的數(shù)據(jù)交互是系統(tǒng)設計的核心,以下是主要的交互方式及其特點:

一、AXI 總線接口

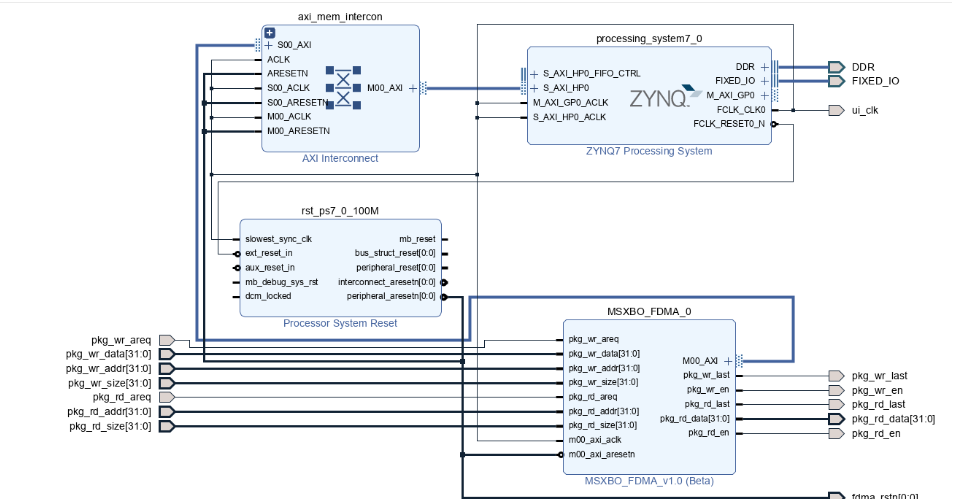

1. AXI4 高性能接口

AXI4 (AXI4-Full)

用于高性能內(nèi)存映射通信

支持突發(fā)傳輸,數(shù)據(jù)位寬通常為32/64/128/256/512位

典型應用:大數(shù)據(jù)量傳輸,如視頻流、DMA傳輸

配置:通過HP (High Performance) 或 ACP (Accelerator Coherency Port) 端口

參考學習:ZYNQ AXI4 FDMA內(nèi)存讀寫

https://leeefpga.blog.csdn.net/article/details/139261530

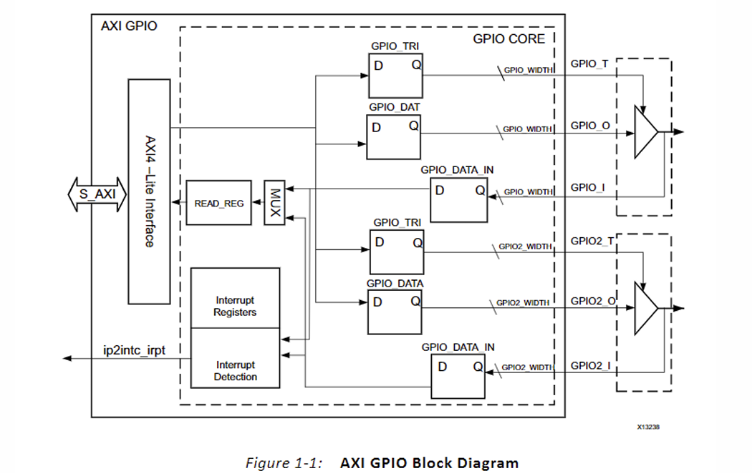

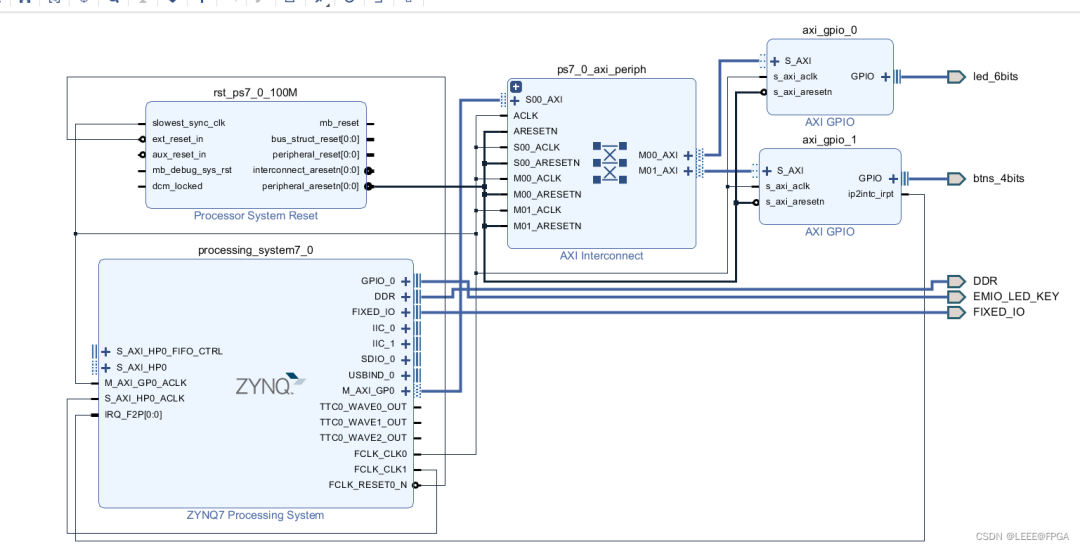

AXI4-Lite

簡化版AXI,用于寄存器級訪問

不支持突發(fā)傳輸,每次傳輸1個數(shù)據(jù)

典型應用:控制寄存器訪問、狀態(tài)監(jiān)控

配置:通常通過GP (General Purpose) 端口

如 axi_gpio

參考學習:ZYNQ AXI GPIO

https://leeefpga.blog.csdn.net/article/details/136880196

ZYNQ 自定義AXI接口 IP(PWM)

https://leeefpga.blog.csdn.net/article/details/136940289

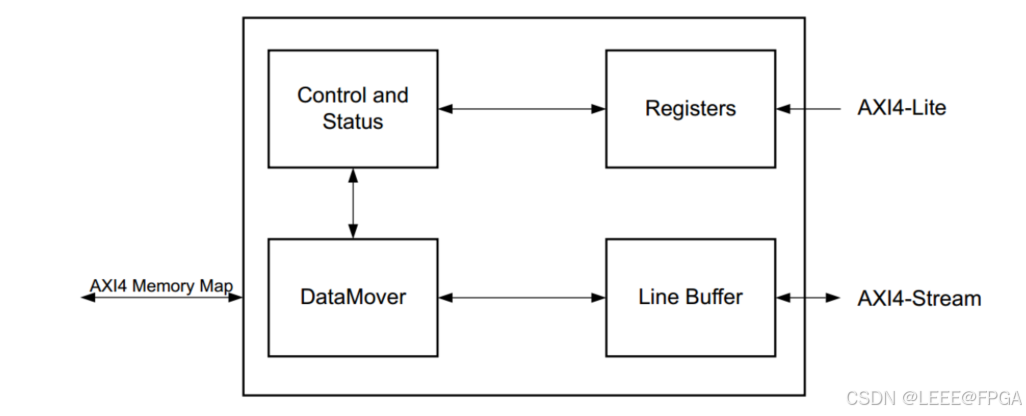

AXI4-Stream

無地址的流式數(shù)據(jù)接口

高性能連續(xù)數(shù)據(jù)傳輸

參考學習:ZYNQ VDMA IP學習

https://leeefpga.blog.csdn.net/article/details/140988072

2. 專用AXI端口

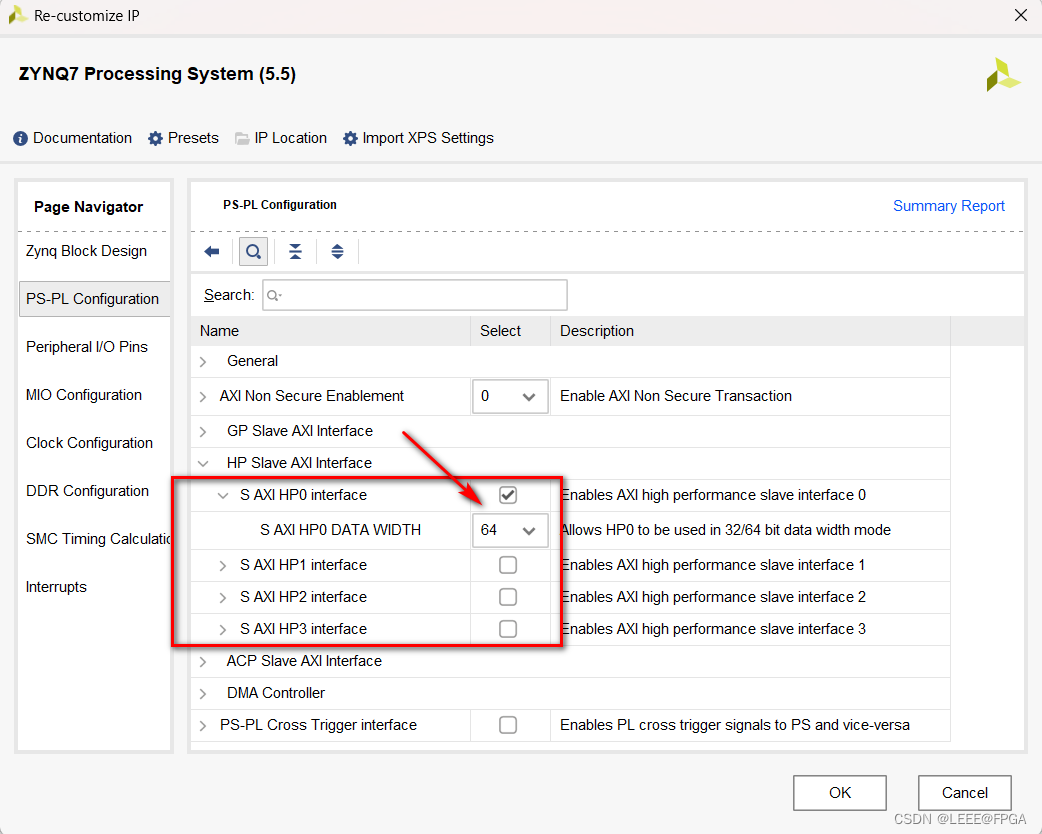

HP端口 (High Performance)

4個HP端口(PS→PL)

支持64位數(shù)據(jù)寬度,最高可達1500MB/s(每個端口)

帶FIFO緩沖,適合大數(shù)據(jù)量傳輸

ACP端口 (Accelerator Coherency Port)

1個ACP端口(雙向)

保持與CPU緩存一致性

適合需要與CPU緊密協(xié)作的加速器

參考學習:ZYNQ–PL讀寫PS端DDR數(shù)據(jù)

https://leeefpga.blog.csdn.net/article/details/138107870

GP端口 (General Purpose)

4個主端口(PS→PL) + 2個從端口(PL→PS)

32位數(shù)據(jù)寬度,性能較低

適合控制信號和少量數(shù)據(jù)傳輸

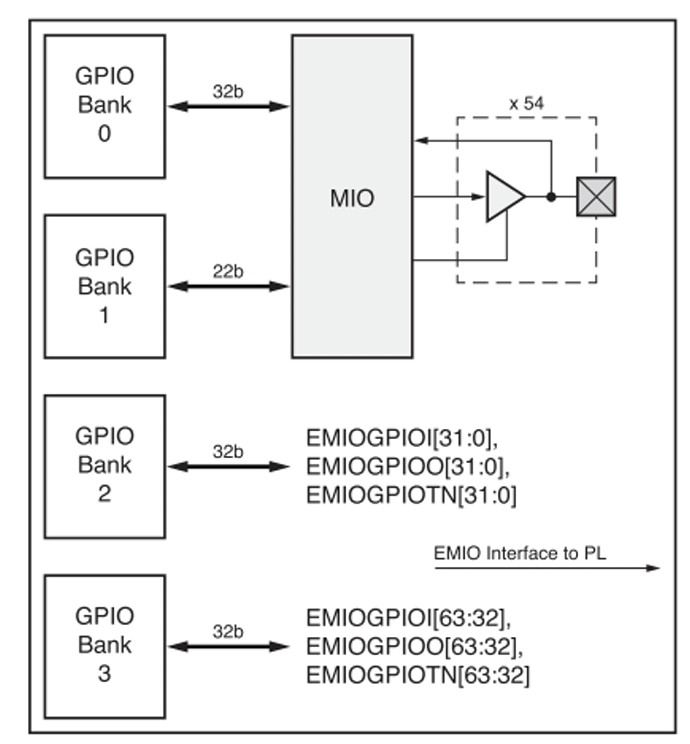

二、非AXI接口方式

1. EMIO (Extended Multiplexed I/O)

通過PS的I/O外設擴展至PL

特點:配置靈活,但帶寬有限

參考學習:ZYNQ學習(01) EMIO MIO

https://leeefpga.blog.csdn.net/article/details/136846551

ZYNQ PS端UART數(shù)據(jù)收發(fā)

https://leeefpga.blog.csdn.net/article/details/137007431

https://leeefpga.blog.csdn.net/article/details/139081862

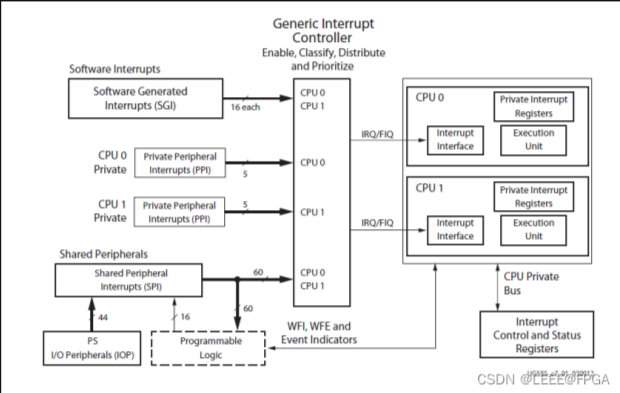

2. 中斷機制

PL→PS中斷

通過IRQ_F2P[15:0]引腳

支持電平觸發(fā)和邊沿觸發(fā)

可用于事件通知、異常處理

參考學習:ZYNQ PL 中斷請求

https://leeefpga.blog.csdn.net/article/details/134641174

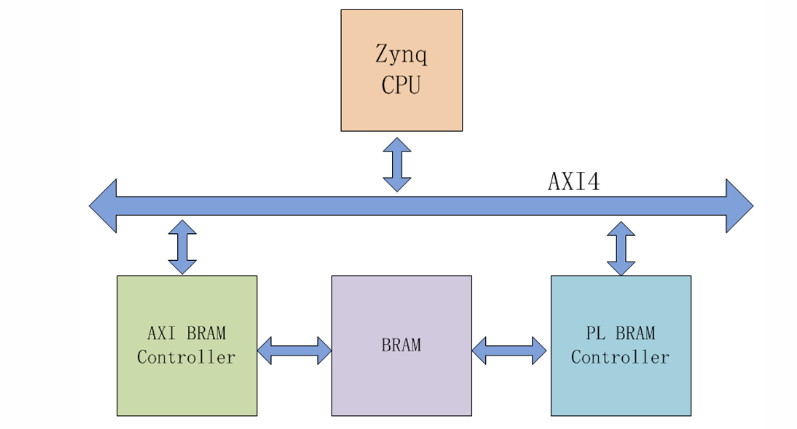

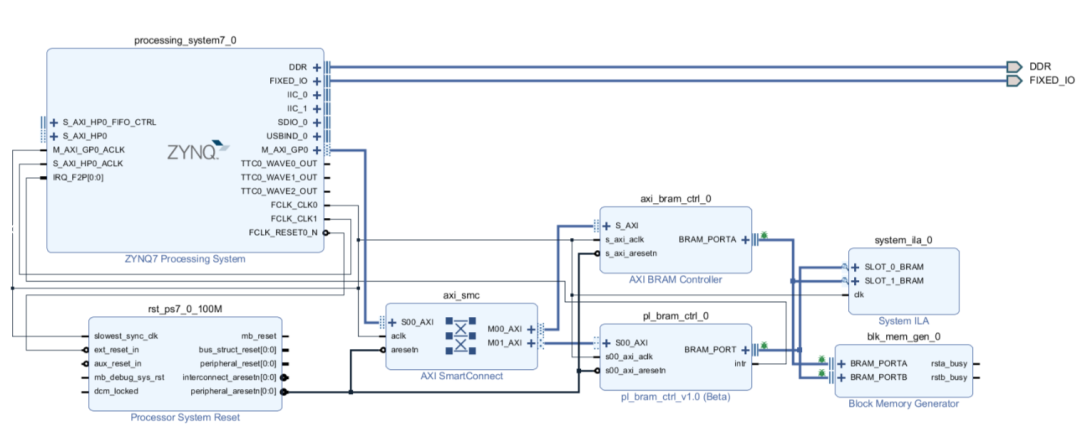

3. BRAM (Block RAM) 共享

通過PS和PL共享的片上存儲器

高速低延遲訪問

需要手動管理同步機制

參考學習:

ZYNQ BRAM實現(xiàn)PS與PL數(shù)據(jù)交互

https://leeefpga.blog.csdn.net/article/details/138116215

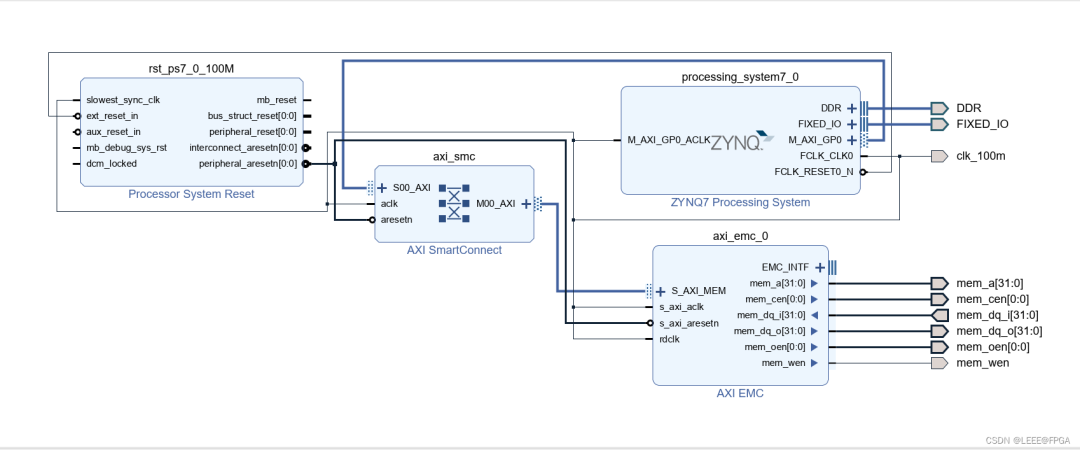

參考學習:ZYNQ EMIF進行PS與PL間的數(shù)據(jù)交互

https://leeefpga.blog.csdn.net/article/details/139289112

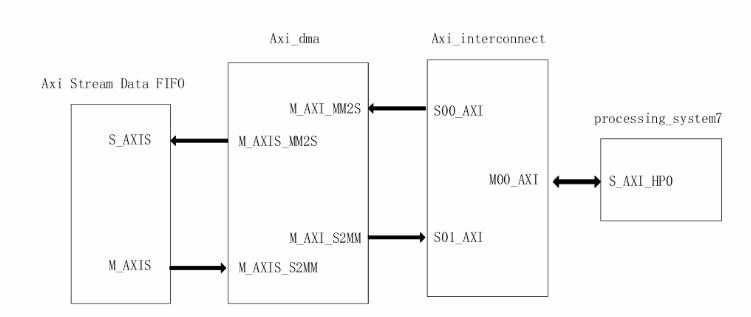

4. DMA傳輸

AXI DMA IP

支持內(nèi)存與PL間高效數(shù)據(jù)傳輸

可配置為Scatter-Gather模式

減輕CPU負擔,提高吞吐量

參考學習:ZYNQ DMA環(huán)通測試

https://leeefpga.blog.csdn.net/article/details/138147558

三、選擇指南

-

接口

+關(guān)注

關(guān)注

33文章

9554瀏覽量

157339 -

AXI總線

+關(guān)注

關(guān)注

0文章

68瀏覽量

14772 -

Zynq

+關(guān)注

關(guān)注

10文章

631瀏覽量

49509

原文標題:ZYNQ PS與PL 數(shù)據(jù)交互方式

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

PYNQ案例(一):ZYNQ的PL與PS開發(fā)

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數(shù)據(jù)

【FPGA ZYNQ Ultrascale+ MPSOC教程】33.BRAM實現(xiàn)PS與PL交互

ZYNQ7000系列 PS、PL、AXI 、啟動流程基本概念

ZYNQ數(shù)據(jù)交互通路PS和PL的連接技術(shù)

zynq 7020 PS和zynq PL是如何通話的?

請問是否可以在同一個Zynq FPGA中從PS控制PL JTAG?

請問zynq 怎么實現(xiàn)PS與PL數(shù)據(jù)交互,然后通過UART串口打印出來?

【正點原子FPGA連載】第十四章基于BRAM的PS和PL的數(shù)據(jù)交互領航者 ZYNQ 之嵌入式開發(fā)指南

ZYNQ的ARM和FPGA數(shù)據(jù)交互——AXI交互最重要的細節(jié)

實例詳解:如何利用Zynq-7000的PL和PS進行交互?

datamover完成ZYNQ片內(nèi)PS與PL間的數(shù)據(jù)傳輸

Zynq PS / PL 第四篇:Adam Taylor MicroZed系列之 24

PS/PL之間的數(shù)據(jù)交互辦法

將Zynq PS和PL與內(nèi)存映射寄存器集成

ZYNQ PS與PL數(shù)據(jù)交互方式

ZYNQ PS與PL數(shù)據(jù)交互方式

評論