硅基異構集成和三維集成可滿足電子系統小型化高密度集成、多功能高性能集成、小體積低成本集成的需求,有望成為下一代集成電路的使能技術,是集成電路領域當前和今后新的研究熱點。硅基三維集成微系統可集成化合物半導體、CMOS、MEMS等芯片,充分發揮不同材料、器件和結構的優勢,可實現傳統組件電路的芯片化、不同節點邏輯集成電路芯片的集成化,從而提升信號處理等電子產品的性價比。梳理了晶圓鍵合裝備的工藝過程、主要廠商及市場需求、我國晶圓鍵合設備研發現狀,并展望了晶圓鍵合設備的技術發展趨勢。

0 引言

半導體與集成電路產業是面向世界科技前沿、面向經濟主戰場、面向國家重大需求的重要產業,也是近期國際經濟與科技競爭的焦點。2018年,中國成為全球半導體第一大市場,2019年,全球半導體市場銷售額達4183億美元。集成電路產業是半導體產業中最大的消費領域,多年來銷售占比重達80%以上,行業銷售收入年均增速超過20%[1]。 在摩爾定律的引導下,集成電路行業一直高速發展,晶體管特征尺寸己經從90nm向7nm邁進。然而,由于隨著晶體管特征尺寸已日益接近物理極限,量子效應和短溝道效應越來越嚴重[3-4],內部電子自發地通過源極和漏極,導致漏電流增加,進而限制了晶體管的進一步縮小。因此,按照摩爾定律的方式,通過縮小晶體管特征尺寸來提升集成電路性能、降低功耗變得越發困難。晶體管將會快速地接近約5nm的極限柵極長度,因此探索新的溝道材料和器件結構是推動IC產業繼續發展的兩條極為重要的路線[5-7]。

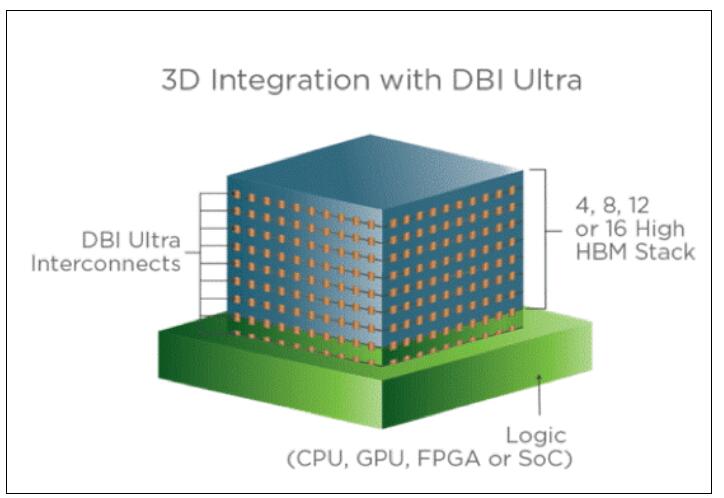

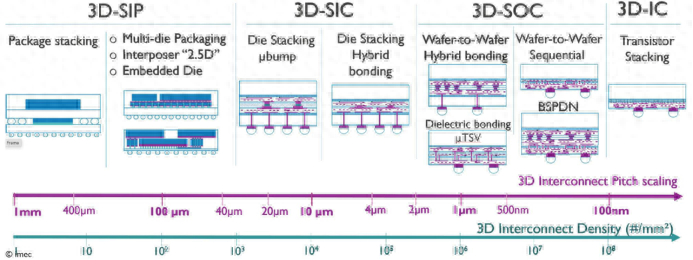

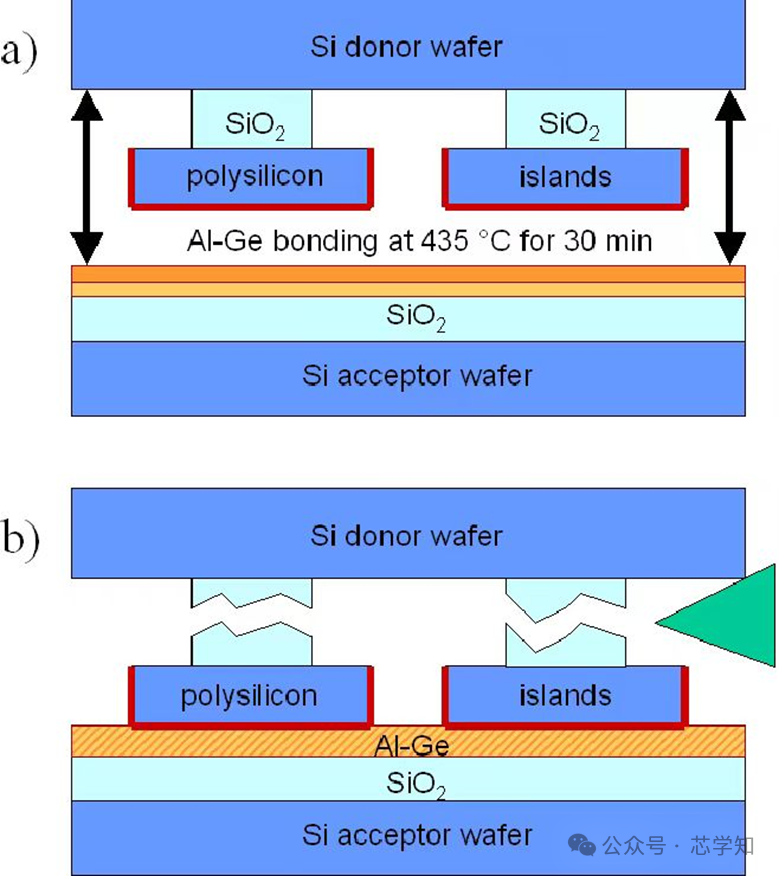

三維(Three-dimensional)集成是超越摩爾一個至關重要的研究應用方向[8-9]。3D集成的定義是將摩爾晶圓或芯片在垂直于晶圓或芯片平面方向上進行堆疊[10]。集成電路技術由二維平面向三維方向發展,該技術分段實現,首先實現幾層的三維集成,隨著時間的推移,三維集成芯片層數將會不斷增加。采用全新結構的3D集成是推動半導體行業發展的重要技術,諸如存儲器、邏輯器件、傳感器和處理器等不同類型的器件和軟件的復雜集成,以及新材料和先進的芯片堆疊技術,都要基于3D集成技術[11]。3D集成技術存在著4項挑戰,分別為晶圓級對準精度、鍵合完整性、晶圓減薄與均勻性控制以及層內(層間)互聯[12]。

隨著摩爾定律逼近材料與器件的物理極限,源于微機電系統(Micro Electro Mechanical Systems,MEMS)制造技術的晶圓級封裝鍵合技術逐漸進入集成電路制造領域,成為實現存儲器、邏輯器件、射頻器件等部件的三維堆疊同質/異質集成,進而提升器件性能和功能,降低系統功耗、尺寸與制造成本的重要技術途徑,對滿足集成電路高集密度、高功能密度和高性能集成的迫切需求,突破國內自主可控平面集成能力不足的瓶頸,實現集成電路由平面集成向三維立體集成的跨越式發展有重要的戰略價值[13]。因此,英特爾、三星、華為、高通、羅姆、臺積電等知名企業及眾多高校、科研院所均圍繞晶圓級封裝鍵合開展了設備、器件、工藝的研究。 1?晶圓鍵合設備及工藝過程

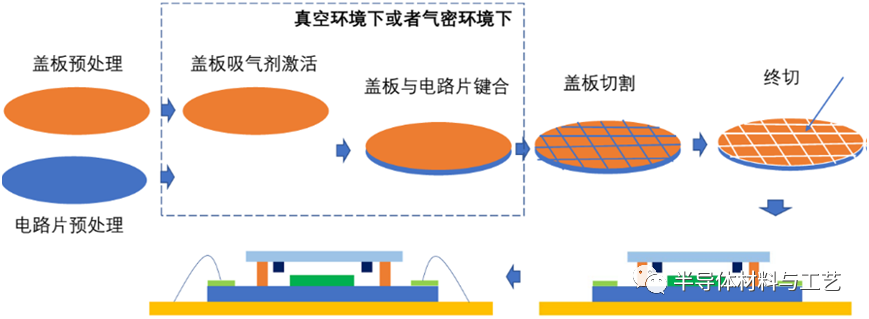

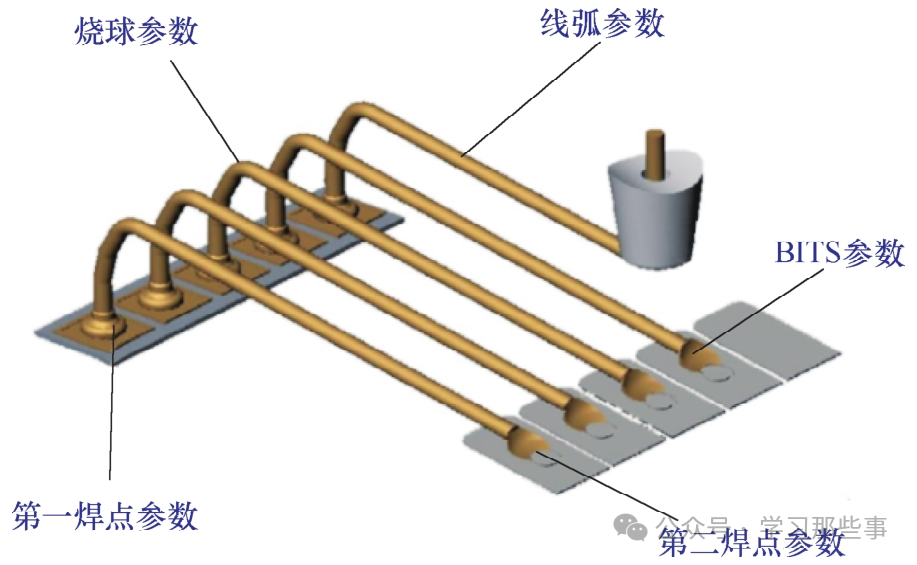

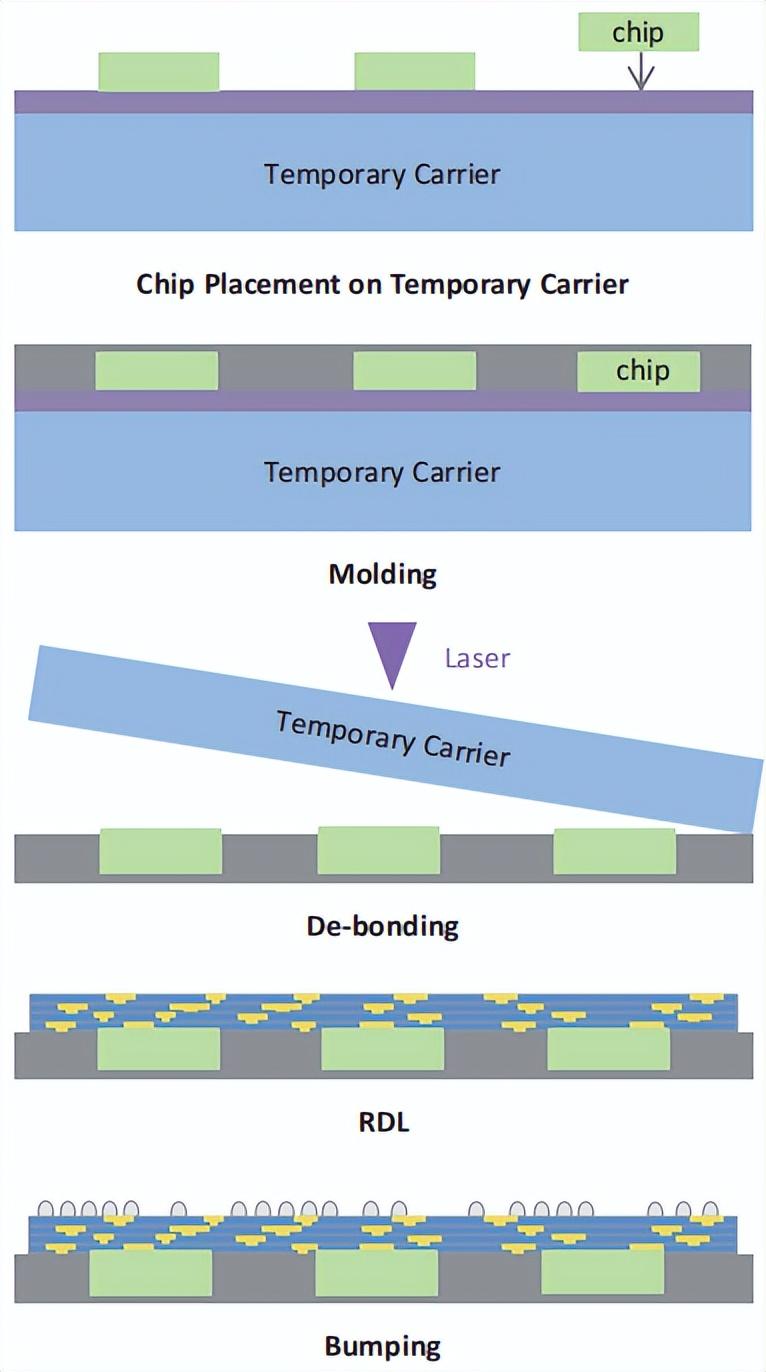

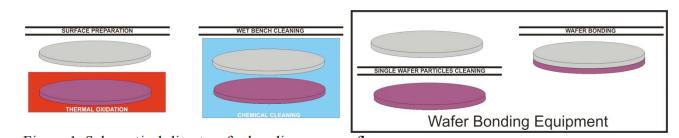

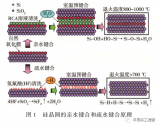

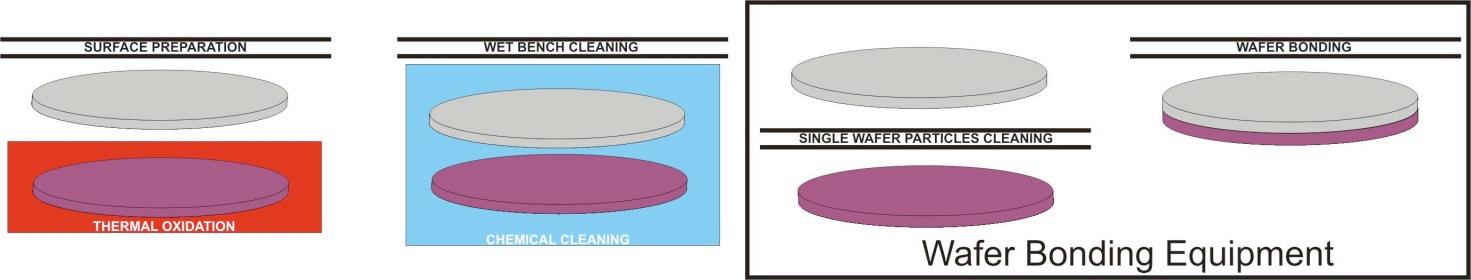

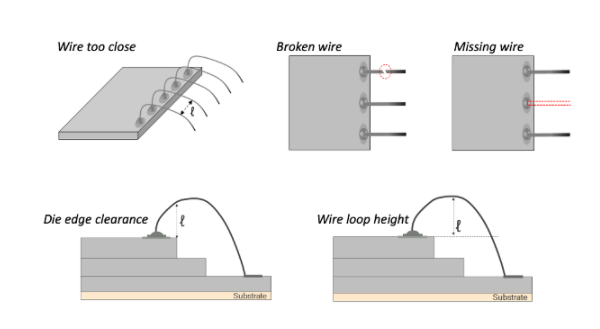

晶圓鍵合設備通過化學和物理作用將兩塊同質或異質晶片緊密地結合起來,從而實現微電子材料、光電材料及其納米等級微機電元件的電氣互聯、功能集成和器件封裝。晶圓鍵合設備廣泛應用于射頻器件、慣性器件、光電器件、信息處理器件及3D集成邏輯集成電路的先進封裝制造,對位精度、鍵合溫度均勻性、鍵合壓力范圍及控制精度對晶圓鍵合工藝具有重要影響。 如圖1所示,晶圓鍵合工藝過程為:首先將待鍵合的一組晶圓進行預處理、清洗、視覺對準,進而通過不同方法實現晶圓對的鍵合。晶片接合后,界面的原子受到外力的作用而產生反應形成共價鍵結合成一體,并使接合界面達到特定的鍵合強度,稱之為永久性鍵合。若借助粘結劑將晶片接合,也可作為臨時鍵合,通過將器件晶圓固定在承載晶圓上,可為超薄器件晶圓提供足夠的機械支撐,保證器件晶圓能夠順利安全地完成后續工藝制程,如光刻、刻蝕、鈍化、濺射、電鍍和回流焊。

圖1?晶圓鍵合及后續工藝流程

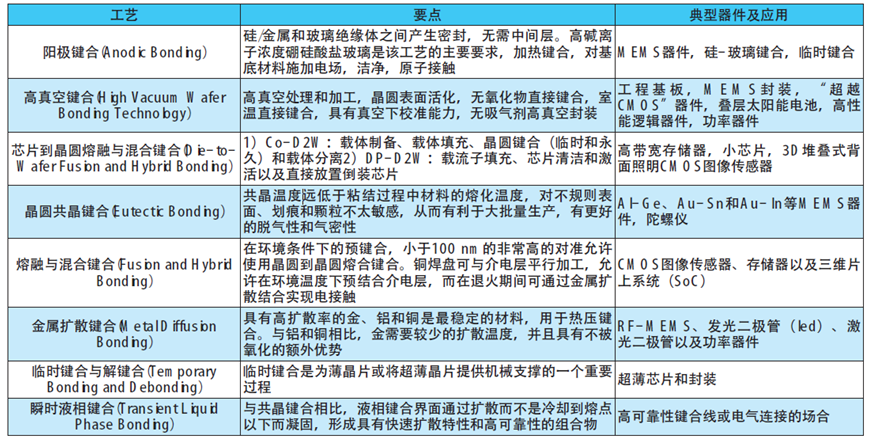

具體的晶圓鍵合工藝可按照鍵合材料、鍵合手段、應用場景分類,方法不盡相同,按照鍵合工藝對晶圓鍵合分類(見表1)。晶圓級鍵合是半導體器件物理、材料物理化學、精密機械設計、高精度自動控制等多學科交叉的科學技術領域。晶圓鍵合工藝中晶圓尺寸的擴大、芯片特征尺寸的縮小、異質材料之間的熱失配及晶格失配等重要技術問題還有待解決[14]。 國外利用超高真空Ar快速原子束表面活化鍵合工藝實現了大面積、高強度的晶圓級鍵合,但我國在大面積、高強度晶圓級鍵合理論與工藝領域能力仍有待提高。晶圓鍵合及烘烤激活對晶圓表面溫度均勻性及翹曲變形有十分嚴格的要求。溫度均勻性取決于設備結構、加熱工藝以及晶圓自身的熱物理性能,翹曲變形則受溫度均勻性、外加機械力以及晶圓自身力學性能的影響。傳統的研究多采用實驗試錯的方法,沒有將上述因素協同考慮,難以獲得優化的結構工藝參數,導致鍵合可靠性及器件良率大大下降。國際上的高水平研究團隊通常結合先進的數值仿真手段及多變量多目標優化方法,綜合考慮包含熱輻射、熱傳導在內的熱場以及包含熱應力、機械應力在內的應力場等多物理場之間的復雜耦合作用機理,開展對晶圓鍵合和烘烤激活工藝參數的協同優化,從而大大提高鍵合品質及器件良率。 表1晶圓鍵合工藝及典型器件

2?晶圓鍵合設備主要廠商

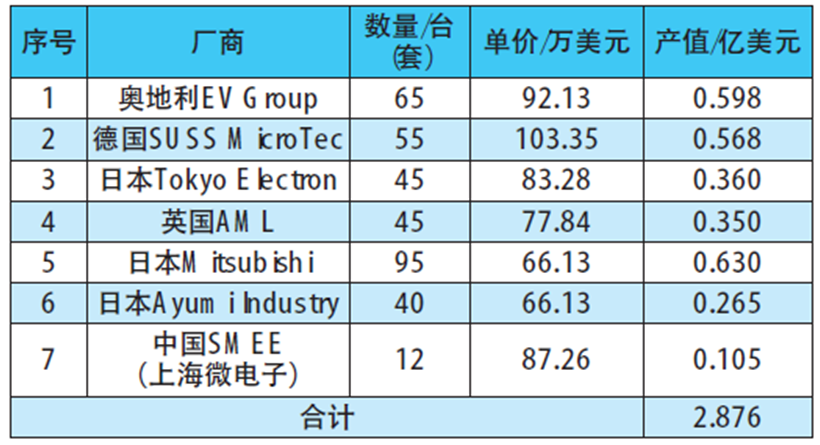

隨著先進封裝趨勢向著更復雜的異質集成、更大的封裝載體、更薄的芯片以及更小的封裝尺寸等方向發展,發達國家晶圓鍵合設備市場已比較成熟,而我國市場仍處成長階段,未來將成為全球晶圓對準設備消費增長的主要推動力。在企業不斷加大資金投入、基礎研究深度拓展和消費者認知不斷提高的基礎上,晶圓鍵合系列設備市場將迎來井噴式發展。目前,國際一流晶圓鍵合設備廠商主要包括奧地利EVG公司與德國SUSS MicroTec公司等,詳見表2。 表2 2020年晶圓鍵合主要廠商

奧地利EVG公司的主流產品,適合陽極鍵合、共晶鍵合、金屬擴散鍵合、直接鍵合、聚合物鍵合、熔融與混合鍵合和瞬時液相鍵合的小批量、半自動晶圓鍵合解決方案,如EVG510、EVG520、E V G 5 4 0?晶圓鍵合系統;也可以提供全自動、大批量、滿足3D異構集成高對準精度生產的晶圓鍵合解決方案,如EVG560、EVG GEMINI、EVGCombond、EVG Bondscale等晶圓鍵合系統;還有用于扇出封裝、晶圓減薄、3D堆疊、晶圓鍵合的臨時鍵合和晶圓解鍵合解決方案,如E V G 8 5 0?、EVG850TB、EVG850LT等晶圓臨時鍵合與解鍵合系統;晶圓對準設備由Smartview發展到Smartview3,對準精度提高到50 nm。 晶圓鍵合設備總體技術發展方向是高精度、高集成化、高可靠性、高動態、高效化的趨勢,關鍵技術指標為:對準精度≤50 nm;鍵合溫度均勻性≤±1%;最大晶圓尺寸304.8 mm(12英寸);最大鍵合壓力100 kN;最高鍵合溫度550?℃。

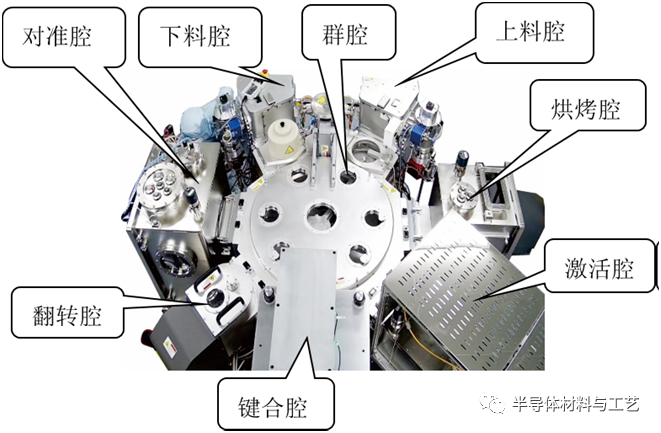

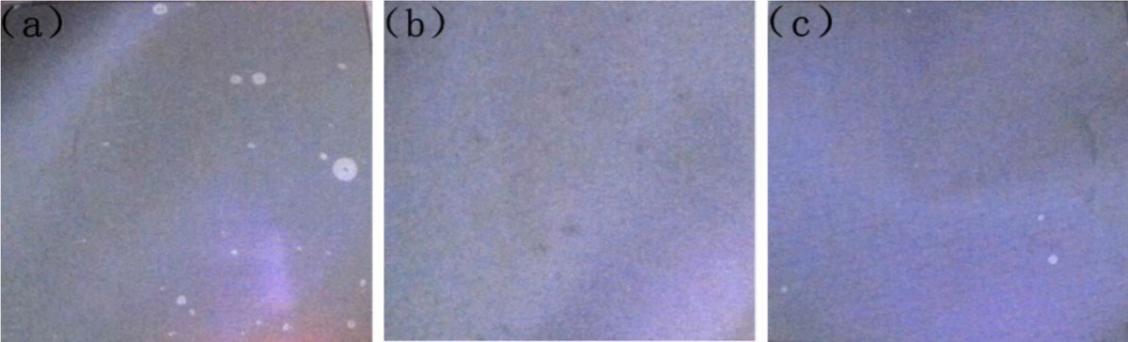

德國SUSS MicroTec擁有六十多年的歷史,是半導體行業領先的微結構工藝設備制造商,產品涵蓋光刻、涂膠/顯影、晶圓鍵合、光刻掩膜版清洗等諸多半導體、微加工相關領域。SUSS晶圓鍵合系統主要包括XB8、SB6/8Gen2、XBS200、XBS300、XBC300Gen2等系統,最大晶圓尺寸304.8 mm(12英寸),對準精度≤500 nm,能夠滿足包括共晶、直接鍵合等各種晶圓鍵合工藝需求。 國內設備起步晚,國內鍵合設備技術發展方向由手動向半自動轉換,國內沒有多模塊集成的晶圓鍵合設備,與國外設備代差距較大。上海微電子裝備(SMEE)有獨立對準、鍵合、解鍵合等設備,SWB系列晶圓鍵合設備用于有機膠鍵合、玻璃漿料鍵合、共晶鍵合、陽極鍵合等工藝。SWA系列晶圓對準設備對準精度≤±2?μm。蘇州美圖開發的陽極晶圓鍵合設備,最大鍵合壓力10~30 kN,最高溫度450?℃。中國電科2所研制真空晶圓鍵合系統對準精度≤1?μm,鍵合溫度均勻性≤±1%(FS),設備達到國內先進水平(如圖2所示)。

圖2?全自動真空晶圓鍵合系統

3?我國晶圓鍵合設備的研發現狀

晶圓鍵合設備是進入壁壘很高的產業,對于光學系統、圖像處理與識別、高精度晶圓平行移動等技術的要求極高。國內的眾多設備廠家因自身的人才、技術、設備、材料和資金等各方面因素的制約,無力進行設備持續的研究和改進,與國外同行之間的技術和實力的差距有擴大的趨勢,晶圓鍵合產品在技術性能、質量可靠性、穩定性等方面存在很大的不足。目前,國內晶圓級鍵合技術主要受限于國內器件設計與工藝、設備穩定性與精確度等領域的基礎理論與關鍵技術的發展水平。 3.1技術性能

目前國內生產的最好的設備對準精度為±2?μm,與國外設備差距較大,EVG對準精度≤50 nm。鍵合溫度均勻性規格書≤±1%(FS),實際能達到≤±0.6%。目前在晶圓級封裝行業內,臨時鍵合技術的使用已經比較成熟,但都是厚度都在100μm以上的單層硅通孔(TSV)結構,受限于臨時鍵合材料,暫不能做到更薄。臨時鍵合穩定的另一面是解鍵合和清除殘膠更加麻煩,需要更長時間去除殘膠,鍵合的穩定和解鍵合殘膠的易清潔之間的平衡,還需要更長時間去解決。國外設備自動化程度可滿足大生產線需求,國內設備差距很大。 3.2?質量可靠性

國外設備鍵合熱臺使用壽命長、密封可靠性高,加壓氣液缸、檢測傳感器、卡盤等關鍵件可靠、耐用,設備一致性、長期使用穩定性好,加熱臺互換性良好。國內設備、鍵合加熱臺等部件一致性差,穩定性不好,缺乏關鍵零部件持續攻關及工藝深度結合。 3.3研發模式及投入

我國設備行業與國外行業領軍企業的研發模式有很大不同。以半導體裝備龍頭企業AMSL為例,在全球范圍內與優勢單位、頭部企業合作,實現優勢互補、強強聯合,分布在全球的700多家供應商提供的功能模塊和單元組件貢獻了AMSL光刻設備約85%的外購成本。 AMSL能專注于自身獨特的能力優勢,集成世界范圍內最專業的制造商來設計、研發與制造***,與比利時的IMEC光刻研究中心保持著長期合作關系,依靠強大的研發實力引領市場、開拓創新,擁有龐大且涉及多學科多領域的高科技研發團隊,每年用于研發的費用數以億計。自2015年以來,AMSL的研發人數占員工總數的比例一直維持在35%左右,研發人員逐年遞增,2018年達8 500多人[15]。國內裝備研制企業與零部件生產商配合不緊密,產學研合作脫節,研究方向不專注,高端人才缺乏,研發投入不夠,缺乏長期戰略投入,造成與國外高端核心裝備的技術差距較大。?

4?晶圓鍵合設備技術發展趨勢

4.1向全自動多工藝集成方向轉換

設備由單一工藝段設備逐步全自動多工藝集成方向轉換,表現出高集成度特點。近年來半自動晶圓鍵合設備市場份額在逐漸下降,全自動晶圓鍵合設備市場份額逐年在提高。集束型晶圓鍵合設備由若干功能不同的工藝腔構成,會產生大量與工藝相關的數據,每個工藝腔內布置大量檢測不同物理量的傳感器,在設備運行期間還會產生大量數據。通過使用合適的數據處理方案處理上述海量數據,可有效地反饋至各部分設計人員,從而輔助設備設計以及器件控制方案。對集成型先進封裝鍵合設備而言,生產過程較復雜,而腔室之間處理晶圓的片數、時間也不相同,導致腔內機械手時域作業調度方案優劣在很大程度上會影響集束型設備生產效率以及設備運作流暢性,因此科學地設計集束型設備生產過程模型以及機械手調度算法對生產效率至關重要[16]。 此外,國際IC裝備和材料協會(SEMI)針對集束型裝備控制軟件(CTC)的控制軟件正向標準化、通用化控制系統發展,符合國際標準CTC的控制軟件是國際上IC裝備控制系統的通用解決方案。因此,為使晶圓鍵合設備可以進入標準化生產線,需要針對SEMI標準設計CTC軟件。

4.2向3D集成技術領域轉化

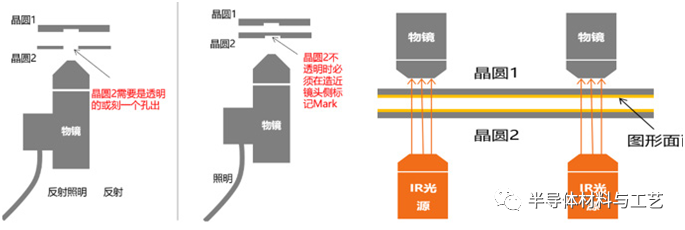

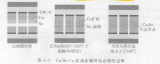

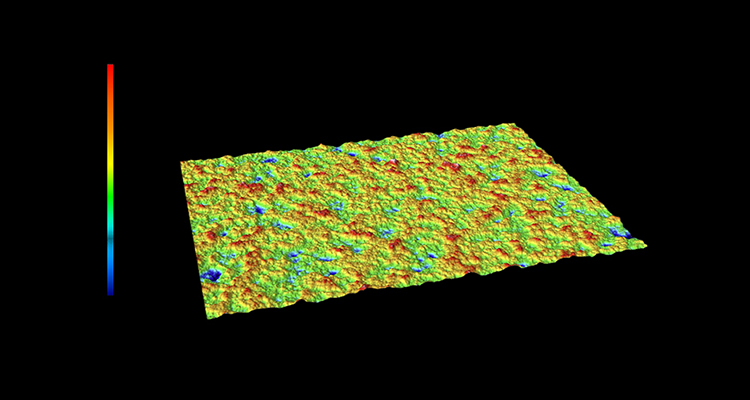

設備由MEMS領域應用轉化到3D集成技術領域,表現出高對準精度特點。大多數對準、鍵合工藝都源于微機電系統(MEMS)制造技術,但應用于3D集成的對準精度要比傳統MEMS對準精度提高5~10倍,目前設備對準精度已經達到亞微米級。實現晶圓級對準的方法有頂部對準或者底部對準(TSA/BSA)、紅外透射對準(IR)、片中間對準(ISA)/面-面對準、背對背對準(如圖3所示)。頂部對準或者底部對準采用一組物鏡,這種方法要求一片晶圓是透明的或具有一定的透光性,從上側或者下側都可以看到上下兩個晶圓的標識(Mark)點。紅外透射對準技術廣泛應用于3D IC晶圓級鍵合領域,能夠實施對Mark進行測量實時成像,多次對準,進一步提高對準精度。紅外透射對準的優點是可實時成像,多次對準;缺點是對準精度與晶圓的厚度相關,波長選擇與材質和厚度相關,并且隨著厚度增加,成像質量下降,疊層晶圓出射面的粗糙度與紅外透射對準精度也相關。背對背對準需要雙面光刻,或者背面光刻。

(a)頂部對準或者底部對準? ? ??(b)紅外透射對準

(c)片中間對準? ???(d)背對背對準

圖3?對準方式及對準示意圖

當上述方式都不滿足對準要求時,可以采用片中間對準(ISA),這種對準方式的主要缺點是需要對準的晶圓Z?方向的間距大。EV Group采用SmartView對準系統。

設備由MEMS領域應用轉化到3D集成技術領域,表現大壓力高溫度均勻性特點。鍵合臺由金屬加熱器向陶瓷加熱器轉化,進一步提高溫度均勻性及耐磨性。晶圓尺寸由203.2 mm(8英寸)轉向304.8 mm(12英寸),低溫直接鍵合增多,鍵合壓力增大至100 kN。 總之,晶圓鍵合設備在后摩爾時代表現出來高集成、高精度、大壓力高溫度均勻性、高動態和智能化的特點,晶圓鍵合設備在3D集成技術應用前景極具優勢。 5?結束語

為提高我國在先進封裝技術領域的自主研發創新能力,建議針對半導體芯片產業鏈對高質量、高可靠性先進封裝鍵合的迫切需求,開展晶圓級同質/異質封裝鍵合基礎理論及關鍵技術研究,重點探索突破封裝鍵合的界面理論與工藝優化方法、復雜精密晶圓級封裝系統設計原理與關鍵技術、高動態高精度晶圓封裝系統檢測控制理論與技術、集束型封裝復雜生產過程優化控制理論與技術等發展瓶頸,構建晶圓級先進封裝同質/異質鍵合理論與技術體系。

王成君1,2,胡北辰2,楊曉東2,武春暉2

(1 東南大學機械工程學院??2 中國電子科技集團公司第二研究所)

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論