PCB設計中如何避免串擾

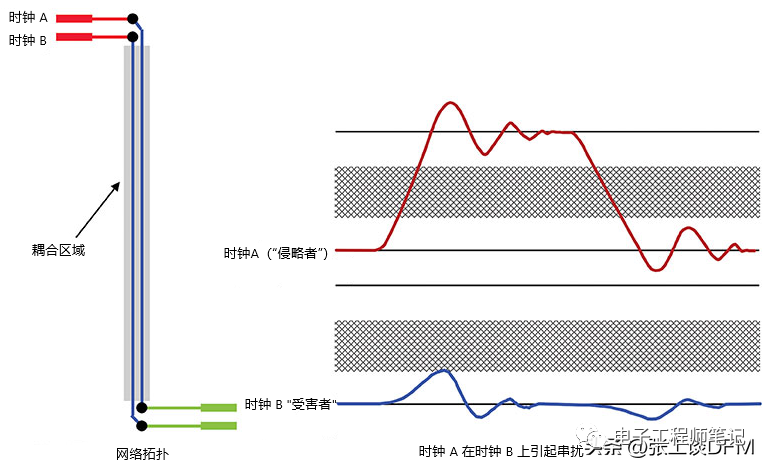

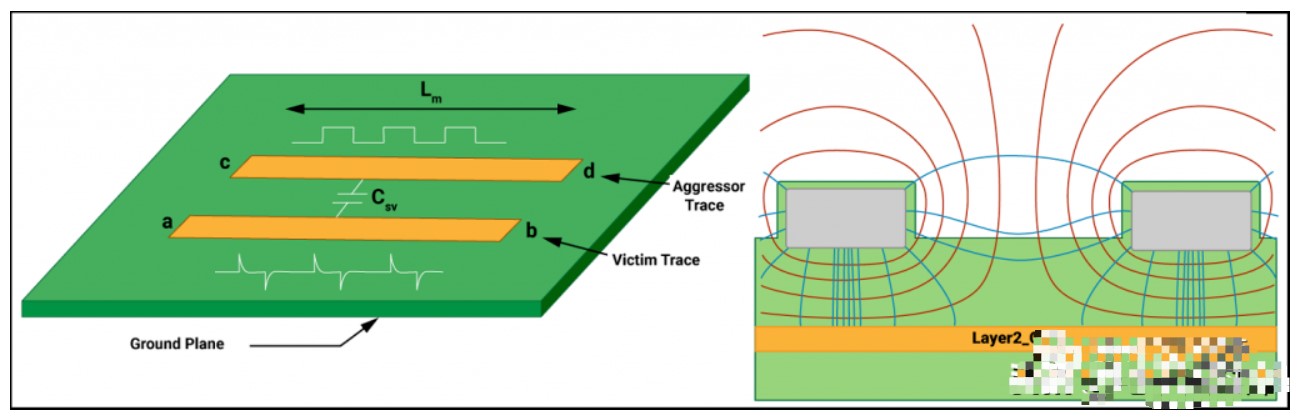

變化的信號(例如階躍信號)沿傳輸線由 A 到 B 傳播,傳輸線 C-D 上會產生耦合信

2009-03-20 14:04:17 778

778 信號完整性測量已成為開發數字系統過程中的關鍵步驟。信號完整性問題,如串擾、信號衰減、接地反彈等,在傳輸線效應也很關鍵的較高頻率下會增加。

2022-07-25 09:59:58 10535

10535

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。

2022-08-22 10:45:08 4444

4444

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。

2022-08-29 09:38:57 2560

2560

在高速PCB設計的學習過程中,串擾是一個需要大家掌握的重要概念。它是電磁干擾傳播的主要途徑,異步信號線,控制線,和I/O口走線上,串擾會使電路或者元件出現功能不正常的現象。 串擾(crosstalk

2022-09-05 18:55:08 3020

3020

因此了解串擾問 題產生的機理并掌握解決串擾的設計方法,對于工程師來說是相當重要的,如果處理不好可能會嚴重影響整個電路的效果。

2022-09-28 09:41:25 2687

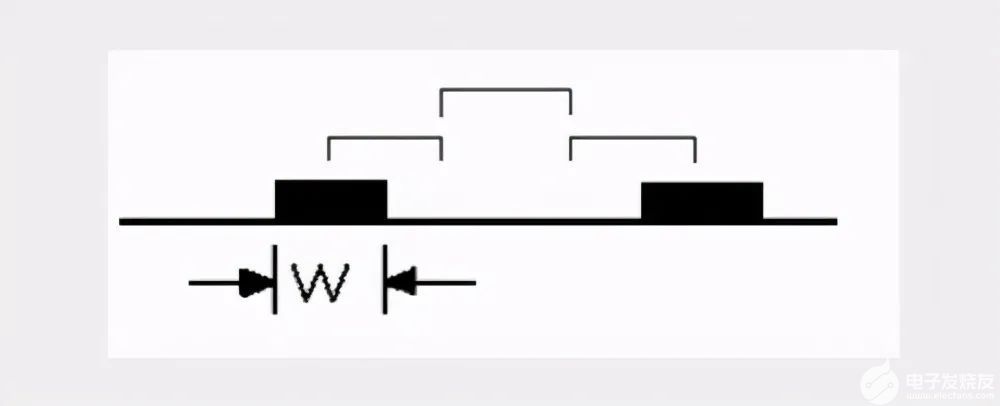

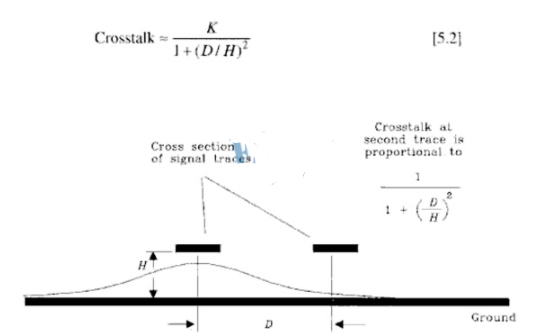

2687 我們經常聽說PCB走線間距大于等于3倍線寬時可以抑制70%的信號間干擾,這就是3W原則,信號線之間的干擾被稱為串擾,串擾是怎么形成的呢?

2023-04-18 11:06:22 2144

2144

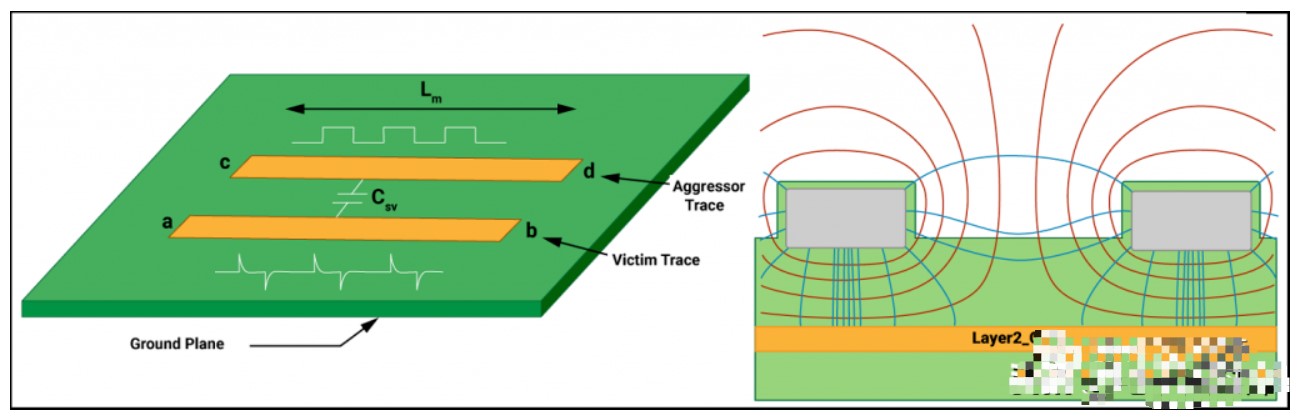

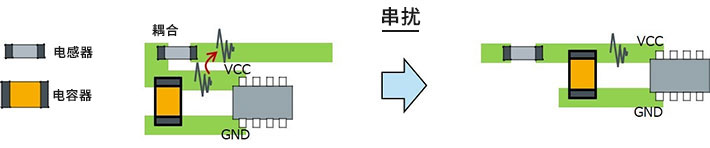

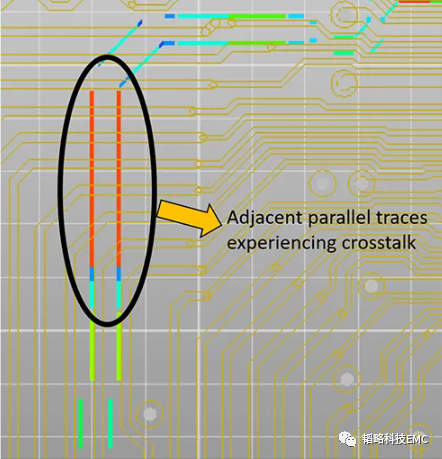

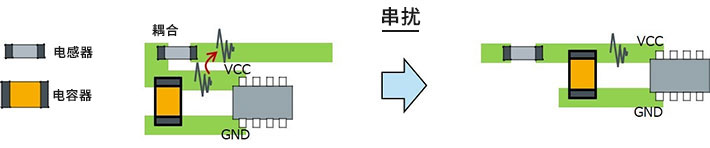

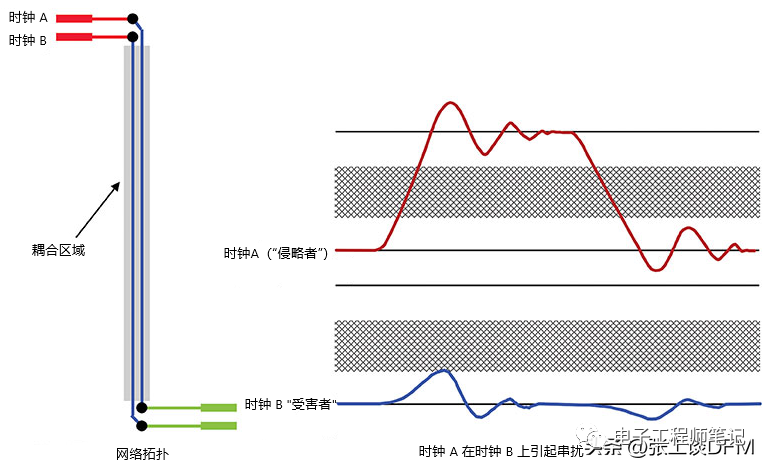

隨著科技發展和人們消費需求,現今電子設備小型化的趨勢越來越突出,印制電路板(PCB)越做越小。這導致PCB板內信號走線之間容易產生無意間耦合,這種耦合現象被稱為串擾(如圖1)。

2023-05-16 12:33:45 1008

1008

01 . 什么是串擾? ? 串擾 是 PCB 的走線之間產生的不需要的噪聲 (電磁耦合)。 串擾是 PCB 可能遇到的最隱蔽和最難解決的問題之一。最難搞的是,串擾一般都會發生在項目的最后階段,而且

2023-05-23 09:25:59 8732

8732

串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法。

2023-06-13 10:41:52 2372

2372

先來說一下什么是串擾,串擾就是PCB上兩條走線,在互不接觸的情況下,一方干擾另一方,或者相互干擾。

2023-09-11 14:18:42 2335

2335

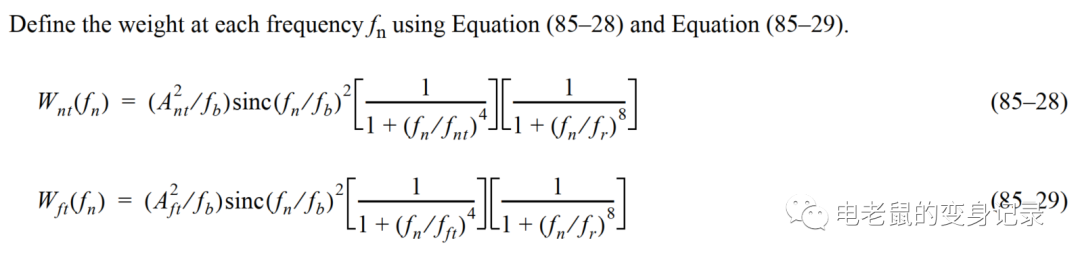

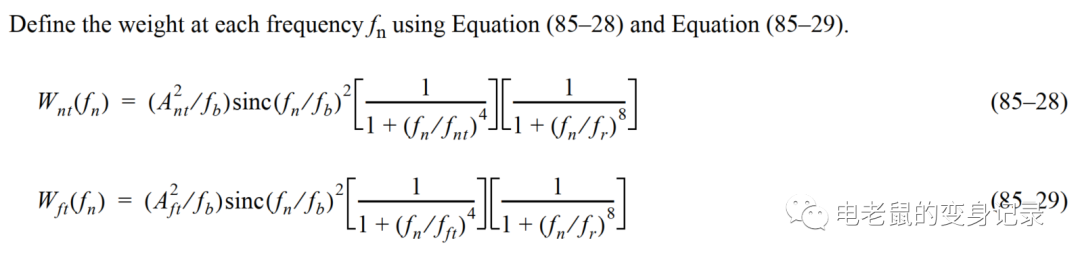

講到串擾,基礎的串擾知識比如串擾是由電場耦合和磁場耦合的共同結果啊,從串擾影響的方向來分有FEXT和NEXT這些小P就都不說了。當小P在學習一篇PCIe 5.0連接器一致性的paper里出現了ICN的字樣。

2023-10-25 14:43:22 7932

7932

PCB板上的高速信號需要進行仿真串擾嗎?

2023-04-07 17:33:31

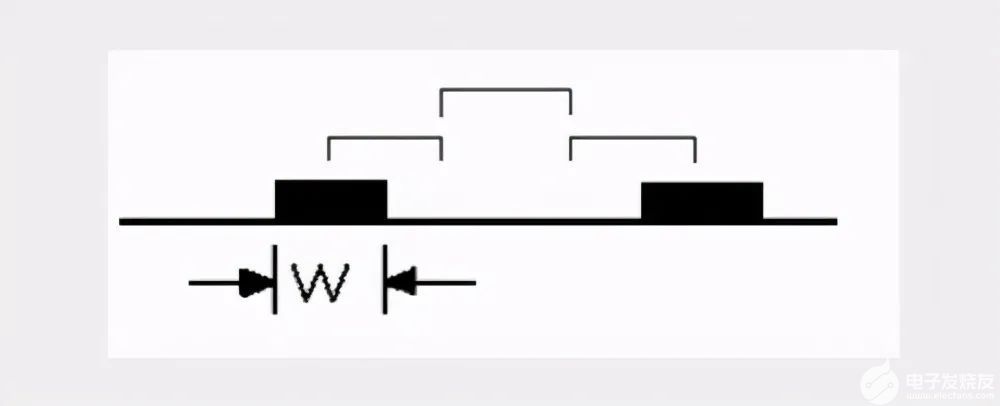

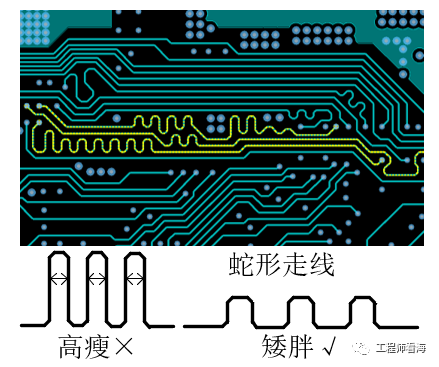

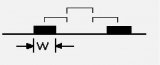

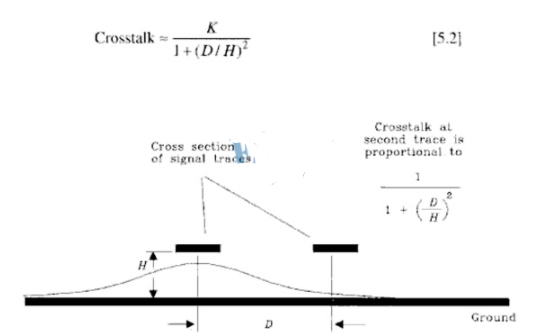

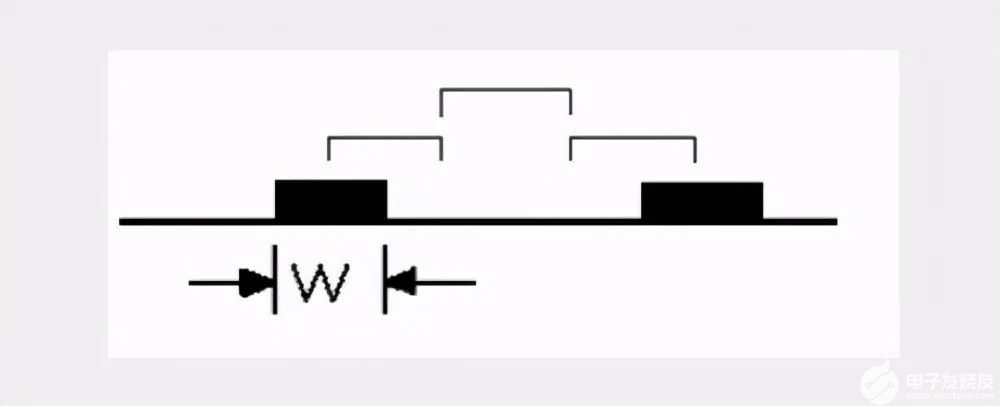

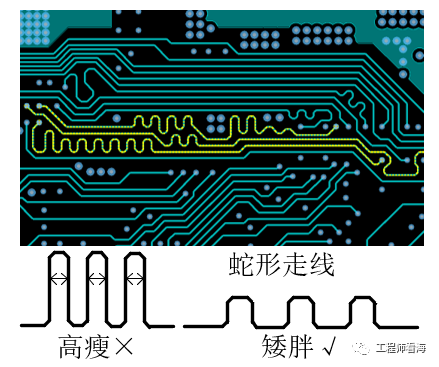

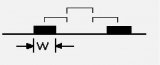

?對串擾有一個量化的概念將會讓我們的設計更加有把握。1.3W規則在PCB設計中為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持大部分電場不互相干擾,這就是3W規則。如(圖1

2014-10-21 09:53:31

作者:一博科技SI工程師陳德恒3. 仿真實例在ADS軟件中構建如下電路: 圖2圖2為微帶線的近端串擾仿真圖,經過Allegro中的Transmission line Calculators軟件對其疊

2014-10-21 09:52:58

PCB設計中如何處理串擾問題 變化的信號(例如階躍信號)沿

2009-03-20 14:04:47

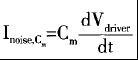

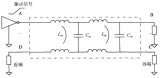

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且

2018-08-29 10:28:17

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號

2020-06-13 11:59:57

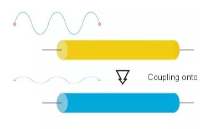

。兩根線(也包括PCB的薄膜布線)獨立的情況下,相互間應該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發干擾。所以,串擾也可以理解為感應噪聲

2018-11-29 14:29:12

在選擇模數轉換器時,是否應該考慮串擾問題?ADI高級系統應用工程師Rob Reeder:“當然,這是必須考慮的”。串擾可能來自幾種途徑從印刷電路板(PCB)的一條信號鏈到另一條信號鏈,從IC中的一個

2019-02-28 13:32:18

。兩根線(也包括PCB的薄膜布線)獨立的情況下,相互間應該不會有電氣信號和噪聲等的影響,但尤其是兩根線平行的情況下,會因存在于線間的雜散(寄生)電容和互感而引發干擾。所以,串擾也可以理解為感應噪聲

2019-03-21 06:20:15

串擾的概念是什么?到底什么是串擾?

2021-03-05 07:54:17

什么是串擾?互感和互容電感和電容矩陣串擾引起的噪聲

2021-02-05 07:18:27

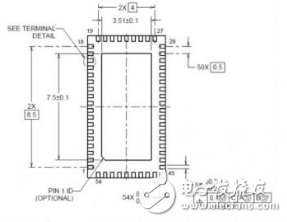

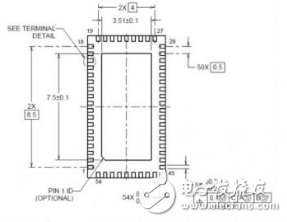

。對于8Gbps及以上的高速應用更應該注意避免此類問題,為高速數字傳輸鏈路提供更多裕量。本文針對PCB設計中由小間距QFN封裝引入串擾的抑制方法進行了仿真分析,為此類設計提供參考。那么,什么是小間距QFN封裝PCB設計串擾抑制呢?

2019-07-30 08:03:48

相互作用時就會產生。在數字電路系統中,串擾現象相當普遍,串擾可以發生在芯片內核、芯片的封裝、PCB板上、接插件上、以及連接線纜上,只要有臨近的銅互連鏈路,就存在信號間的電磁場相互作用,從而產生串擾現象

2016-10-10 18:00:41

在設計fpga的pcb時可以減少串擾的方法有哪些呢?求大神指教

2023-04-11 17:27:02

的誤碼源的重要調試手段。S 參數的概念是源于對互連器件或系統的微波屬性的描述,提供了描述從音頻范圍到毫米波頻率范圍的應用中存在的串擾的最直觀方法。畢竟S參數矩陣中的每個參量事實上都是正弦信號從互連

2019-07-08 08:19:27

變小,布線密度加大等都使得串擾在高速PCB設計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發,導致系統無法正常工作。設計者必須了解串擾產生的機理,并且在設計中應用恰當的方法

2018-09-11 15:07:52

在嵌入式系統硬件設計中,串擾是硬件工程師必須面對的問題。特別是在高速數字電路中,由于信號沿時間短、布線密度大、信號完整性差,串擾的問題也就更為突出。設計者必須了解串擾產生的原理,并且在設計時應用恰當的方法,使串擾產生的負面影響降到最小。

2019-11-05 08:07:57

。對于8Gbps及以上的高速應用更應該注意避免此類問題,為高速數字傳輸鏈路提供更多裕量。本文針對PCB設計中由小間距QFN封裝引入串擾的抑制方法進行了仿真分析,為此類設計提供參考。二、問題分析在PCB

2018-09-11 11:50:13

8Gbps及以上的高速應用更應該注意避免此類問題,為高速數字傳輸鏈路提供更多裕量。本文針對PCB設計中由小間距QFN封裝引入串擾的抑制方法進行了仿真分析,為此類設計提供參考。

2021-03-01 11:45:56

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產生干擾的數字部分盡量隔離,使易產生干擾的數字信號走線上盡量靠近交流地,使高頻信號獲得較好的回流路徑。盡量減小信號回路的面積,降低地線的阻抗,采用多點接地的方法。使用多層板將電源與地作為獨立的一層來處理。合理的走線拓樸結構-盡量采用菊花輪式走線

2009-06-18 07:52:34

、電路板的設計、串擾的模式(反向還是前向)以及干擾線和***擾線兩邊的端接情況。下文提供的信息可幫助讀者加深對串擾的認識和研究,從而減小串擾對設計的影響。 研究串擾的方法 為了盡可能減小PCB設計中的串

2018-11-27 10:00:09

在PCB電路設計中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設計最常用的軟件等問題,本文我們講一下關于怎么解決PCB設計中消除串擾的問題,快跟隨小編一起趕緊學習下。 串擾是指在一根

2020-11-02 09:19:31

高速PCB串擾分析及其最小化 1.引言 &

2009-03-20 13:56:06

可能出現在電路板、連接器、芯片封裝以及線纜上。本文將剖析在高速PCB板設計中信號串擾的產生原因,以及抑制和改善的方法。?

?????? 串擾的產生

?????? 串擾是指信號在傳輸通道

2018-08-28 11:58:32

方向的間距時,就要考慮高速信號差分過孔之間的串擾問題。順便提一下,高速PCB設計的時候應該盡可能最小化過孔stub的長度,以減少對信號的影響。如下圖所1示,靠近Bottom層走線這樣Stub會比較短。或者

2020-08-04 10:16:49

高速PCB設計中的串擾分析與控制:物理分析與驗證對于確保復雜、高速PCB板級和系統級設計的成功起到越來越關鍵的作用。本文將介紹在信號完整性分析中抑制和改善信號串擾的

2009-06-14 10:02:38 0

0 高速PCB 串擾分析及其最小化喬 洪(西南交通大學 電氣工程學院 四川 成都 610031)摘要:技術進步帶來設計的挑戰,在高速、高密度PCB 設計中,串擾問題日益突出。本文就串

2009-12-14 10:55:22 0

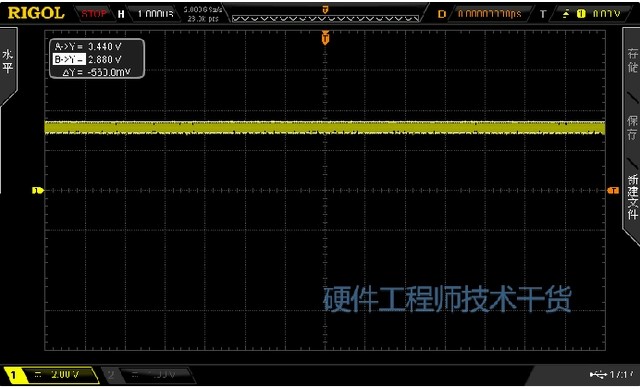

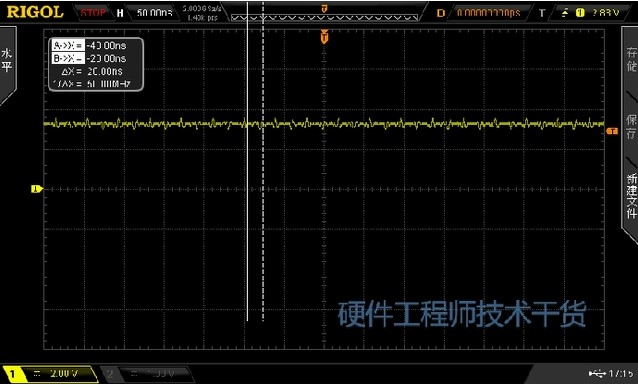

0 用于PCB 品質驗證的時域串擾測量法作者:Tuomo Heikkil關鍵詞:TDS8000B,串擾,采樣示波器,PCB,通信信號分析儀摘要:本文討論了串擾的組成,并展示了如何利用泰克的TDS8000

2010-02-07 16:40:00 37

37 高速PCB串擾分析及其最小化

1.引言 隨著電子產品功能的日益復雜和性能的提高,印刷電路

2009-03-20 13:55:35 888

888

分析了在超深亞微米階段,串擾對高性能芯片設計的影響,介紹了消除串擾影響的方法。 關鍵詞:串擾,布線,關鍵路徑,

2009-05-05 20:59:16 1434

1434

用于PCB品質驗證的時域串擾測量法分析

本文討論了串擾的組成,并向讀者展示了如何利用泰克的TDS8000B系列采樣示波器或CSA8000

2009-11-16 16:51:41 932

932 對高速PCB中的微帶線在多種不同情況下進行了有損傳輸的串擾仿真和分析, 通過有、無端接時改變線間距、線長和線寬等參數的仿真波形中近端串擾和遠端串擾波形的直觀變化和對比,

2011-11-21 16:53:02 0

0 PCB印制線間串擾的MATLAB分析理論分析給實際布線做參考依據

2015-12-08 10:05:46 0

0 pcb設計相關知識,關于平行走線串擾的東東

2016-01-21 11:03:50 0

0 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號沿

2017-11-29 14:13:29 0

0 變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且信號沿

2018-01-26 11:03:13 6105

6105

本文對高速差分過孔之間的產生串擾的情況提供了實例仿真分析和解決方法。 高速差分過孔間的串擾 對于板厚較厚的PCB來說,板厚有可能達到2.4mm或者3mm。以3mm的單板為例,此時一個通孔在PCB上Z方向的長度可以達到將近118mil。

2018-03-20 14:44:00 1793

1793

如果不同層的信號存在干擾,那么走線時讓這兩層走線方向垂直,因為相互垂直的線,電場和磁場也是相互垂直的,可以減少相互間的串擾。

2019-05-01 09:28:00 3985

3985 信號頻率變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串擾在高速PCB設計中的影響顯著增加。串擾問題是客觀存在,但超過一定的界限可能引起電路的誤觸發,導致系統無法正常工作。設計者必須了解串擾產生的機理,并且在設計中應用恰當的方法,使串擾產生的負面影響最小化。

2019-05-29 14:09:48 1271

1271

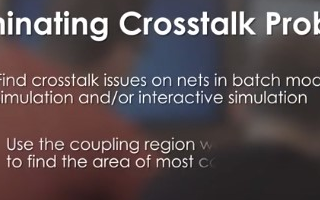

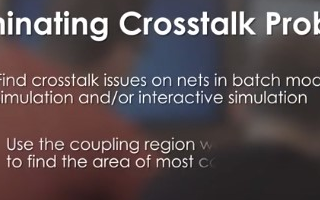

使用 HyperLynx? 可以輕松地查找并修復 PCB 串擾問題。從 PCB Layout 導出設計后,以批量模式和/或交互模式運行仿真,從而確定潛在的串擾問題。利用 BoardSim 的耦合區

2019-05-16 06:30:00 4186

4186

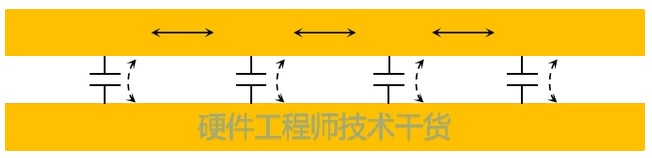

串擾(Crosstalk)是指信號線之間由于互容(信號線之間的空氣介質相當于容性負載),互感(高頻信號的電磁場相互耦合)而產生的干擾,由于這種耦合的存在,當一些信號電平發生變化的時候,在附近的信號線上就會感應出電壓(噪聲),在電路設計中,抑制串擾最簡單的方法就是在PCB Layout中遵循3W原則。

2019-06-22 09:32:29 3297

3297 PCB布局上的串擾可能是災難性的。如果不糾正,串擾可能會導致您的成品板完全無法工作,或者可能會受到間歇性問題的困擾。讓我們來看看串擾是什么以及如何減少PCB設計中的串擾。

2019-07-25 11:23:58 3989

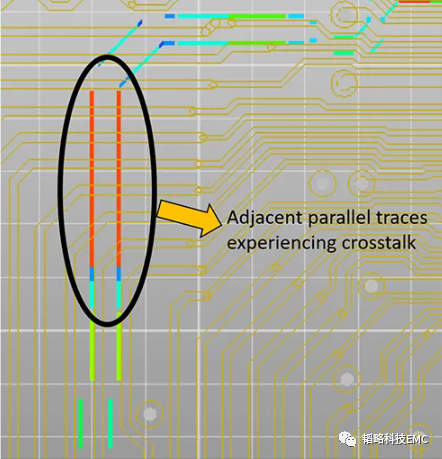

3989 串擾(CrossTalk)是指PCB上不同網絡之間因較長的平行布線引起的相互干擾,主要是由于平行線間的分布電容和分布電感的作用。

2019-08-14 08:42:30 6934

6934

今天該聊聊——串擾!

2019-08-14 09:12:23 25734

25734

串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法:

2019-08-14 11:50:55 20421

20421 在實際PCB設計中,3W規則并不能完全滿足避免串擾的要求。

2019-08-19 15:10:14 8071

8071 耦合電感電容產生的前向串擾和反向串擾同時存在,并且大小幾乎相等,這樣,在受害網絡上的前向串擾信號由于極性相反,相互抵消,反向串擾極性相同,疊加增強。串擾分析的模式通常包括默認模式,三態模式和最壞情況模式分析。

2019-09-19 14:39:54 1448

1448 PCB串擾問題可以很容易地定位和固定使用HyperLynx?墊專業或墊+標準。從PCB布局出口你的設計之后,在批處理模式運行模擬和/或交互模式來識別潛在的串擾問題。沃克BoardSim耦合地區使您能

2019-10-16 07:10:00 3786

3786 串擾在電路板設計中無可避免,如何減少串擾就變得尤其重要。在前面的一些文章中給大家介紹了很多減少串擾和仿真串擾的方法。

2020-03-07 13:30:00 4390

4390 8Gbps及以上的高速應用更應該注意避免此類問題,為高速數字傳輸鏈路提供更多裕量。本文針對PCB設計中由小間距QFN封裝引入串擾的抑制方法進行了仿真分析,為此類設計提供參考。

2020-10-19 10:42:00 0

0 高速PCB設計中,信號之間由于電磁場的相互耦合而產生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可能引發電路誤動作從而導致系統無法正常工作,解決PCB串擾問題可以從以下幾個方面考慮。

2020-07-19 09:52:05 2820

2820 PCB設計師之所以關心串擾這一現象,是因為串擾可能造成以下性能方面的問題:噪音電平升高;有害尖峰突波;數據邊沿抖動;意外的訊號反射。

2020-09-09 13:44:30 2223

2223 串擾是高速 PCB 設計人員存在的基礎之一。市場需要越來越小和更快的電路板,但是兩條平行走線或導體放置在一起的距離越近,一條走線上產生的電磁場干擾另一條走線的機會就越大。 在本文中,我們將介紹串擾

2020-09-16 22:59:02 3130

3130 當電路板上出現串擾時,電路板可能無法正常工作,并且在那里也可能會丟失重要信息。為了避免這種情況, PCB 設計人員的最大利益在于找到消除其設計中潛在串擾的方法。讓我們談談串擾和一些不同的設計技術

2020-09-19 15:47:46 3330

3330 您可能會發現布局和布線會因攻擊者的蹤跡而產生強烈的串擾。 那么,在設計中哪里可以找到串擾,以及在PCB中識別出不良走線的最簡單方法是什么?您可以使用全波場求解器,但是可以在PCB設計軟件中使用更簡單的分析功能來識別和抑

2021-01-13 13:25:55 3419

3419 1、 層疊設計與同層串擾 很多時候,串擾超標的根源就來自于層疊設計。也就是我們第一篇文章說的設計上先天不足,后面糾正起來會比較困難。 講到層疊對串擾的影響,這里有另一張圖片,和上文提到的參考平面

2021-04-09 17:21:57 5483

5483

文章——串擾溯源。 提到串擾,防不勝防,令人煩惱。不考慮串擾,仿真波形似乎一切正常,考慮了串擾,信號質量可能就讓人不忍直視了,于是就出現了開頭那驚悚的一幕。下面就來說說串擾是怎么產生的。 所謂串擾,是指有害信號從一

2021-03-29 10:26:08 4155

4155 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2021-01-23 08:19:24 16

16 為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾,稱為3W規則。如要達到98%的電場不互相干擾,可使用10W的間距。

2021-03-11 14:22:38 3563

3563 電子發燒友網為你提供PCB小間距QFN封裝引入串擾的抑制方法資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-31 08:52:17 11

11 串擾的危害:

降低板內信號完整性

時鐘或者信號延遲

產生過沖電壓和突變電流

造成芯片邏輯功能紊亂

2022-07-07 10:35:01 1287

1287 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

2022-08-15 09:32:06 11704

11704 串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。串擾也可以理解為感應噪聲。

2022-09-14 09:49:55 3781

3781

小間距QFN封裝PCB設計串擾抑制分析

2022-11-04 09:51:54 2

2 在硬件系統設計中,通常我們關注的串擾主要發生在連接器、芯片封裝和間距比較近的平行走線之間。但在某些設計中,高速差分過孔之間也會產生較大的串擾,本文對高速差分過孔之間的產生串擾的情況提供了實例仿真分析和解決方法。

2022-11-07 11:20:35 2558

2558 這之前作為使用電感的降噪對策,介紹了電感和鐵氧體磁珠、共模濾波器。本文將主要介紹PCB板布局相關的注意事項。串擾:串擾是因電路板布線間的雜散電容和互感,噪聲與相鄰的其他電路板布線耦合,這在“何謂串擾”中已經介紹過。

2023-02-15 16:12:05 2138

2138

串擾是 PCB 的走線之間產生的不需要的噪聲 (電磁耦合)。

2023-05-22 09:54:24 5605

5605

當信號通過電纜發送時,它們面臨兩個主要的通信影響因素:EMI和串擾。EMI和串擾嚴重影響信噪比。通過容易產生EMI 和串擾的電纜發送關鍵數據是有風險的。下面,讓我們來看看這兩個問題。

2023-07-06 10:07:03 3408

3408 串擾是 PCB 的走線之間產生的不需要的噪聲(電磁耦合)。

2023-07-20 09:57:08 3937

3937

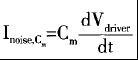

空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-08-21 14:26:46 700

700 pcb上的高速信號需要仿真串擾嗎? 在數字電子產品中,高速信號被廣泛應用于芯片內部和芯片間的數據傳輸。這些信號通常具有高帶寬,并且需要在特定的時間內準確地傳輸數據。然而,在高速信號傳輸的過程中,會出

2023-09-05 15:42:31 1458

1458 能引路誤動作從而導致系統無法正常工作。接下來深圳PCBA公司為大家分享高速PCB設計布線解決信號串擾的方法。 PCB設計布線解決信號串擾的方法 一、 在可能的情況下降低信號沿的變換速率 通常在器件的時候,在滿足設計規范的同時盡量選擇慢速的器

2023-10-19 09:51:44 2513

2513 雙絞線的串擾就是其中一個線對被相鄰的線對的信號串進來所干擾就是串擾。串擾本身是消除不了的,但只要控制在標準所要求以內就不會對網絡傳輸產生大的影響。

2023-11-01 10:10:37 2314

2314

如何減少PCB板內的串擾

2023-11-24 17:13:43 1382

1382

空間中耦合的電磁場可以提取為無數耦合電容和耦合電感的集合,其中由耦合電容產生的串擾信號在受害網絡上可以分成前向串擾和反向串擾Sc,這個兩個信號極性相同;由耦合電感產生的串擾信號也分成前向串擾和反向串擾SL,這兩個信號極性相反。

2023-12-28 16:14:19 718

718

在PCB設計過程中,串擾(Crosstalk)是一個需要重點關注的問題,因為它會導致信號質量下降,甚至可能導致數據丟失。本文將詳細介紹PCB中的串擾機制。 耦合 耦合是指兩條信號線之間的磁場和電場

2024-01-17 14:33:20 1136

1136

一些方法盡量降低串擾的影響。那么減少串擾的方法有哪些呢? 檢查靠近 I/O 網絡的關鍵網絡 檢查與I/O線相關的關鍵網絡的布線非常重要,因為這些線容易產生噪聲,這些噪聲可能會通過它們離開或進入電路板并與PCB連接,從而耦合到電路板內部或外部的世界,以及其他系統

2024-01-17 15:02:12 3258

3258

PCB產生串擾的原因及解決方法? PCB(印刷電路板)是電子產品中非常重要的組成部分,它連接著各種電子元件,并提供電氣連接和機械支撐。在 PCB 設計和制造過程中,串擾是一個常見的問題,它可

2024-01-18 11:21:55 3085

3085 在PCB設計中,如何避免串擾? 在PCB設計中,避免串擾是至關重要的,因為串擾可能導致信號失真、噪聲干擾及功能故障等問題。 一、了解串擾及其原因 在開始討論避免串擾的方法之前,我們首先需要

2024-02-02 15:40:30 2902

2902 電路布線常會有串擾的風險,最后簡單說明幾個減小串擾的方法,常見增大走線間距、使兩導體的有串擾風險的區域最小化、相鄰層走線時傳輸線互相彼此垂直、降低板材介電常數(確保阻抗控制)、內層布線(減小遠程串擾)... 等。

2024-03-07 09:30:57 2437

2437

電子發燒友網站提供《緩解ADC存儲器串擾的方法.pdf》資料免費下載

2024-09-06 10:15:03 3

3 改善串擾的設計方法據說有兩種:很多人知道的方法:信號線之間通過“包地”改善串擾……幾乎只有高速先生知道的方法:信號線之間通過“割地”改善串擾……

2024-11-11 17:26:11 822

822

在高速PCB設計中,信號完整性、串擾、信號損耗等問題直接影響電路板的性能穩定性。隨著5G通信、服務器、高速計算、汽車電子等行業對高頻、高速信號傳輸的需求增加,如何優化PCB布線以降低**信號衰減

2025-03-21 17:33:46 781

781

電子發燒友App

電子發燒友App

評論