1、什么是串擾

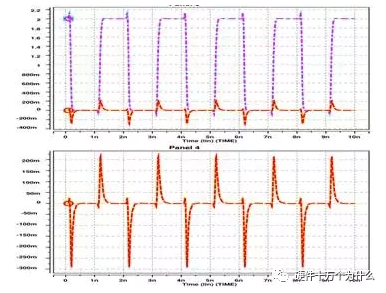

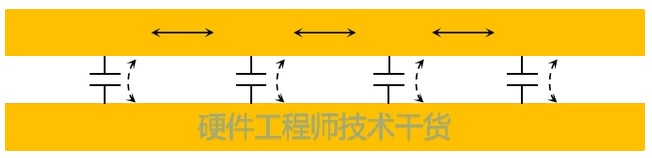

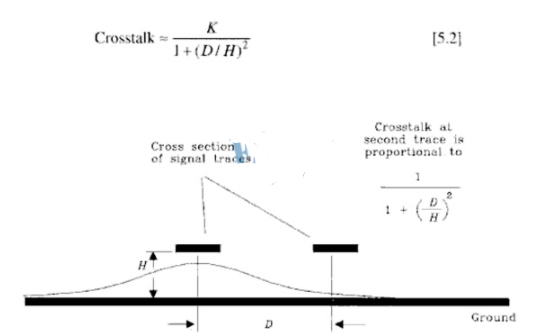

串擾是兩條信號線之間的耦合、信號線之間的互感和互容引起線上的噪聲。容性耦合引發耦合電流,而感性耦合引發耦合電壓。PCB板層的參數、信號線間距、驅動端和接收端的電氣特性及線端接方式對串擾都有一定的影響。

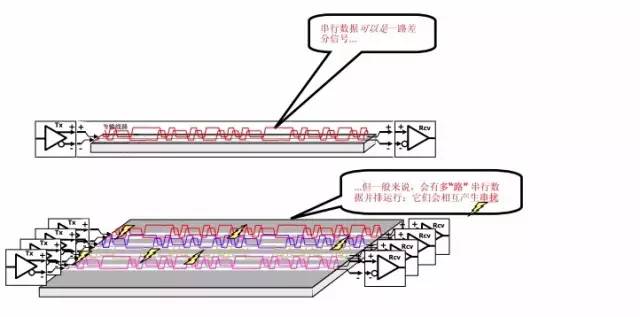

串擾是信號完整性中最基本的現象之一,在板上走線密度很高時串擾的影響尤其嚴重。我們知道,線性無緣系統滿足疊加定理,如果受害線上有信號的傳輸,串擾引起的噪聲會疊加在受害線上的信號,從而使其信號產生畸變。

2、串擾是怎么引起的?

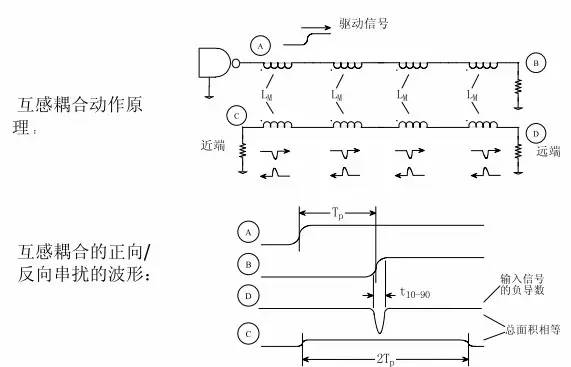

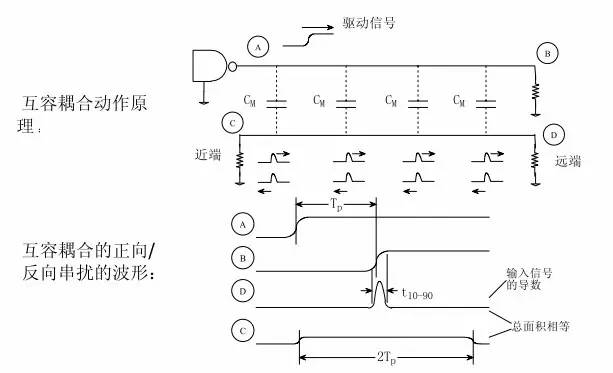

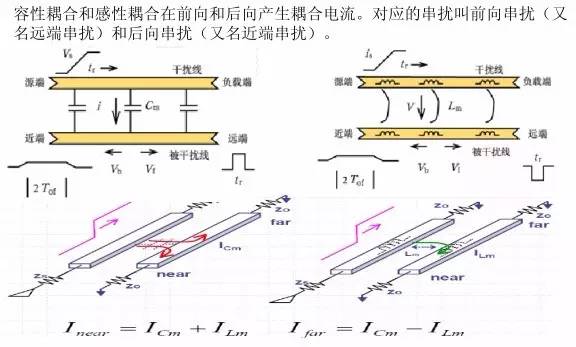

串擾是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。

串擾是指當信號在傳輸線上傳播時,因電磁耦合對相鄰的傳輸線產生的不期望的電壓噪聲。

容性耦合是由于干擾源(Aggressor)上的電壓變化在被干擾對象(Victim)上

引起感應電流從而導致的電磁干擾;

而感性耦合則是由于干擾源上的電流變化產生的磁場在被干擾對象上引起感應電壓從而導致的電磁干擾。因此,信號通過一導體時會在相鄰的導體上引起兩類不同的噪聲信號:容性耦合信號和感性耦合信號。

感性耦合:

容性耦合:

3、降低串擾有哪些方法?

當兩個網絡靠近時,一個網絡的電流變化會引起另外一個網絡的電流變化,即產生串擾。也就是兩個網絡之間的電磁場耦合產生。串擾只在上升、下降沿電流變化時產生。

降低串擾的方法有:

1、選擇慢變化邊沿信號的器件。

2、選擇輸出擺幅和電流小的器件。

3、為了減少PCB上的線間耦合,可以采取:

(1)加大電源地層與信號層間距;

(2)提高相鄰信號層間距;

(3)減少并行走線長度;

(4)增加線間距抑制;

(5)地線隔離

(6)在受害線上采用匹配技術;

(7)關鍵信號線走STRIPLINE

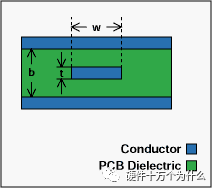

帶狀線:走在內層(stripline/double stripline),埋在PCB內部的帶狀走線,如下圖所示

藍色部分是導體,綠色部分是PCB的絕緣電介質,stripline是嵌在兩層導體之間的帶狀導線。

因為stripline是嵌在兩層導體之間,所以它的電場分布都在兩個包它的導體(平面)之間,不會輻射出去能量,也不會受到外部的輻射干擾。但是由于它的周圍全是電介質(介電常數比1大),所以信號在stripline 中的傳輸速度比在microstrip line中慢!

審核編輯:湯梓紅

-

pcb

+關注

關注

4411文章

23913瀏覽量

425333 -

電流

+關注

關注

40文章

7218瀏覽量

141450 -

串擾

+關注

關注

4文章

196瀏覽量

27861

原文標題:串擾

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

淺談PCB串擾及降低方法

串擾是怎么引起的 降低串擾有哪些方法

串擾是怎么引起的 降低串擾有哪些方法

評論