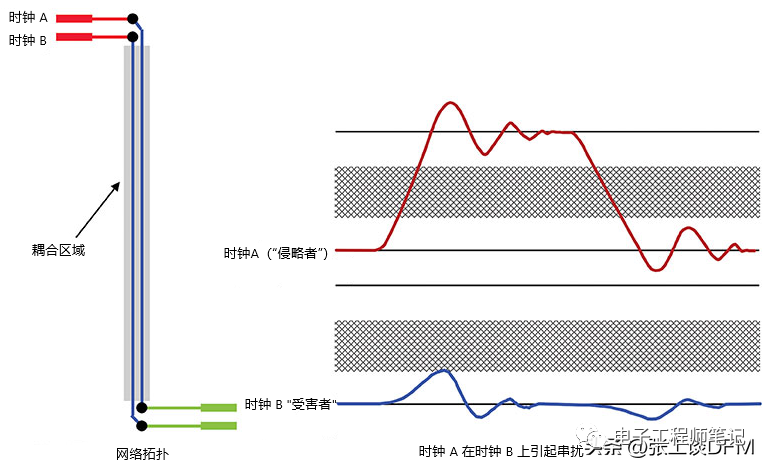

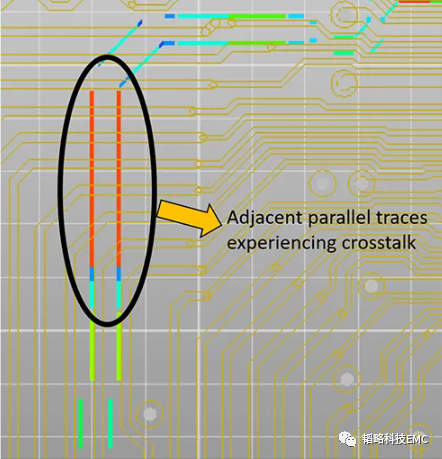

串擾是指一個信號在傳輸時,因電磁耦合等原因,對相鄰的傳輸線產生不期望的影響,在被干擾信號表現為被注入了一定的耦合電壓和耦合電流。過大的串擾可能引起電路的誤觸發,導致系統無法正常工作。

電子產品的發展,朝著小體積、高速度的方向發展,體積減小會導致電路的布局布線密度變大,而信號的頻率卻在提高,使得串擾高發。PCB的設計、生產中,串擾是一個必須嚴肅對待的問題。

那么,我們在設計PCB的時候,應該注意什么呢?

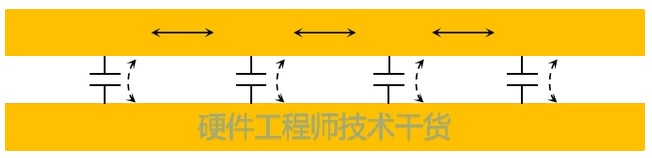

1.線之間的間距盡量大,因為間距越大,電容電感之間的影響就越小,電磁場耦合也會變小。

2.傳輸線和參考平面間的距離越小越好,這樣會使其更緊密地耦合,減少臨近線的干擾。

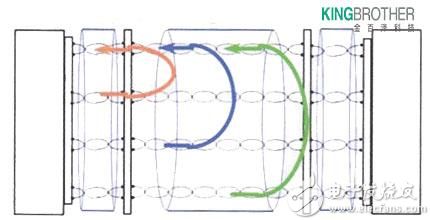

3.如果不同層的信號存在干擾,那么走線時讓這兩層走線方向垂直,因為相互垂直的線,電場和磁場也是相互垂直的,可以減少相互間的串擾。

4.盡可能使用介電常數最低的疊層介質材料,這樣做可以在給定特性阻抗的情況下,使得信號路徑與返回路徑間的介質厚度保持最小。

5.如果使用防護布線,盡量達到其所需要的寬度,并用過孔使防護線與返回路徑短接。

6.如果信號改變參考平面,則參考平面應盡量靠近信號平面。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

發布評論請先 登錄

相關推薦

熱點推薦

淺談PCB串擾及降低方法

先來說一下什么是串擾,串擾就是PCB上兩條走線,在互不接觸的情況下,一方干擾另一方,或者相互干擾。主要表現是波形有異常雜波,影響信號完整

發表于 11-10 17:00

?2722次閱讀

解決PCB設計消除串擾的辦法

在PCB電路設計中有很多知識技巧,之前我們講過高速PCB如何布局,以及電路板設計最常用的軟件等問題,本文我們講一下關于怎么解決PCB設計中消除串擾

發表于 11-02 09:19

高速PCB設計中如何消除串擾?

PCB布局上的串擾可能是災難性的。如果不糾正,串擾可能會導致您的成品板完全無法工作,或者可能會受到間歇性問題的困擾。讓我們來看看

輕松定位和修復pcb串擾問題

PCB串擾問題可以很容易地定位和固定使用HyperLynx?墊專業或墊+標準。從PCB布局出口你的設計之后,在批處理模式運行模擬和/或交互模式來識別潛在的

如何解決PCB串擾問題

高速PCB設計中,信號之間由于電磁場的相互耦合而產生的不期望的噪聲電壓信號稱為信號串擾。串擾超出一定的值將可能引發電路誤動作從而導致系統無法

發表于 07-19 09:52

?2897次閱讀

如何解決PCB布局中的串擾問題

您可能會發現布局和布線會因攻擊者的蹤跡而產生強烈的串擾。 那么,在設計中哪里可以找到串擾,以及在PCB中識別出不良走線的最簡單方法是什么?您

如何解決EMC設計中的串擾問題?

? 串擾是通過近電場(電容耦合)和磁場(電感耦合)在相鄰導體之間耦合的噪聲。盡管任何相鄰導體都表現出串擾,但是當它出現在強干擾信號和敏感信號之間時,對信號完整性將造成很大的影響。

PCB串擾如何解決

PCB串擾如何解決

評論