串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法:

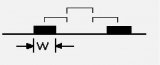

(1)在情況允許的情況下,盡量增大走線之間的距離,減小平行走線的長度,必要時采用jog方式走線。

(2)在確保信號時序的情況下,盡可能地選擇上升沿和下降沿速度更慢的器件,使電場和磁場變化的速度變慢,從而降低串擾。

(3)在設計走線時,應該盡量使導體靠近地平面或電源平面。這樣可以使信號路徑與地平面緊密的耦合,減少對相鄰信號線的干擾。

(4)在布線空間允許的條件下,在串擾較嚴重的兩條信號線之間插入一條地線,可以減小兩條信號線間的耦合,進而減小串擾。

串擾是信號完整性中的重要內容,影響系統的時序、降低噪聲容限,導致系統無法正常的工作。

介紹了高速電路中串擾產生的機理,并通過仿真對串擾進行分析,得出串擾的大小與影響串擾相關因素的關系,在此基礎上提出了一些減小串擾的方法,對于在高速高密度的電路設計中解決串擾問題有一定的指導意義。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電子產品

+關注

關注

6文章

1300瀏覽量

61163 -

串擾

+關注

關注

4文章

196瀏覽量

27861

原文標題:IPC 往屆PCB設計冠、亞、季軍作品欣賞

文章出處:【微信號:eda365wx,微信公眾號:EDA365電子論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

消除串擾的方法

消除串擾的方法合理的PCB布局-將敏感的模擬部分與易產生干擾的數字部分盡量隔離,使易產生干擾的數字信號走線上盡量靠近交流地,使高頻信號獲得較好的回流路徑。盡量減小信號回路的面積,降低地線的阻抗,采用多點接地的

發表于 06-18 07:52

PCB設計中避免串擾的方法

變化的信號(例如階躍信號)沿傳輸線由A到B傳播,傳輸線C-D上會產生耦合信號,變化的信號一旦結束也就是信號恢復到穩定的直流電平時,耦合信號也就不存在了,因此串擾僅發生在信號跳變的過程當中,并且

發表于 08-29 10:28

在高速PCB設計中消除串擾的方法與討論

串擾是高速 PCB 設計人員存在的基礎之一。市場需要越來越小和更快的電路板,但是兩條平行走線或導體放置在一起的距離越近,一條走線上產生的電磁場干擾另一條走線的機會就越大。 在本文中,我們將介紹串

避免PCB中出現串擾的方法

為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾,稱為3W規則。如要達到98%的電場不互相干擾,可使用10W的間距。

解決串擾的方法

解決串擾的方法

評論