隨著電子技術的不斷發展,在高速電路中信號的頻率的變高、邊沿變陡、電路板的尺寸變小、布線的密度變大,這些因素使得在高速數字電路的設計中,信號完整性問題越來越突出,其已經成為高速電路設計工程師不可避免的問題。

串擾是指有害信號從一個網絡轉移到另一個網絡,它是信號完整性問題中一個重要問題,在數字設計中普遍存在,有可能出現在芯片、PCB板、連接器、芯片封裝和連接器電纜等器件上。

如果串擾超過一定的限度就會引起電路的誤觸發,導致系統無法正常工作。因此了解串擾問題產生的機理并掌握解決串擾的設計方法,對于工程師來說是相當重要的。

串擾問題產生的機理 ? ? ?

串擾是信號在傳輸線上傳播時,由于電磁耦合而在相鄰的傳輸線上產生不期望的電壓或電流噪聲干擾,信號線的邊緣場效應是導致串擾產生的根本原因。

為了便于分析,下面介紹幾個有關的概念。

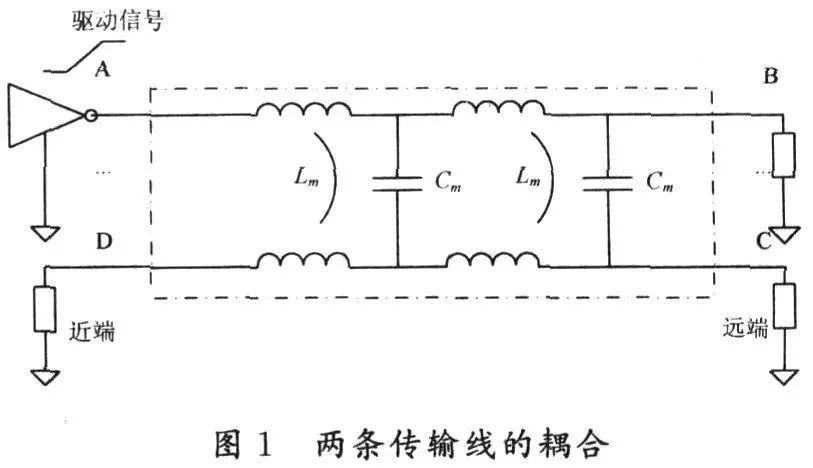

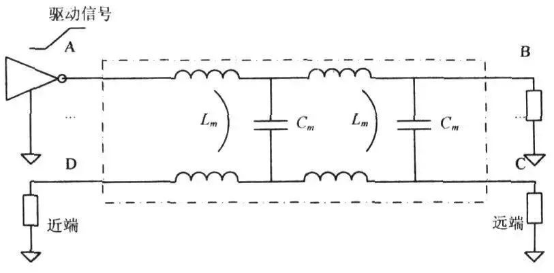

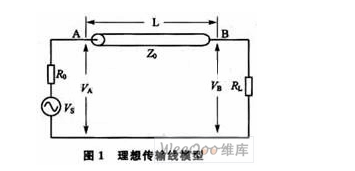

如圖1所示,假設位于A點的驅動器是干擾源,而位于D點的接受器為被干擾對象,那么驅動器A所在的傳輸線被稱之為干擾源網絡或侵害網絡(Agreessor),相應的接收器D所在的傳輸線網絡被稱之為靜態網絡或受害網絡。

靜態網絡靠近干擾源一端的串擾稱為近端串擾(也稱后向串擾),而遠離干擾源一端的串擾稱為遠端串擾(或稱前向串擾)。由于產生的原因不同將串擾可分為容性耦合串擾和感性耦合串擾兩類。

圖1:兩條傳輸線的耦合

1 容性耦合機制

當干擾線上有信號傳輸時,由于信號邊沿電壓的變化,在信號邊沿附近的區域,干擾線上的分布電容會感應出時變的電場,而受害線處于這個電場里面,所以變化的電場會在受害線上產生感應電流。

可以把信號的邊沿看成是沿干擾線移動的電流源,在它移動的過程中,通過電容耦合不斷地在受害線上產生電流噪聲。

由于在受害線上每個方向的阻抗都是相同的,所以50%的容性耦合電流流向近端而另50 9/6則傳向遠端。

此外,容性耦合電流的流向都是從信號路徑到返回路徑的,所以向近端和遠端傳播的耦合電流都是正向的。

對于近端容性耦合串擾,隨著驅動器輸出信號出現上升沿脈沖,流向近端的電流將從零開始迅速增加,當邊沿輸入了一個飽和長度以后,近端電流將達到一個固定值。

另外,流向近端的耦合電流將以恒定的速度源源不斷地流向近端,當上升沿到達干擾線的接收端,此上升沿會被接受吸收,不再產生耦合電流信號,但是受害線上還有后向電流流向受害線的近端,所以近端的耦合電流將持續兩倍的傳輸延遲。?

對于遠端容性耦合串擾,由于信號的邊沿可看成是移動的電流源,它將在邊沿的附近區域產生經互容流進受害線的耦合電流,而產生的耦合電流將有50%與干擾線上的信號同向而且速度相同地流人遠端,因此隨著干擾線上信號的傳輸,在受害線上將不斷地產生的前向耦合電流而且和已經存在的前向耦合電流不斷地疊加,并一同傳向遠端。

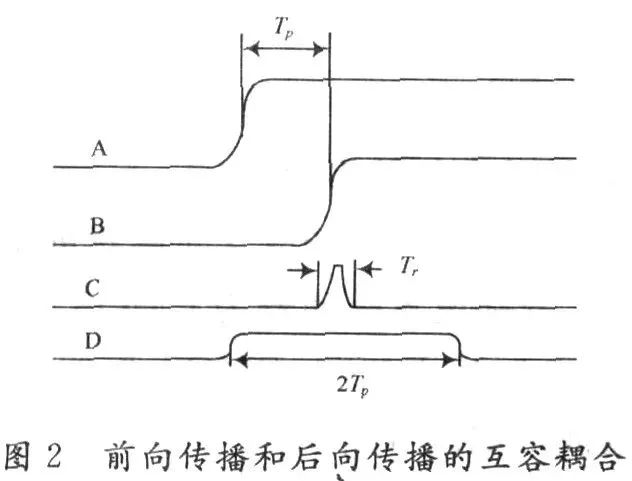

由于串擾只在信號的邊沿附近區域產生,流向遠端的耦合電流的持續時間等于信號的躍變時間。具體的容性耦合如圖2所示。

圖2:前向傳播和后向傳播的互容耦合

2 感性耦合機制

當信號在于擾線上傳播時,由于信號電流的變化,在信號躍變的附近區域,通過分布電感的作用將產生時變的磁場,變化的磁場在受害線上將感應出噪聲電壓,進而形成感性的耦合電流,并分別向近端和遠端傳播。

與容性耦合電流不一樣的是,感性耦合電流的方向與干擾線上信號傳播的方向是反向的,向近端傳輸時,電流回路是從信號路徑到返回路徑,而向遠端傳輸時,電流回路則是從返回路徑到信號路徑。

對于近端感性耦合串擾,其特征與近端容性耦合串擾非常相似,也是從零開始迅速增加,當傳輸長度大于等于飽和長度以后,將穩定在一個固定值,持續時間是兩倍的傳輸延遲。

因為流向近端的感性耦合電流與容性耦合電流同向,所以兩者將疊加在一起。

對于遠端感性耦合串擾,感性耦合噪聲與干擾線上信號邊沿的傳播速度相同,而且在每一步將會耦合出越來越多的噪聲電流,持續的時間等于信號躍變的時間。

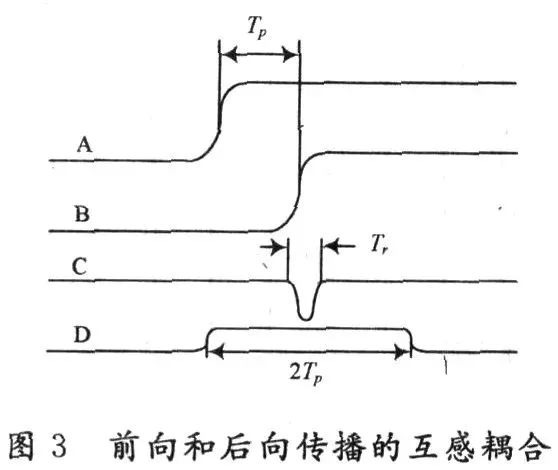

但是由于電流流向與遠端容性耦合電流是反向的,所以到達受害線遠端接收器的耦合電流是兩者之差,具體的感性耦合如圖3所示。

圖3:前向和后向傳播的互感耦合

3 互感和互容的混合效應

一般地,在完整的地平面上,容性和感性的耦合產生的串擾電壓大小相等,因此遠端串擾的總噪聲由于容性和感性耦合的極性不一樣而相互抵消。

在帶狀線電路更能夠顯示兩者之間很好的平衡,其遠端耦合系數極小,但是對于微帶線路,由于與串擾相關的電場大部分穿過的是空氣,而不是其他的絕緣材料,因此容性串擾比感性串擾小,導致其遠端串擾系數是一個小的負數。

串擾的仿真分析 ? ? ?

在實際的設計中,板層特性(如厚度,介質常數等)以及線長、線寬、線距、信號的上升時間等都會對串擾有所影響。

下面結合使用Mentor Graphie公司的信號完整性仿真軟件Hyperlynx,對上述的影響串擾的因素進行分析。

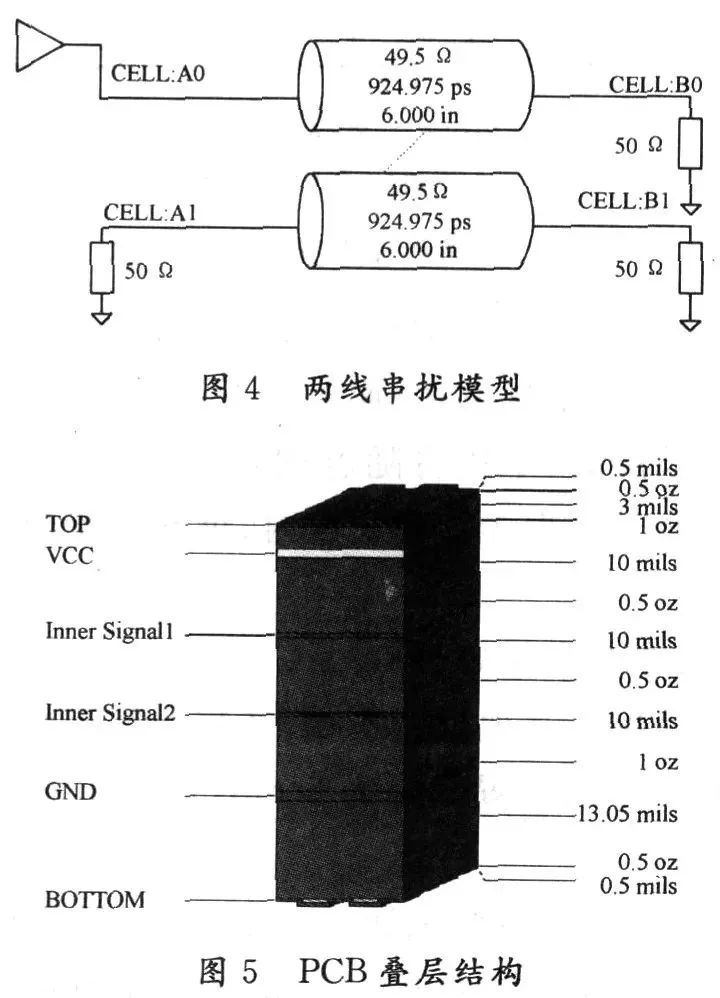

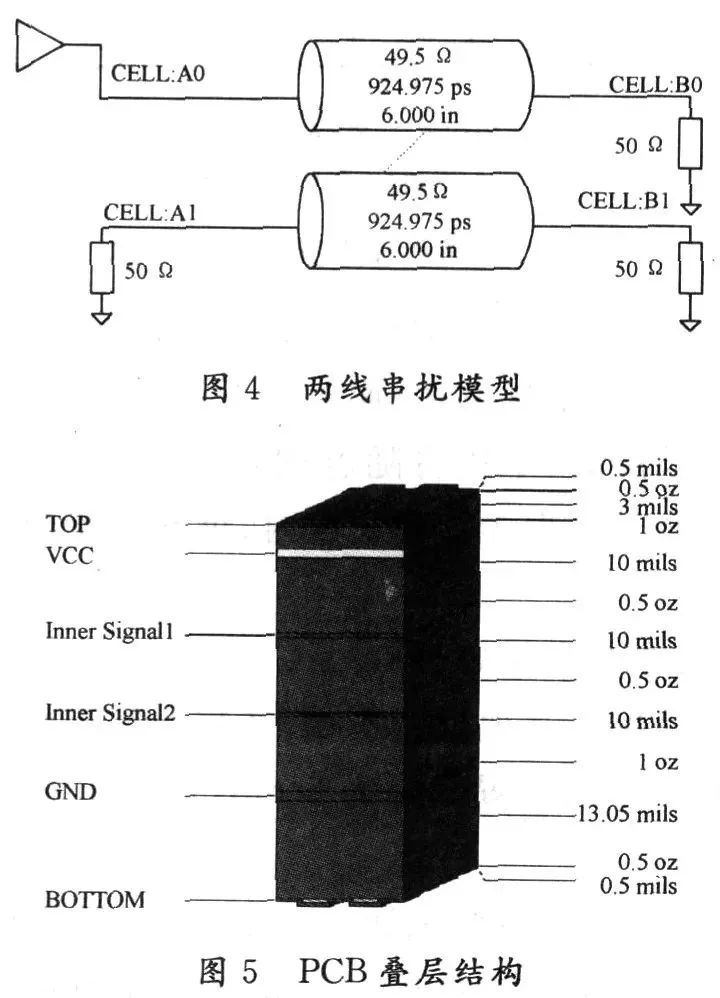

首先在Hyperlynx中建立兩線串擾的模型,如圖4所示,設兩線的線寬為5 mil,線長為6 in,線距為5 mil,兩線均為頂層微帶線,特性阻抗為49.5Ω,兩線都端接50Ω的電阻,以消除反射的影響。

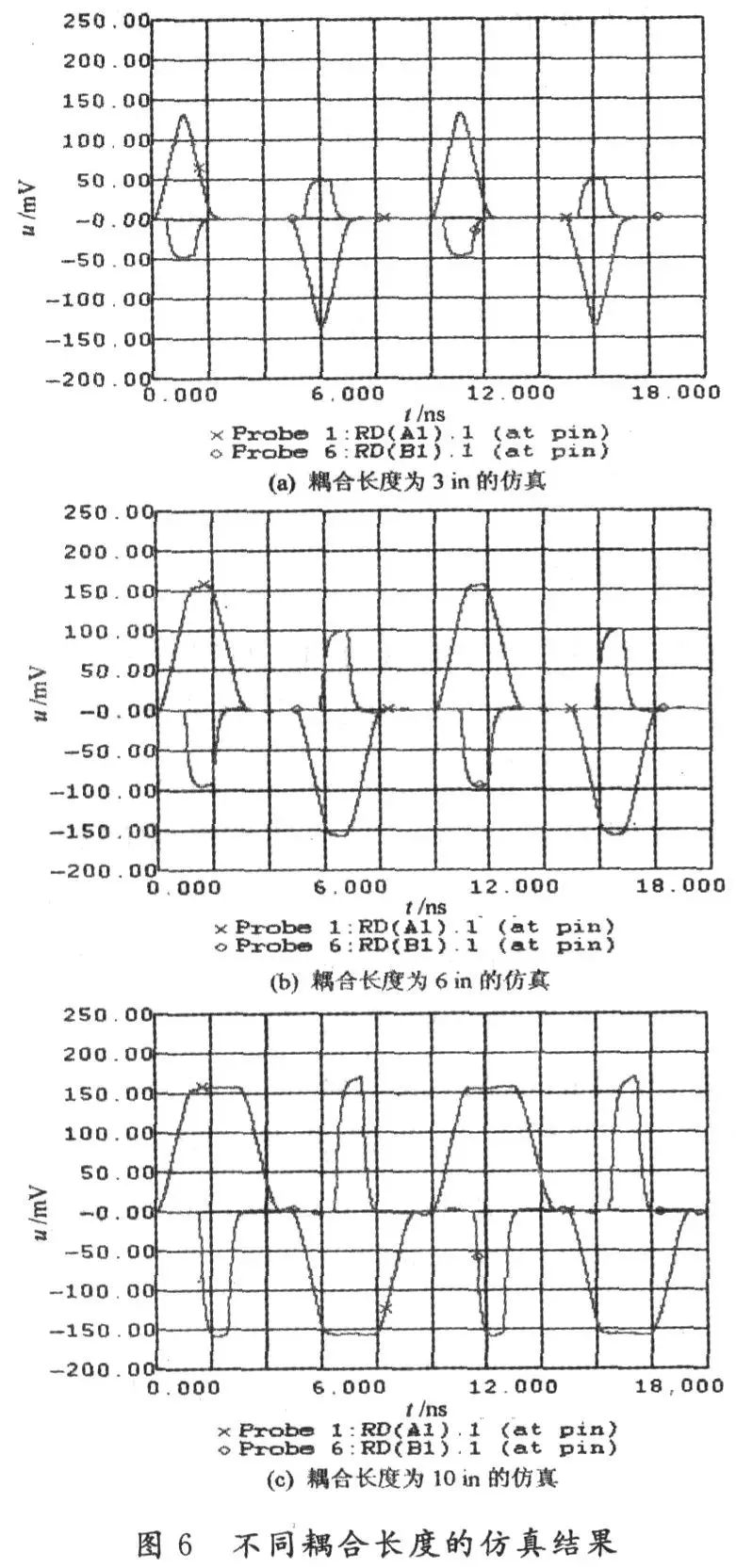

干擾線的驅動器采用CMOS工藝器件的IBIS模型,電壓為3.3 V,頻率為100 MHz。PCB的介電常數為4.3,六層板,其疊層結構如圖5所示。

圖4:兩線串擾模型

圖5:PCB疊層結構

1 耦合長度對串擾的影響

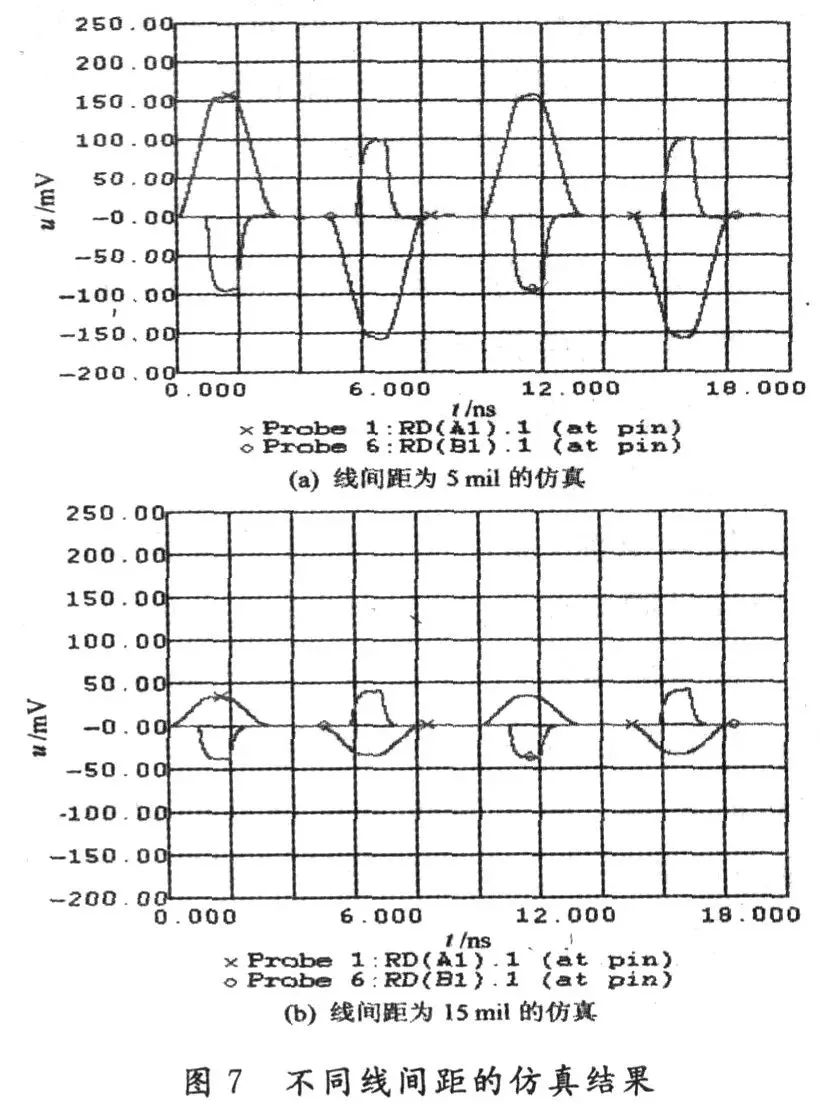

改變兩線的耦合長度,分別將耦合長度設置為3 in,6 in,10 in,其他設置不變。

圖6(a)是耦合長度為3 in的串擾波形,其中近端串擾峰值為126.34 mV,遠端為43.01 mV;圖6(b)是耦合長度為6 in的串擾波形,其近端串擾峰值為153.23 mV,遠端為99.46 mV;圖6(c)是耦合長度為10 in的串擾波形,其近端串擾峰值為153.23 mV,遠端為163.98 mV。

由此可見,對于遠端串擾峰值與耦合長度成正比,耦合長度越長,串擾越大;而對于近端串擾,當耦合長度小于飽和長度時,串擾將隨著耦合長度的增加而增加,但是當耦合長度大于飽和長度時,近端串擾值將為一個穩定值。

圖6:不同耦合長度的仿真結果

2 線間距對串擾的影響

以下是保持其他設置不變,考察線間距的改變對串擾的影響。分別設置線距為5 mil,15 mil,仿真波形如圖7所示。

圖7:不同線間距的仿真結果

由圖7可知,當線間距為5 mil時,近段串擾峰值為153.23 mV,遠端為99.46 mV;而線間距為15 mil時,近端串擾峰值為33.40 mV,遠端為40.49 mV。

可見隨著線間距的增大,無論是近端還是遠端串擾都將減小,當線間距大于等于線寬的3倍時,串擾已經很小。

3 上升時間對串擾的影響

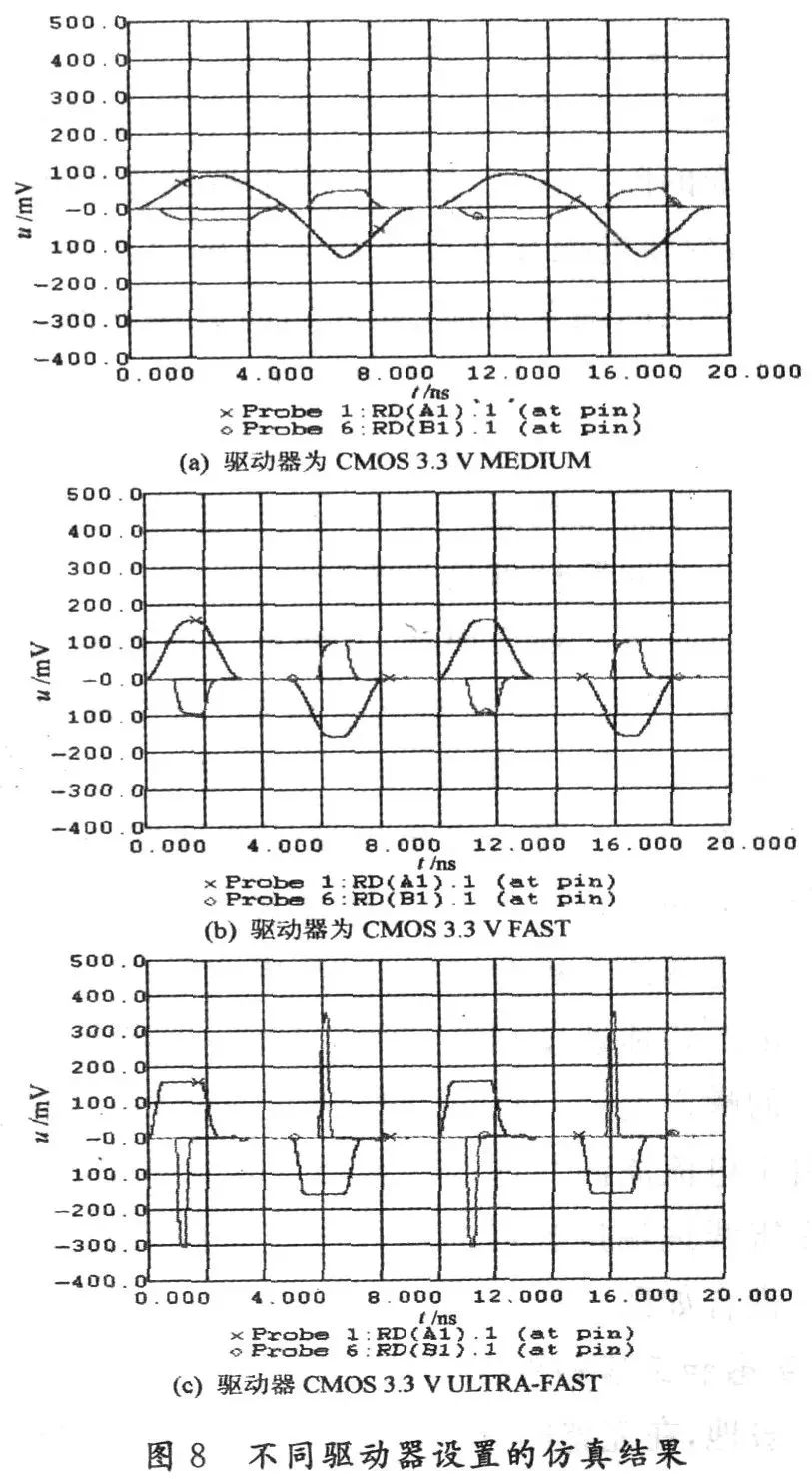

下面考察上升沿時間的變化對串擾的影響,其他設置保持不變。分別設置驅動器為CMOS 3.3 V MEDI—UM;CMOS 3.3 V FAST;CMOS 3.3 V ULTRA—FAST,仿真波形如圖8所示。

圖8:不同驅動器設置的仿真結果

圖8(a)中的近端串擾峰值為153.9 mV,遠端串擾為46.3 mV;圖8(b)中近端串擾峰值為153.2 mV,遠端串擾為99.5 mV;圖8(c)中近段串擾峰值為153.2 mV,遠端串擾為349.9 mV。

可見,當上升沿時間縮短時,遠端串擾噪聲越來越大。

對于近端串擾來說,如果與傳輸線的時延相比,上升時間較短,則近端串擾與上升時間無關;而如果與傳輸線時遲相比,上升時間較長,則近端串擾噪聲與上升時間有關(隨著上升沿時間的減小,近端串擾變大)。

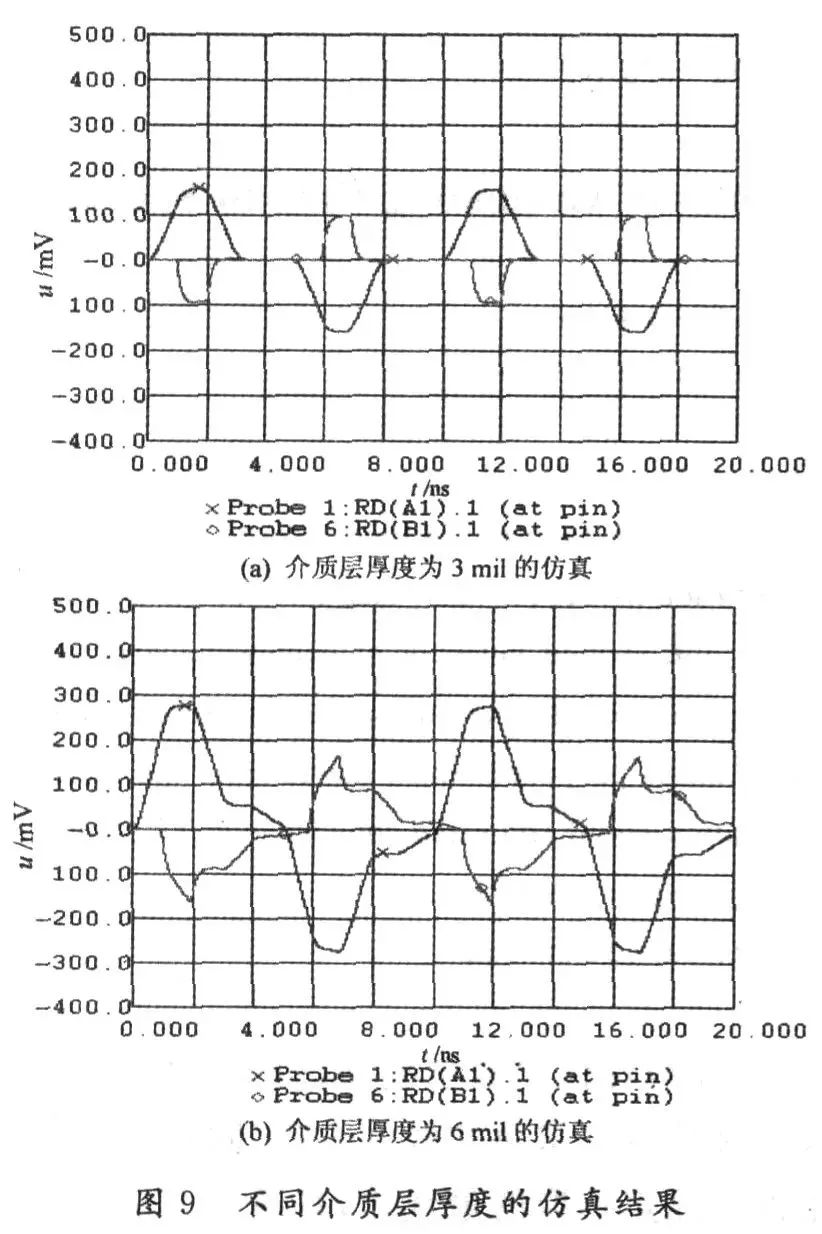

4 介質層厚度對串擾的影響

在PCB的疊層編輯器中將介質層厚度分別設置為3 mil和6 mil,其他設置不變,仿真波形如圖9所示。

圖9:不同介質層厚度的仿真結果

考察以上的仿真波形可知,當介質層厚度為3 mil時,近端串擾峰值為153.2 mV,遠端串擾為99.5 mV;當介質層厚度為6 mil時,近端串擾峰值為277.3 mV,遠端串擾為163.9 mV。

可見,隨著介質層厚度的減小,串擾也將變小。

解決串擾的方法 ? ? ?

串擾在電子產品的設計中普遍存在,通過以上的分析與仿真,了解了串擾的特性,總結出以下減少串擾的方法:

(1)在情況允許的情況下,盡量增大走線之間的距離,減小平行走線的長度,必要時采用jog方式走線。

(2)在確保信號時序的情況下,盡可能地選擇上升沿和下降沿速度更慢的器件,使電場和磁場變化的速度變慢,從而降低串擾。

(3)在設計走線時,應該盡量使導體靠近地平面或電源平面。這樣可以使信號路徑與地平面緊密的耦合,減少對相鄰信號線的干擾。

(4)在布線空間允許的條件下,在串擾較嚴重的兩條信號線之間插入一條地線,可以減小兩條信號線間的耦合,進而減小串擾。

結 語 ? ? ?

串擾是信號完整性中的重要內容,影響系統的時序、降低噪聲容限,導致系統無法正常的工作。

介紹了高速電路中串擾產生的機理,并通過仿真對串擾進行分析,得出串擾的大小與影響串擾相關因素的關系,在此基礎上提出了一些減小串擾的方法,對于在高速高密度的電路設計中解決串擾問題有一定的指導意義。

編輯:黃飛

?

電子發燒友App

電子發燒友App

評論