當電路板上出現串擾時,電路板可能無法正常工作,并且在那里也可能會丟失重要信息。為了避免這種情況,PCB設計人員的最大利益在于找到消除其設計中潛在串擾的方法。讓我們談談串擾和一些不同的設計技術,這些技術可以回答如何減少PCB布局中的串擾。

印刷電路板上的串擾

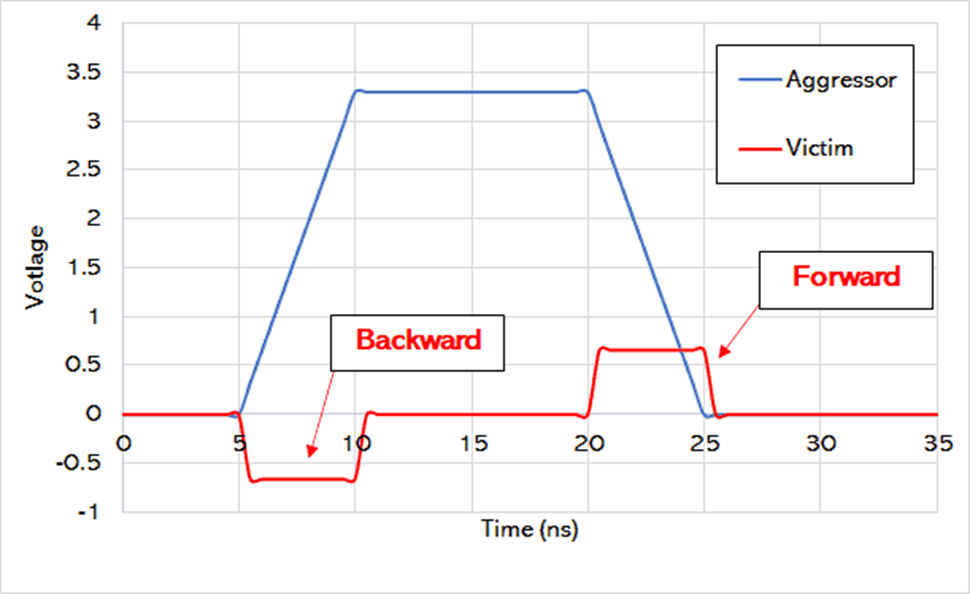

電路板上的活動過多會導致信號傳輸困難。考慮一下電路板上并排在一起的兩條走線。如果一條跡線的信號比另一條跡線的信號具有更大的幅度,可能會使另一條跡線過載。就像在嘈雜的房間中試圖講話時保持自己的直覺很難一樣,PCB上的“受害者”走線也同樣會受到響亮信號的影響。然后的問題是,受害信號將開始像侵略者信號那樣運行,而不是表現出應有的方式。

串擾定義為印刷電路板上跡線之間的意外電磁耦合。即使兩條跡線彼此之間沒有物理接觸,也可能是這種耦合導致的結果是一條跡線中的一個信號被另一信號強過。這種情況可能發生在具有可接受的走線間距但對于串擾不可接受的PCB上。

除了在同一層上并排的兩條走線之間可能產生串擾之外,走線在兩層之間垂直平行延伸的風險更大。這種效應被稱為寬邊耦合,是由于兩個信號層之間僅被很小厚度的芯材分開而產生的。該距離通常小于同一層上兩條跡線之間的間隔。

PCB設計工具如何幫助您解決串擾問題

這些天來,您在減少和消除電路板上的串擾方面擁有非常好的盟友,這就是PCB設計工具中的功能。一方面,設計工具可以為您提供的幫助極少,但現在情況已不再如此。

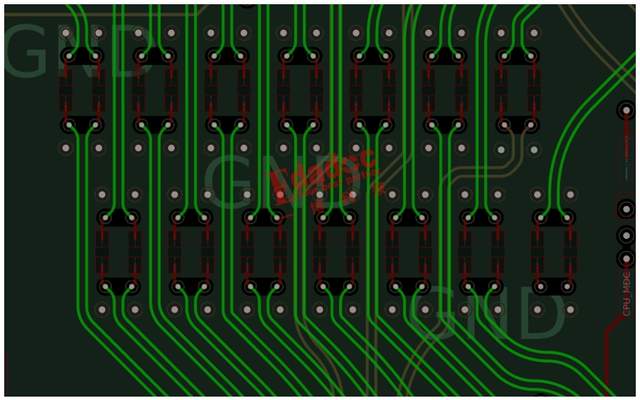

您可以設置各種各樣的設計規則,以指定走線之間以及走線到電路板上其他對象的間距。您甚至可以根據特定的網或穿過這些網的區域設置不同的間隙值。這將極大地幫助您設置設計,以避免可能發生串擾的情況。

設計工具還具有用于按特定寬度和間距布線差分對的特定功能,并且您可以設置走線長度以及將特定走線長度相互匹配的規則。您還可以指定可以在其上路由某些網絡的板的哪些層以及這些層上的走線的首選方向。您還可以使用串擾計算器以及其他仿真和分析工具。今天我們可以使用的設計工具包含各種設計約束功能,可以幫助解決諸如串擾之類的問題,我們只需要使它們起作用即可。

如何減少串擾的設計方法

現在我們已經討論了什么是串擾以及您的PCB設計工具如何為您提供幫助,讓我們看一下一些基本的PCB設計技巧,這些技巧可以避免設計中潛在的串擾區域:

l 配置您的電路板層,以使兩個相鄰的信號層具有相互交叉而不是相互平行的首選布線方向。如果第二層從“北到南”運行,則確保第三層從“東到西”運行。這樣,您可以將寬邊耦合的可能性降到最低。

l 在兩個相鄰信號層之間使用接地層,以進一步減少寬邊耦合的機會。這不僅會增加各層之間的距離,而且這種配置還可以為您提供更好的接地平面返回路徑。

l 在高速路由(差分對,時鐘路由等)和其他路由之間保持盡可能多的空間。這里的一般原理是通過以線寬的三倍隔開走線(測得的中心到中心),可以阻止70%的電場相互干擾。

串擾會在您的設計中引起嚴重的問題,您將需要盡可能多地了解它。我們為您提供的這是朝著這個方向邁出的偉大的第一步,以使您走上正確的道路。

-

電路板設計

+關注

關注

1文章

133瀏覽量

17421 -

PCB設計

+關注

關注

396文章

4934瀏覽量

95665 -

PCB布線

+關注

關注

22文章

473瀏覽量

43637 -

華秋DFM

+關注

關注

20文章

3515瀏覽量

6515

發布評論請先 登錄

AP2813 SOP8 封裝 PCB 布局 7 條黃金規則(工程師必背)

如何設置HDI PCB布局?

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

隔離地過孔要放哪里,才能最有效減少高速信號過孔串擾?

PCB布局布線的相關基本原理和設計技巧

技術資訊 I 在 Allegro PCB 中如何快速布局

如何減少PCB布局中的串擾

如何減少PCB布局中的串擾

評論