感謝你對Vivado HLS也就是XILINX’s 高層次綜合解決方案有興趣,這個解決方案綜合c,c++和系統c代碼成Verilog和VHDL RTL結構。

2012-04-25 08:59:37 3141

3141 賽靈思(Xilinx)因應鎖定新一代更智能(Smarter)功能的網絡和數據中心特定應用集成電路(ASIC)和特定應用標準產品(ASSP)方案出現重大效能與系統需求落差的問題,而該問題導致元件效能不敷應用的情況日趨嚴重,因此賽靈思推出全新解決方案

2013-03-12 09:14:37 2611

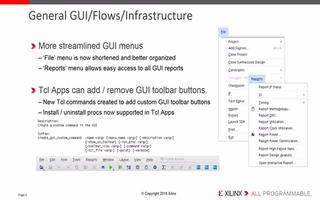

2611 在生產力方面進行了兩大改進。Vivado設計套件2013.1版本新增了一款以IP為中心的設計環境,用以加速系統集成;而其提供的一套完整數據庫,則可加速C/C++系統級設計和高層次綜合(HLS)。

2013-04-08 15:08:54 1265

1265 從 2019.2 版開始,賽靈思 SDK 開發環境已統一整合到全功能一體化的 Vitis 統一軟件平臺 中。 馬上開始將工程從賽靈思 SDK 移植到 Vitis 吧。 Vivado 工程升級 工程

2020-11-09 16:57:12 3744

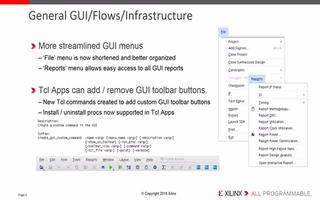

3744 作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 4357

4357 歷經四年的開發和一年的試用版本測試,賽靈思可編程顛覆之作 Vivado 設計套件終于震撼登場,并通過其早期試用計劃開始向客戶隆重推出。

2012-04-25 09:03:33 11462

11462

電子發燒友網訊:近年來,賽靈思不斷超越從Virtex-7 2000T到vivado設計套件的發布,都可以是行業發展的里程碑。現在就讓我們悉數下賽靈思的創新技術與產品吧。

2012-08-21 09:45:56 2737

2737 關于Zynq的Vivado 2013.1發行說明說:“需要及早訪問Vivado IP集成商”。這是什么意思?它是否真的支持Zynq開箱即用?提前致謝。以上來自于谷歌翻譯以下為原文Vivado

2018-12-04 11:00:58

將Vivado HLS建立的加速器功能集成到Vivado IP集成器中。賽靈思Smarter Vision方案在計算機視覺領域的應用立即觀看視頻回答問卷 參與抽獎觀看視頻并參與問卷調查的聽眾,將參加

2013-12-30 16:09:34

參考:UG973 (v2021.1)圖:賽靈思全新 Vivado? ML 版Vivado 2021.1這個新版本的新增加的一些特:1、在IP這個層面的功能的增強,主要體現在新增加了一個BD...

2021-07-20 07:06:23

每一版本都提供了完整的FPGA設計流程,并且專門針對特定的用戶群體(工程師)和特定領域的設計方法及設計環境要求進行了優化。那大家知道賽靈思ISE? 設計套件11.1版對FPGA有什么優化作用嗎?

2019-07-30 06:52:50

賽靈思Virtex-6 HXT FPGA ML630評估套件采用SiTime電子發燒友振具體型號為:SIT9102AI-243N25E200.0000,而目前針對這一型號sitime推出了抖動更低

2014-11-17 15:07:35

賽靈思Zynq-7000可擴展處理平臺(EPP)將雙ARM Cortex-A9 MPCore處理器系統與可編程邏輯和硬IP外設緊密集成在一起,提供了靈活性、可配置性和性能的完美組合。圍繞其剛剛推出

2019-05-16 10:44:42

可擴展的處理平臺- 是系統集成、軟件可編程性的靈活性與FPGA 硬件加速的完美結合,支持客戶打造定制和優化的系統。全球第一個支持高層次綜合設計方法的可編程邏輯企業- 其 AutoESL? 高層次綜合

2012-03-22 15:17:12

賽靈思有哪幾種ISE設計套件配置版本 ?

2021-04-30 06:30:50

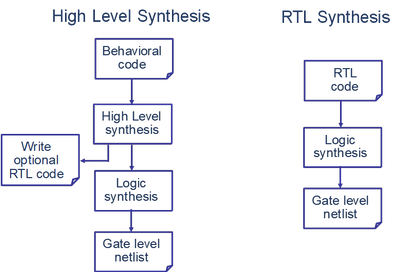

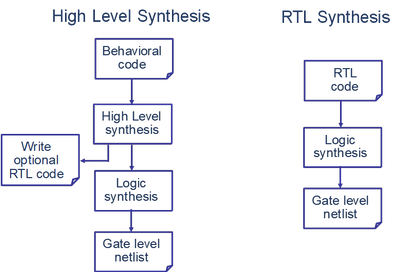

雖然淺顯易懂,但是它將基于CPU的架構的軟件程序與在高層次綜合這項技術上行為描述語言做出了明顯的區分。賽靈思的HLS官方手冊中,對文中提到了端口協議,優化指令,數據類型等都有非常詳細的解釋。本系列以后

2021-01-06 17:52:14

高層次綜合技術原理淺析

2021-02-01 06:04:00

1、HLS最全知識庫介紹高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD Xilinx而言

2022-09-07 15:21:54

目錄第1章:高層次生產力設計方法指南第2章:系統設計第3章:shell開發第4章:基于C語言的IP開發第5章:系統集成

2017-12-13 09:50:31

能做賽靈思方案的,請聯系

2019-01-21 19:31:40

、應用、后端支持.pdf直播簡介:為了解決FPGA的可編程性問題,實現從算法到RTL設計的快速編譯,我們引入了基于MLIR(多級別中間表示)的高層次綜合框架ScaleHLS,對算法的高層次描述進行多級

2022-11-27 12:43:17

Altera和賽靈思20年來都在FPGA這個窄眾市場激烈的競爭者,然而Peter Larson基于對兩個公司現金流折現法的研究表明,賽靈思是目前FPGA市場的絕對領先者。

2019-09-02 06:04:21

1、使用Vitis HLS創建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD

2022-09-09 16:45:27

FAST包處理器的核心功能是什么如何使用賽靈思FPGA加速包處理?

2021-04-30 06:32:20

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

最基本的OpenCV I/O功能都需要加速。為什么需要高層次綜合? 賽靈思推出的Vivado HLS是一款軟件編譯器,旨在將C、C++或SystemC編寫的算法轉變為針對用戶定義時鐘頻率和賽靈思產品

2014-04-21 15:49:33

詳解賽靈思All Programmable Smarter Vision解決方案

2021-06-02 06:56:12

) 的靈活可編程 VESADisplayPort v.1.1a 解決方案。該 IP 可隨時提供給賽靈思的客戶,但在用戶展開設計之前,建議先了解與該標準的部分關鍵功能有關的其它背景信息,如olicy Maker

2012-03-01 11:10:18

利用Mentor高層次綜合技術快速實現復雜DSP算法摘要:為了滿足產品上市時間和功能豐富性的要求,越來越多的先進設計公司開始提高設計的抽象層次進行復雜的D

2010-04-29 14:01:59 34

34 賽靈思:六大領域優化開發套件齊發,大幅提升SoC設計效率與創新

賽靈思 (Xilinx, Inc.)日前宣布,作為公司目標設計平臺最新一步的發展,賽靈思同時推出六大領域優化

2009-12-10 09:02:54 761

761 賽靈思推出最新Virtex-6/Spartan-6 FPGA 連接開發套件

近日,賽靈思公司(Xilinx, Inc. )宣布推出最新Virtex-6 和 Spartan-6 FPGA連接開發套件,該套件將為客戶提供一個綜合的、易用的

2009-12-15 08:42:01 1273

1273 賽靈思推出DTV可編程平臺

賽靈思公司日前在美國國際消費電子展 (CES) 上宣布推出首款為開發最先進數字電視 (DTV) 解決方案而優化的可編程平臺。該款賽靈思消費DTV目

2010-01-09 10:38:42 945

945 賽靈思推出即插即用高清電視參考設計

全球可編程邏輯解決方案領導廠商賽靈思公司(Xilinx, Inc.)近日推出一款全新的消費視頻增強參考設計。該款參考設計基于一個

2010-01-27 09:52:23 842

842 賽靈思推出ISE 12軟件設計套件

全球可編程平臺領導廠商賽靈思公司(Xilinx, Inc.)日前推出ISE 12軟件設計套件,實現了具有更高設計生產力的功耗和成

2010-05-05 09:49:39 930

930 全球可編程平臺領導廠商賽靈思公司(Xilinx)在 2011 年CES消費電子展上推出其最受歡迎的 Spartan-6 FPGA 消費類視頻套件(Consumer Video Kit)的最新版本。該套件為系統設計人員提供了一

2011-01-11 09:50:51 840

840 賽靈思公司宣布推出 ISE 13設計套件。這款屢獲殊榮的設計工具和 IP 套件新增了許多增強特性,可以提高片上系統(SoC) 設計團隊的生產力

2011-03-18 09:29:56 1143

1143 全球可編程平臺領導廠商賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX) )今天宣布推出具有全新功能的 ISE? 13.3 設計套件,可幫助 DSP 設計人員在面向無線、醫療、航空航天與軍用、高性能計算和

2011-11-07 09:25:02 912

912 在高層次對系統進行功耗佑算和功耗優化是soc設計的關健技術本文首先給出soc設計的特點和流程,然后綜述目前高層次功耗估算和功耗優化的常用方法和技術,重點論述寄存器傳輸級和

2011-12-27 16:42:38 46

46 賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX) )日前宣布推出 ISE? 13.4設計套件。該設計套件可提供對 MicroBlaze? 微控制器系統 (MCS) 的公共訪問功能、面向 28nm 7 系列 FPGA 的全新 RX 裕量分析和調試功

2012-02-01 09:02:53 2161

2161 賽靈思公司 (Xilinx, Inc. (NASDAQ:XLNX) )今天公開發布以 IP及系統為中心的新一代顛覆性設計環境 Vivado 設計套件

2012-04-25 08:51:15 1519

1519 賽靈思推出的 Vivado 設計套件和 Virtex-7 FPGA,使 EVE 等標準 FPGA 仿真供應商在產品性能和功能方面全面超越定制 ASIC 仿真供應商

2012-04-25 09:10:14 1963

1963 2012年4月25日全球可編程平臺領導廠商賽靈思公司全球公開發布了vivado設計套件。新的工具套件面向未來十年 “All Programmable”器件而精心打造, 致力于加速其設計生產力。

2012-04-25 15:50:44 2490

2490 4年數百名研發工程師的夜以繼日,1年100多家客戶和聯盟計劃成員的親身測試,4月25日,在外界毫無征兆的情況下,賽靈思(Xilinx)公司宣布推出全新的Vivado設計套件。

2012-04-27 09:13:06 1245

1245 賽靈思(Xilinx)公司宣布推出全新的Vivado設計套件。Xilinx全球高級副總裁湯立人表示,Vivado不是已有15年歷史的ISE設計套件的再升級(ISE采用的是當時極富創新性的基于時序的布局布線引

2012-06-19 17:50:14 1054

1054 賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX) )今天宣布首次面向所有用戶全面開放其新一代設計環境Vivado?設計套件2012.2

2012-07-27 10:22:10 965

965

All Programmable技術和器件的全球領先企業賽靈思公司與賽靈思聯盟計劃認證成員Barco Silex公司近日在2012國際廣播電視設備展(IBC 2012 )上宣布推出一款雙方聯合開發的綜合性平臺,該平臺

2012-09-26 10:57:55 1840

1840

電子發燒友網核心提示: 賽靈思稱為可編程顛覆之作Vivado設計套件于4月25日震撼登場。Vivado是賽靈思最新推出的、面向未來十年、替換ISE的設計套件。本文主要給大家介紹Vivado設計套件

2012-10-18 13:43:43 14983

14983 賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX) )今天宣布推出Vivado?設計套件2012.3版本,首次為在多核處理器工作站上運行該工具的客戶提供全新的增強功能,大幅提升生產力,同時,還為加速設計實

2012-10-24 16:12:41 792

792 隨著Vivado設計套件2012.4版的發布,客戶現可立即免費下載業界首款強大的SoC級的設計工具,支持All Programmable設計。

2012-12-21 13:46:22 3192

3192 ?設計方法。這套綜合性的設計方法能幫助采用Vivado設計套件的設計團隊加速設計進程,準確預測設計進度。賽靈思正通過其Vivado設計套件、用戶指南、視頻和講師指導的培訓課程、第三方工具以及IP等,全面簡化該設計方法的采用,并促進其廣泛部署。

2013-10-29 10:21:17 819

819 ,提供全新UltraFastTM設計方法,增強型即插即用IP配置、集成與驗證功能,以及部分重配置(Partial Reconfiguration)功能。Vivado?設計套件與賽靈思的All

2013-10-29 10:29:49 991

991 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 美國賽靈思官方授權培訓伙伴依元素科技,以賽靈思最新的客戶培訓課程,通過Webex在線舉辦免費培訓。近期推出的在線免費培訓是 “Vivado設計套件工具流程”。 Xilinx采用先進的 EDA 技術

2017-02-08 11:58:12 671

671 HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE? IP 子系統以及完整的 Vivado 實現工具套件,使主流用戶能夠方便地采用生產力最高、最

2017-02-08 19:35:06 952

952 IP子系統集成了多達80個不同的IP 核、軟件驅動程序、設計實例和測試平臺,可大幅提高生產力 賽靈思發布 Vivado Design Suite2015.3版本。這一新版本通過支持設計團隊利用

2017-02-09 01:15:42 389

389 支持現在即可利用量產級的芯片性能、完善的工具及IP立即啟動開發 賽靈思公司今天宣布,Vivado設計套件開始支持包括Zynq UltraScale+和Kintex UltraScale+器件在內

2017-02-09 03:25:37 632

632 ? 無縫集成在其設計中的工作。該 ?IP? 集成工具支持針對所有 ?Xilinx? 器件提供,其中包括最新 ?UltraScale? 器件系列,可充分滿足 ?Vivado? 設計套件工具 ?2014.4? 以及更高版本的要求。 了解更多 ??

2017-02-09 08:12:36 466

466

,有助于應對這種挑戰。 我們使用 Vivado? Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號

2017-11-16 20:05:41 2681

2681

如果您正在努力開發計算內核,而且采用常規內存訪問模式,并且循環迭代間的并行性比較容易提取,這時,Vivado? 設計套件高層次綜合(HLS) 工具是創建高性能加速器的極好資源。通過向C 語言高級算法描述中添加一些編譯指示,就可以在賽靈思FPGA 上快速實現高吞吐量的處理引擎。

2017-11-17 18:12:01 2315

2315 新型基于FPGA的設計使用IP核的數量和種類日趨繁多。Vivado?設計套件中的IP集成器 (IPI)工具和賽靈思通信IP讓設計人員能夠更加輕松快速地將IP模塊連接在一起。 為了更好地闡明IPI方法的強大之處,我們以遠程無線電頭端(RRH)為例。RRH位于天線附近,構成蜂窩通信網絡的一部分。

2017-11-18 01:25:01 2548

2548 眾多應用中的一個,而且創建定制硬件需要花費時間和成本。是不是這樣? 最近聽說了賽靈思的高層次綜合工具Vivado?HLS后,我開始重新思考這一問題。高層次綜合工具與Zynq?-7000 All Programmable SoC的結合為設計開辟了新的可能性。

2017-11-18 09:12:24 1626

1626

理由一:突破器件密度極限:在單個器件中更快速集成更多功能;理由二:Vivado以可預測的結果提供穩健可靠的性能和低功耗;理由三:Vivado設計套件提供了無與倫比的運行時間和存儲器利用率;理由四:使用Vivado高層次綜合生成基于C語言的IP。

2017-11-22 08:15:19 2250

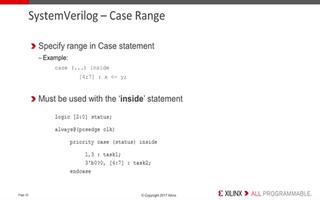

2250 Vivado HLS配合C語言等高級語言能幫助您在FPGA上快速實現算法。 高層次綜合(HLS)是指自動綜合最初用C、C++或SystemC語言描述的數字設計。工程師之所以對高層次綜合如此感興趣,不僅是因為它能讓工程師在較高的抽象層面上工作,而且還因為它能方便地生成多種設計解決方案。

2019-10-06 10:44:00 1849

1849

Vivado設計套件終于震撼登場,賽靈思采用先進的 EDA技術和方法,提供了全新的工具套件,可顯著提高設計生產力和設計結果質量,使設計者更好、更快地創建系統,而且所用的芯片更少。

2017-11-24 16:24:01 2272

2272 賽靈思 ISE 12設計套件利用智能時鐘門控技術將動態功耗降低30% 1)賽靈思今天要宣布什么消息? ISE? 12設計套件不僅實現了功耗與成本的突破性優化,而且為邏輯、嵌入式、DSP和系統設計人

2018-07-02 06:20:00 1457

1457 面向未來十年All Programmable,一個以IP及系統為中心的工具套件,把可編程系統的集成度和實現速度提升至原來的4倍。賽靈思公司(Xilinx)2012年4月25日美國發布會現場及答記者問

2018-06-05 13:45:00 4564

4564 賽靈思隆重推出Zynq-7000

2018-06-06 03:45:00 4960

4960

我們使用 Vivado ?Design Suite 的高層次綜合 (HLS) 工具來評估針對 E-UTRA I/Q 數據的開放無線電設備接口 (ORI) 標準壓縮方案,以估計其對信號保真度的影響、造成的時延及其實現成本。我們發現賽靈思的 Vivado HLS 平臺能夠高效評估和實現所選壓縮算法。

2018-07-24 09:30:00 2717

2717

、HL 設計版本和 HL WebPACK 版本。所有 HLx 版本均包括帶有 C/C++ 庫的 Vivado 高層次綜合 (HLS)、Vivado IP 集成器 (IPI)、LogicCORE IP

2018-08-17 11:43:00 4072

4072 賽靈思公司為成本敏感型應用推出靈活的 I/O 密集型器件——Spartan-7 FPGA系列。該新型系列器件可滿足汽車、消費類電子、工業物聯網、數據中心、有線/無線通信和便攜式醫療解決方案等多種

2018-08-20 10:48:00 1968

1968 賽靈思推出了新款 Zynq UltraScale+ RFSoC ZCU111 評估套件,用于支持 RF 級模擬設計評估,便于廣大用戶親身嘗試這款顛覆性技術.

2018-08-26 11:08:33 9320

9320 All Programmable SoC 的生產力帶來重大突破。伴隨此款最新版Vivado 設計套件推出的還包括其內含的 Vivado 高層次綜合(HLS)和IP集成器的增強功能,以及最新性能監控

2018-09-06 16:07:00 1987

1987 賽靈思公司(Xilinx)今天宣布推出Vivado設計套件2014.1版,這是業界唯一一款SoC增強型開發環境。該版本增加了UltraFast設計方法的自動化功能,讓所有器件的運行時間平均縮短達

2018-09-13 16:59:00 1593

1593 賽靈思公司推出ISE設計套件11.1版本(ISE Design Suite 11.1)。這一FPGA設計解決方案在業界率先為邏輯、數字信號處理、嵌入式處理以及系統級設計提供了完全可互操作的領域專用

2018-10-25 15:47:50 977

977 賽靈思公司推出ISE設計套件11.1版本(ISE Design Suite 11.1)。這一FPGA設計解決方案在業界率先為邏輯、數字信號處理、嵌入式處理以及系統級設計提供了完全可互操作的領域專用

2018-10-27 08:22:00 5106

5106 作為集成電路設計領域現場可編程門陣列 (FPGA) 技術的創造者之一,賽靈思一直積極推廣高層次綜合 (HLS) 技術,通過這種能夠解讀所需行為的自動化設計流程打造出可實現此類行為的硬件。賽靈思剛剛推出了一本專著,清晰介紹了如何使用 HLS 技術來創建優化的硬件設計。

2018-11-10 11:01:05 3178

3178 本視頻重點向您介紹了Vivado設計套件2017.3版本中的增強功能,包括操作系統和器件支持,高級增強功能,加速集成,實施和驗證的各種升級和改進。歡迎收看本視頻,了解更多有關

Vivado設計套件的新功能。

2018-11-21 06:15:00 4104

4104

本視頻重點介紹了Vivado設計套件2018.1版本中的新增功能,包括對操作系統以及器件的支持情況,還有高層次增強功能,以及各種功能改進以加速設計集成,實現和驗證的過程。

2018-11-20 06:28:00 3109

3109

Vivado設計套件,是FPGA廠商賽靈思公司2012年發布的集成設計環境。包括高度集成的設計環境和新一代從系統到IC級的工具,這些均建立在共享的可擴展數據模型和通用調試環境基礎上。這也是一個

2019-06-18 08:00:00 14

14 賽靈思的 FPGA 和 All Programmable SoC 提供多個定制選項,讓黑客開發套件 (HDK) 成為了一款多功能且易于重新編程的通用工具。

2019-07-30 17:41:59 3566

3566 Vivado實驗室版本是一款免費的輕量級Vivado設計套件的編程與調試版本。該實驗室版本包含Vivado器件編程器、Vivado邏輯與串行I/O分析器以及內存調試工具,專門針對無需全功能Vivado設計套件的實驗室環境。

2019-07-31 11:25:11 2573

2573 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述

2021-01-14 09:27:28 2671

2671 說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2022-02-08 17:26:42 9381

9381

本文介紹如何在 vivado 開發教程(一) 創建新工程 的基礎上, 使用IP集成器, 創建塊設計。

2022-02-08 10:47:39 3601

3601

說起高層次綜合技術(High-level synthesis)的概念,現在有很多初學者簡單地把它理解為可以自動把c/c++之類地高級語言直接轉換成底層硬件描述語言(RTL)的技術。其實更準確的表述是:由更高抽象度的行為描述生產電路的技術。

2021-01-28 09:11:08 3

3 提供了多種加速應用和 IP 解決方案。 Uncanny Vision屬于最早使用 Kria SOM 的用戶之一。 采用 KV260 入門套件開發自己的 ALPR(自動車牌識別) 解決方案,現已通過賽靈

2021-06-10 18:04:28 2519

2519 賽靈思公司昨日宣布推出 Vivado ML 版,這是業內首個基于機器學習( ML )優化算法以及先進的面向團隊協作的設計流程打造的 FPGA EDA 工具套件,可以顯著節省設計時間與成本。與目前

2021-06-24 11:42:16 2633

2633 賽靈思近日宣布推出 Vivado ML 版,這是業內首個基于機器學習(ML )優化算法以及先進的面向團隊協作的設計流程打造的 FPGA EDA 工具套件,可以顯著節省設計時間與成本,與目前

2021-07-02 16:40:13 3410

3410

內核,并使用 C/C++ 語言代碼在 Vivado Design Suite 中為賽靈思器件設計開發 RTL IP。

2022-05-25 09:43:36 3450

3450 01 演講題目 ? 開源硬件系列02期: 從PyTorch到RTL - 基于MLIR的高層次綜合技術 02 演講時間 ? 2022年11月27日 上午?10:00 03 內容簡介 ? 為了解

2022-11-24 08:15:03 2694

2694 英特爾? NUC 8 支持更高層次的設計

2022-12-29 10:02:52 1793

1793

電子發燒友網站提供《UltraFast高層次生產力設計方法指南.pdf》資料免費下載

2023-09-15 10:41:47 0

0 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 隨著 AMD Spartan UltraScale+ 系列現已投入量產,解鎖其功能集的最快途徑便是采用最新 AMD Vivado 工具版本( 2025.1 或更高版本)和全新操作指南資源。該集成

2025-09-23 09:15:55 1390

1390

電子發燒友App

電子發燒友App

評論