由于FPGA技術和ARM技術應用越來越廣泛,通過設計并行總線接口來實現兩者之間的數據交換,可以較容易地解決快速傳輸數據的需求,因此設計滿足系統要求的FPGA并行總線顯得尤為重要。本文設計的FPGA的ARM外部并行總線接口,滿足了總線的時序要求,并在某航空機載雷達應答機中進行了應用.

2013-08-15 10:44:19 9148

9148

本文針對Mali-T604 GPU論述了基于OpenCL的Linux平臺上進行通用計算并行優化的方法,論述了Mali-T604 GPU的硬件特點,并基于OpenCL設計了二維矩陣乘法的并行方案,在

2015-08-07 17:12:13 3862

3862

具有現場可編程能力,即使產品已經投入市場,也可根據特殊應用重新配置硬件; b)FPGA具有強大的并行處理能力; c)

2020-12-17 12:58:21 5247

5247 InTime。 前言 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著從 C 轉化得到 RTL 基本不可能。其實,使用 FPGA 工具設置來優化設計可以最

2020-12-20 11:46:46 2389

2389

HLS 優化設計的最關鍵指令有兩個:一個是流水線 (pipeline) 指令,一個是數據流(dataflow) 指令。正確地使用好這兩個指令能夠增強算法地并行性,提升吞吐量,降低延遲但是需要遵循一定

2021-01-08 10:26:01 9923

9923 雖然 FPGA 可使用 Verilog 或 VHDL 等低層次硬件描述語言 (HDL) 來編程,但現在已有多種高層次綜合 (HLS) 工具可以采用以 C/C++ 之類的更高層次的語言編寫的算法描述

2022-10-12 15:06:47 1502

1502 ? HLS任務級編程第一篇文章可看這里: HLS之任務級并行編程 HLS的任務級并行性(Task-level Parallelism)分為兩種:一種是控制驅動型;一種是數據驅動型。對于控制驅動型

2023-07-27 09:22:10 1950

1950

HLS的任務級并行性(Task-level Parallelism)分為兩種:一種是控制驅動型;一種是數據驅動型。

2023-07-27 09:21:40 1613

1613

今天我們看的這篇論文介紹了在多FPGA集群上實現高級并行編程的研究,其主要目標是為非FPGA專家提供一個成熟且易于使用的環境,以便在多個并行運行的設備上擴展高性能計算(HPC)應用。

2024-07-24 14:54:16 2361

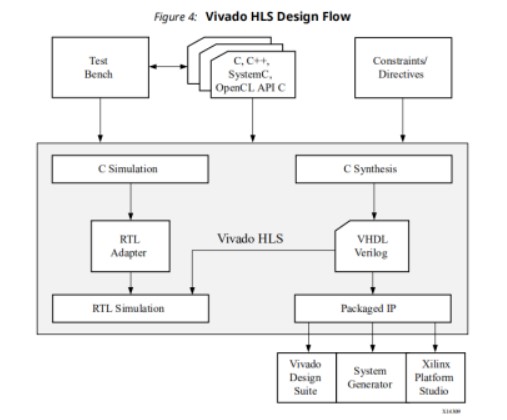

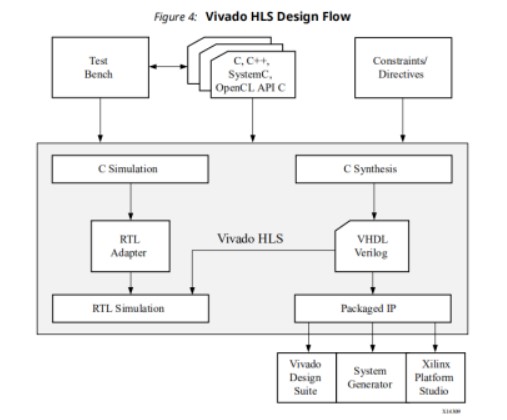

2361 Vivado? HLS 編譯器提供了一個與專用和標準處理器共享關鍵技術的編程環境,可優化基于 C 的程序。

=#6。= TensorFlow 和 PyTorch 等 AI 平臺

工程師使用Pytorch 或

2024-03-30 11:50:56

(HLS) 的幫助下,基于 C 語言的語言現在可用于 FPGA 設計。具體來說,AMD Vivado? HLS 編譯器提供的編程環境能夠與標準處理器及專用處理器共享關鍵技術,用于優化 C 語言程序

2023-06-28 18:18:57

),設計定制化的FPGA架構,以優化性能和功耗。

2.提升跨領域技能? AI知識儲備:掌握深度學習算法、模型量化和優化技術,以便更好地將AI模型與FPGA硬件結合。? 系統集成能力:熟悉AI芯片(如

2025-03-03 11:21:28

的物理管腳輸出,同時還需保持設計的電氣完整性。FPGA 復雜度增加也需要高級合成技術,如此才能更快達到時序收斂,最大程度地減少設計變更的影響以及解決特定應用要求。通過使用可選的 FPGA-PCB 優化技術

2018-09-20 11:11:16

,FPGA可以有效地處理深度學習中的大規模并行運算,從而提高深度學習應用的效率。

定制化計算:FPGA的高度可編程性使其可以針對特定的應用場景和算法進行定制化的硬件設計。這意味著,如果深度學習算法發生變化

2024-07-29 17:05:30

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

重要組成部分,所以我們將重點介紹Vitis HLS。LUT 或 SICELUT 或 SICE是構成了 FPGA 的區域。它的數量有限,當它用完時,意味著您的設計太大了!BRAM 或 Block

2022-09-07 15:21:54

連接器)。外部以太網鏈路可以連接到任何交換層次結構。Suchconfiguration可以進行優化,以大規模實現textra大型模型并行性,并可以輕松處理數據并行性或模型和數據并行性的組合。

GAUDI

2023-08-04 06:06:14

利用所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-10 08:00:00

`fpga基礎篇(二):三大并行結構最近小編比較忙,所以這期給大家介紹一個基礎篇,比較簡單,但卻是FPGA編程的基礎。我們知道FPGA與單片機最大的區別就是FPGA是并行執行的,而單片機是串行的,說

2017-04-13 10:23:27

優化 FPGA HLS 設計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

介紹

高級設計能夠以簡潔的方式捕獲設計,從而

2024-08-16 19:56:07

并行編程模型是并行計算,尤其是并行軟件的基礎,也是并行硬件系統的導向,在面臨多核新挑戰的情況下,什么樣的并行編程模型在未來能成為主流,還很難說。至少到目前,還處于百家爭鳴的時代,很多模型提出,很多在應用,下面我們簡單介紹一下當前的并行編程模型現狀。

2019-07-11 08:03:33

;j++) {

b = 2;

}

}

由于這條指令的應用條件十分苛刻,因此很少使用。一般直接通過代碼重構的方式對連續循環進行優化。

參考文檔

官方vitis-hls的ug1399文檔

FPGA并行編程

【流水線】FPGA中流水線的原因和方法

2023-12-31 21:20:08

編譯和編程下載,這被稱為數字邏輯電路的高層次設計方法。 作為現代電子系統設計的主導技術,EDA具有兩個明顯特征:即并行工程(Concurrent Engineering)設計和自頂向下

2008-06-26 16:16:11

,place and route)、仿真及特定目標芯片的適配編譯和編程下載,這被稱為數字邏輯電路的高層次設計方法。---作為現代電子系統設計的主導技術,eda具有兩個明顯特征:即并行工程(concurrent

2013-09-02 15:19:20

,Place And Route)、仿真及特定目標芯片的適配編譯和編程下載,這被稱為數字邏輯電路的高層次設計方法。---作為現代電子系統設計的主導技術,EDA具有兩個明顯特征:即并行工程(Concurrent

2008-06-27 10:26:34

資源。近年來,優化技術沒有發生顯著變化,但應用領域卻以顯著的速度迅速發展。在專業實踐中成功嵌入優化的使用至少需要三個先決條件。它們包括設計問題的數學建模、計算機編程知識和優化技術知識。現在有許多特殊

2023-09-21 07:07:10

應用與生俱來的異構特性,使其需要軟硬件相結合的實現方案。Vivado HLS視頻庫能加快OpenCV函數向FPGA可編程架構的映射。

2021-07-08 08:30:00

1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

fpga的硬件換成我們自己的arm設備。不過經過研究這種設想不可行。個人看法,也許不對哦。!!!!arm是一款多核心,單進程處理器,目前為止arm處理器都不支持多線程。所以多線程概念不能將并行計算優化

2015-12-30 14:33:38

正在改變FPGA編程的方式,其中的新興技術能夠將圖形化程序框圖、甚至是C代碼轉換成數字硬件電路。各行各業紛紛采用FPGA芯片是源于FPGA融合了ASIC和基于處理器的系統的最大優勢。 FPGA能夠提供

2019-04-28 10:04:13

利用所有可能的數據通信方式-沒有功能概述,也沒有對用戶代碼進行優化轉換-支持代碼報告得太晚了-在某些情況下,工具的高效實施是不可能的,例如當必須將太多的加速器映射到硬件部分時。HLS工具無法預先檢測

2021-07-06 08:00:00

Virtual Cable)調試FPGA邏輯

三、硬件加速之—使用PL加速FFT運算(Vivado)

四、硬件加速之—使用PL加速矩陣乘法運算(Vitis HLS)

后四期測評計劃:

五、Vitis AI

2023-10-13 20:11:51

主要可以從“設計的重用”和“抽象層級的提升”這兩個方面來考慮。Xilinx推出的Vivado HLS工具可以直接使用C、C++或System C來對Xilinx系列的FPGA進行編程,從而提高抽象的層級

2020-10-10 16:44:42

HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。LUT 或 SICELUT 或 SICE是構成了 FPGA 的區域。它的數量有限,當它用完時,意味著您的設計太大了!BRAM 或

2022-09-09 16:45:27

的時候,他們必須理解不斷進步的技術,如多核處理器、現場可編程門陣列(FPGA)和高速數據總線,如PCI Express等等。通過將這些技術與NI LabVIEW并行化編程軟件及NI TestStand

2014-12-12 16:02:30

將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架對Xilinx可編程邏輯器件進行開發,可加速算法開發的進程,縮短產品上市時間。HLS基本開發流程如下:(1) HLS工程新建/工程

2021-02-19 18:36:48

多核技術下的并行編程模式課程議程多核時代所帶來的優勢與挑戰化繁為簡——多核編程的趨勢LabVIEW并行編程模式[hide]多核技術下的并行編程模式.pdf[/hide][此貼子已經被作者于2009-12-16 9:21:54編輯過]

2009-12-16 09:21:39

我正在設計一個子板,上面有40個Artix 7(AC7A12T)設備。每臺設備都應具有相同的圖像。我不是一次編程鏈1中的每個器件的串行鏈,而是希望并行執行任務,以便所有FPGA同時進行編程。我似乎

2020-05-14 07:01:03

SDK 2017.4。Xilinx Vivado HLS(High-Level Synthesis,高層次綜合)工具支持將C、C++等語言轉化成硬件描述語言,同時支持基于OpenCL等框架

2021-11-11 09:38:32

,FPGA憑借硬件并行處理能力,能夠實現納秒級響應,遠優于微秒級的嵌入式系統。

功耗效率上,嵌入式系統針對特定應用優化后能效比很高,而FPGA由于可編程特性通常功耗較大,但在特定算法加速場景下可能更高

2025-11-19 06:55:20

相比,能夠為通信和多媒體應用提供高達10倍速的更高的設計和驗證能力。Synphony HLS為ASIC 和 FPGA的應用、架構和快速原型生成最優化的RTL。Synphony HLS解決方案架構圖

2019-08-13 08:21:49

和生成比特流以對FPGA進行編程4 - 將比特流導入并阻塞到SDK中,基于此生成板級支持包(BSP)并與Zedboard連接。順便說一下,SDK的目標是成為我在Vivado HLS中的測試平臺嗎?即在計算機中觀察Zedboard產生的結果是否為例外情況。

2020-03-24 08:37:03

的出現,并行設計和創新在硬件開發中成為可能,對所有企業,無論大或小,FPGA 的使用將變得越來越便宜和現實,也會得到越來越多的應用。業界對它的使用仍然停留在起步階段,但隨著使用量的增加,FPGA 將讓每個企業,無論是單人初創企業還是已經成立的跨國企業,都可以利用高性能并行計算來持續推動技術創新。

2017-12-15 09:09:32

,在單芯片上提供了軟/硬件和I/O可編程性。Zynq SoC在單個器件中集成了一個ARM?雙核Cortex?-A9 MPCore?處理系統、FPGA邏輯和一些關鍵外設。這樣,該器件就能幫助設計人員實現

2014-04-21 15:49:33

的生命周期。第二個原因是速度。微控制器只能按順序一次執行一條指令。由于硬件特性,FPGA 結構本身是并行的。因此它能同時執行多個指令,這對于 FFT 或圖形處理等操作非常有用,因為在按順序執行的處理器上

2018-10-31 11:33:29

,目前主流的異構并行計算平臺是X86+GPU(Graphics Processing Unit,圖形處理器)和X86+FPGA(Field-Programmable Gate Array,現場可編程

2017-09-25 10:06:29

的文章將適合HLS加速的應用場景出發,重點講解數據傳輸的架構優化以及如何編寫高效的硬件描述C代碼。 寫在最后: “為現場可編程門陣列的高層次綜合建立的算法基礎”曾獲IEEE計算機分會年度技術成就獎

2021-01-06 17:52:14

可擴展并行計算技術、結構與編程

2006-03-25 16:43:55 61

61 一種基于FPGA的圖像中值濾波器的硬件實現:隨著超大規模集成電路(VLSI) 技術的不斷發展,圖像的并行處理技術也得到飛速發展。現場可編程門陣列(FPGA) 是在專用集成電路(ASIC) 的基礎

2009-11-01 15:18:41 31

31 本文提出了如何實現在硬件上直接對信號做并行處理,比如測量波形周期、占空比、濾波等;并提出了如何優化FPGA資源。運用NI FPGA提供的可重配置測量I接口技術和可控制底層硬件的

2010-07-17 17:57:07 21

21 采用CPLD/FPGA的VHDL語言電路優化原理設計

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工業標準硬件描述語言,是隨著可編程邏輯器件(PLD)的發展而發展起

2010-03-19 11:38:02 2834

2834

Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 高層次綜合設計最常見的的使用就是為CPU創建一個加速器,將在CPU中執行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 4243

4243

HLS工具 以個人的理解,xilinx將HLS(高層次綜合)定位于更方便的將復雜算法轉化為硬件語言,通過添加某些配置條件HLS工具可以把可并行化的C/C++的代碼轉化為vhdl或verilog,相比于純人工使用vhdl實現圖像算法,該工具綜合出的代碼的硬件資源占用可能較多。

2019-10-12 17:34:00 2937

2937

,Xilinx Vivado HLS是一個高級綜合工具,能夠將C語言轉換成硬件描述語言(HDL),也就是說我們可以用C語言來實現HDL模塊編程了。 圖1 Vivado HLS工作流程 第一位Hacker

2017-02-08 20:01:59 846

846

本實驗練習使用的設計是實驗1并對它進行優化。 步驟1:創建新項目 1.打開Vivado HLS 命令提示符 a.在windows系統中,采用Start>All Programs>Xilinx

2017-02-09 05:07:11 1116

1116

本文介紹了FPGA電源設計并行工程的合理性,講解了并行工程(CE)技術及其作用,討論了FPGA電源系統設計的復雜性和不確定性。

2017-10-13 13:00:35 5

5 DSP并行系統的并行粒子群優化目標跟蹤

2017-10-20 10:54:00 6

6 在使用高層次綜合,創造高質量的RTL設計時,一個重要部分就是對C代碼進行優化。Vivado Hls總是試圖最小化loop和function的latency,為了實現這一點,它在loop

2017-11-16 14:44:58 4126

4126 NI LabVIEW圖形化編程方法不僅省時,還很適合對多核處理器和其他并行硬件[如:現場可編程門陣列(FPGA)]進行編程。 其中一項優勢是:通過2個、4個或更多核將應用程序自動擴展至CPU,通常

2017-11-16 19:30:41 1927

1927

針對大容量固態存儲器中數據錯“位”的問題,目前大多采用軟件ECC 模型進行檢錯和糾錯,但這勢必會極大地影響存儲系統的讀寫性能。基于ECC校驗原理,提出一種并行硬件ECC 模型,并采用FPGA 實現。仿真分析和實驗結果表明:該模型不僅具有良好的糾錯能力,而且顯著地提高了存儲系統的讀寫性能。

2017-11-18 10:32:51 6534

6534

Vviado-HLS基于Xilinx FPGA對C的解析,綜合原理。Vivado-HLS FPGA并行與處理器架構 與處理器架構相比,FPGA結構具有更高的并行。Vivado-HLS對軟件C程序編譯時與處理器編譯是不一樣的執行機制。

2017-11-18 12:23:09 3066

3066

(COTS)計算機集群的日益普及。 直至最近,尚無商業高級工具可以支持針對高性能系統的科學計算應用程序的開發。并行編程是一門深奧的技術,只有那些旨在通過利用自定義設置和低級庫以及通過為特定硬件調優應用程序,來實現最高性能

2017-12-02 09:49:13 641

641

傳統的基于模擬退火的現場可編程門陣列( FPGA)時序驅動布局算法在時延代價的計算上存在一定誤差,已有的時序優化算法能夠改善布局質量,但增加了時耗。針對上述問題,提出一種基于事務內存( TM)的并行

2018-02-26 10:09:04 0

0 HLS,高層綜合)。這個工具直接使用C、C++或SystemC 開發的高層描述來綜合數字硬件,這樣就不再需要人工做出用于硬件的設計,像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來做這個事情。

2018-06-04 01:43:00 7738

7738

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS為FPGA流程提供集成化設計與開發環境,率先支持5G無線應用。

2018-08-30 10:09:32 8283

8283 Vivado HLS是Xilinx公司推出的加速數字系統設計開發工具,直接使用C、C++或SystemC開發的高層描述來綜合數字硬件,替代用VHDL或Verilog實現FPGA硬件設計[6],實現設計的功能和硬件分離,不需要關心低層次具體細節,具有很強的靈活性,有效降低數字系統設計開發周期。

2018-10-04 10:41:00 8295

8295

有效并行縮減和擴展并行性的編程技術。

2018-11-01 06:24:00 2928

2928 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著從 C

2018-12-16 11:19:28 1903

1903

用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。 本項目所需應用與工具:賽靈思HLS、Plunify Cloud 以及 InTime。 前言 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。

2019-09-15 11:56:00 767

767 我們將繼續介紹 Vivado HLS 所支持的 “for循環” 的優化方法。在默認情況下,Vivado HLS 并不會對順序執行的 for 循環優化為并行執行,LOOP_MERGE 約束提供了這樣一種可能:for 循環并行執行。本講結合案例介紹了循環合并的三個主要規則。

2019-08-01 16:59:21 3256

3256 RTL代碼),也可以在某些場合加速設計與驗證(例如在FPGA上實現OpenCV函數),但個人還是喜歡直接從RTL入手,這樣可以更好的把握硬件結構。Xilinx官方文檔表示利用HLS進行設計可以大大加速設計進度:

2019-07-31 09:45:17 7434

7434

應用能夠有更高的性能,您需要熟悉如下介紹的硬件。另外,將會介紹編譯優化選項,有助于將您的 OpenCL 應用更好的實現 RTL 的轉換和映射,并部署到 FPGA 上執行。

2020-07-16 17:58:28 7215

7215

Unroll 指令在 for 循環的代碼區域進行優化,這個指令不包含流水線執行的概念,單純地將循環體展開使用更多地硬件資源實現,保證并行循環體在調度地過程中是彼此獨立的。

2021-01-14 09:41:31 3250

3250 Python編程就可以調用FPGA模塊,不需要懂Verilog/VHDL硬件編程就可以享受FPGA可并行計算、接口可方便擴展和可靈活配置帶來的諸多好處

2022-02-08 10:59:29 5278

5278 HLS 優化設計的最關鍵指令有兩個:一個是流水線 (pipeline) 指令,一個是數據流(dataflow) 指令。正確地使用好這兩個指令能夠增強算法地并行性,提升吞吐量,降低延遲但是需要遵循一定的代碼風格。

2021-02-01 06:28:14 7

7 本系列教程演示如何使用xilinx的HLS工具進行算法的硬件加速。

2021-06-17 10:20:33 10326

10326

ADC和DAC是FPGA與外部信號的接口,從數據接口類型的角度劃分,有低速的串行接口和高速的并行接口。FPGA經常用來采集中高頻信號,因此使用并行ADC和DAC居多。本文將介紹如何使用FPGA驅動并行ADC和并行DAC芯片。

2022-04-21 08:55:22 8245

8245 FPGA的布局布線軟件向來跑得很慢。事實上,FPGA供應商已經花了很大的精力使其設計軟件在多核處理器上運行得更快。

2022-05-25 09:50:10 1939

1939 HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 2261

2261

基于硬件描述語言HDL,抽象出HLS(High-Level Synthesis)(翻譯為高層次綜合?怎么聽起來都沉得別扭)技術,通過高層設計去隱藏很多底層邏輯和細節,讓FPGA的開發更加簡單。

2022-09-05 09:12:48 1208

1208 軟件編譯器講高級語言翻譯成為機器語言。主要關注的語言的語法轉換規則,相比之下,HLS 的翻譯難度更大一些,模塊中的語句形式上是前后順序排列。但是HLS盡力轉換成為并行執執行的硬件邏輯。

2022-10-10 14:50:29 2419

2419 電子發燒友網站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費下載

2022-10-27 16:49:59 0

0 實現,無縫的將硬件仿真環境集合在一起,使用軟件為中心的工具、報告以及優化設計,很容易的在 FPGA 傳統的設計工具中生成 IP。 傳統的 FPGA 開發,首先寫 HDL 代碼,然后做行為仿真,最后做綜合

2022-12-02 12:30:02 7407

7407 對于FPGA來說,設計人員可以充分利用其可編程能力以及相關的工具來準確估算功耗,然后再通過優化技術來使FPGA和相應的硬件設計滿足其功耗方面的要求。

2022-12-29 14:46:14 2379

2379 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發 算法。這將提升FPGA 算法開發的生產力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 6467

6467 電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 3

3 軟硬件工程之間的界限比我們看到的更模糊。稱之為現場可編程門陣列 (FPGA) 的器件,其物理屬性可通過使用硬件描述語言 (HDL) 來操控,該器件可在軟硬件編程之間架起一座橋梁。 但人們通常認為

2023-07-04 08:35:01 3888

3888

因為NI LabVIEW是數據流編程語言,開發者們可以編寫并行的應用程序,這些應用程序可以直接映射到并行的硬件(如多核心處理器和FPGA等)上以獲得最優異的性能。這篇白皮書討論了什么是數據流編程以及為什么說NI LabVIEW是多核系統編程的首選。

2023-10-27 17:08:53 904

904 本篇博客介紹 VVAS 框架所支持調用的 H/W(HLS) 內核。 H/W 內核指的是使用 HLS 工具生成的在 FPGA 部分執行的硬件功能模塊。

2023-08-04 11:00:43 1647

1647

需要手工在 C++ 代碼里明確指定可并行執行的任務(用 task,添加頭文件 hls_task.h),同時可并行執行的 task 接口(對應 C++ 函數的形參)必須是 stream 或 stream_of_blocks。

2023-08-11 11:23:50 1276

1276 電子發燒友網站提供《Vitis HLS:使用任務級并行性的高性能設計.pdf》資料免費下載

2023-09-13 17:21:04 2

2 電子發燒友網站提供《基于FPGA的ARM并行總線設計原理.pdf》資料免費下載

2023-10-10 09:31:31 1

1 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 AMD Vitis 高層次綜合 ( HLS ) 已成為自適應 SoC 及 FPGA 產品設計領域的一項顛覆性技術,可在創建定制硬件設計時實現更高層次的抽象并提高生產力。Vitis HLS 通過將 C

2023-12-05 09:10:14 1160

1160

FPGA(Field-Programmable Gate Array)是一種可編程邏輯技術,它使用可重構的硬件單元(如門陣列和查找表)來實現電路功能。相比傳統的專用集成電路(ASIC),FPGA具有

2024-02-04 15:26:30 3079

3079 隨著人工智能技術的飛速發展,對計算性能的需求也日益增長。FPGA(現場可編程門陣列)作為一種高性能、低功耗、可靈活編程的硬件平臺,正逐漸在 AI 領域嶄露頭角,展現出獨特的優勢,為 AI 應用的落地

2025-01-06 17:37:10 2318

2318

電子發燒友App

電子發燒友App

評論