大家好,歡迎Vivado的一個(gè)快速演示,它是xilinx新的設(shè)計(jì)套件,應(yīng)用到7系列和以上的系列器件。

2012-04-25 08:55:55 3049

3049 電子發(fā)燒友網(wǎng)訊 :Altera 公司與FPGA高性能知識(shí)產(chǎn)權(quán)(IP)內(nèi)核領(lǐng)先供應(yīng)商Northwest Logic2012年11月14號(hào)宣布,開(kāi)始提供硬件成熟的1,600 Mbps低延時(shí)DRAM (RLDRAM) 3存儲(chǔ)器接口解決方案,可用于

2012-11-15 09:32:59 1184

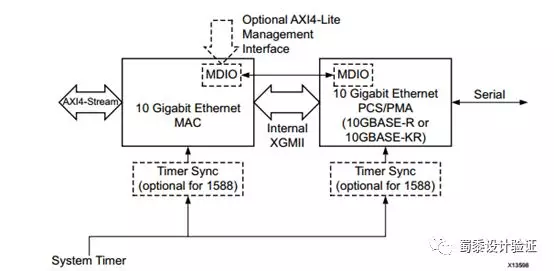

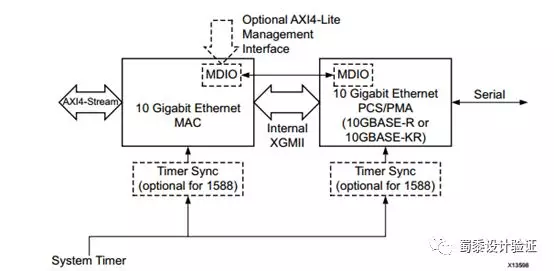

1184 IP核描述 10 Giga Ethernet Sub System , 參考文檔PG157: https://www.xilinx.com/support/documentation

2020-12-30 12:56:30 5312

5312

鎖相環(huán)基本上是每一個(gè)fpga工程必不可少的模塊,之前文檔xilinx 7 系列FPGA時(shí)鐘資源對(duì)xilinx fpga的底層時(shí)鐘資源做過(guò)說(shuō)明,但是對(duì)于fpga的應(yīng)用來(lái)說(shuō),使用Clocking Wizard IP時(shí)十分方便的。

2023-06-12 17:42:03 8964

8964

上文XILINX FPGA IP之Clocking Wizard詳解說(shuō)到時(shí)鐘IP的支持動(dòng)態(tài)重配的,本節(jié)介紹通過(guò)DRP進(jìn)行MMCM PLL的重新配置。

2023-06-12 18:24:03 16812

16812

推出的FPGA設(shè)計(jì)工具集搭配Zynq UltraScale+ RFSoC會(huì)提供所有生產(chǎn)用的IP以及一些通用功能的IP庫(kù),用戶(hù)在搭建自己設(shè)計(jì)時(shí)可以用到。這些IP集成模塊可以輕松的導(dǎo)入Xilinx Vivado設(shè)計(jì)工具,所有IP都支持AXI4協(xié)議并且可以無(wú)縫對(duì)接Xilinx提供的IP資源。

2019-02-13 10:53:59 4841

4841 在win8.1 pc上使用Vivado 2014.1,MIG IP生成器在啟動(dòng)時(shí)收到Windows錯(cuò)誤。相同的安裝文件已加載到win7 pc上,MIG IP生成器運(yùn)行正常。在Win8.1機(jī)器上,我

2018-12-07 11:18:46

怎樣能使35集成器運(yùn)行起來(lái)?連完電路,三極管導(dǎo)通,35應(yīng)該通電工作輸出高電平才對(duì)。為啥工作不了?

2021-10-20 14:06:11

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個(gè)文件對(duì)我們比較有用,假設(shè)生成了一個(gè) asyn_fifo 的核,則

2012-08-12 12:21:36

XILINX ISE 14.7,我想建立一個(gè)工程,里面要調(diào)用之前別人的包含SRAM IP核的模塊,需要使用.v和.ngc文件,可是不知道那個(gè).ngc文件該怎么使用,是copy到自己工程目錄然后在工程里面添加進(jìn)去嗎?為什么加進(jìn)去后我的工程文件層次就亂了。。。

2015-04-18 14:21:49

下載到板子測(cè)試的時(shí)候,卻得不到輸出數(shù)據(jù),求大神幫忙看看是否是代碼的問(wèn)題呢?多謝啦library IEEE;use IEEE.STD_LOGIC_1164.ALL;use

2016-12-23 12:53:46

最近收集了一些 xilinx FIFO IP的資料整理了一下拿出來(lái)大家分享分享。

2013-05-11 08:36:29

嗨,出于移植和維護(hù)的原因,我需要安裝Xilinx ISE 10.1 Foundation,完全支持所有FPGA,尤其是Virtex-5 XC5VFX70T。我有這個(gè)版本的有效許可證(即注冊(cè)ID)但我

2018-11-15 11:30:24

Xilinx TCP_IP協(xié)議實(shí)現(xiàn)

2012-08-17 09:03:39

大家好,我擁有Xilinx Vivavo 14.4和Matlab 2015a,當(dāng)我試圖將兩者集成到系統(tǒng)生成器時(shí),我得到的錯(cuò)誤是“沒(méi)有matlab exixting的余地”我該怎么辦,請(qǐng)幫助我

2020-05-05 08:09:03

嗨, 我正在尋找一個(gè)數(shù)字多相上變頻器。 我在Altera的應(yīng)用筆記和設(shè)計(jì)實(shí)例中找到了一些。 只是想知道Xilinx有沒(méi)有任何應(yīng)用筆記和系統(tǒng)生成器設(shè)計(jì)實(shí)例?謝謝,將以上來(lái)自于谷歌翻譯以下為原文Hi,I

2019-01-30 10:08:42

我在Xilinx核心生成器(vivado 2016.2)生成的AsynFifo(獨(dú)立時(shí)鐘塊Ram,F(xiàn)IFO生成器版本13.1)上遇到了問(wèn)題。設(shè)置如下:輸入數(shù)據(jù)寬度:260輸入數(shù)據(jù)寬度:520問(wèn)題是當(dāng)

2020-05-05 17:41:49

`Xilinx系列FPGA芯片IP核詳解(完整高清書(shū)簽版)`

2017-06-06 13:15:16

有沒(méi)有大神可以提供xilinx FPGA的FFT IP核的調(diào)用的verilog 的參考程序,最近在學(xué)習(xí)FFT的IP核的使用,但是仿真結(jié)果有問(wèn)題,所以想找些參考設(shè)計(jì),謝謝

2016-12-25 17:05:38

嗨,我在系統(tǒng)生成器2014中使用黑盒子.4在模擬模式下選擇vivado模擬器。如果我運(yùn)行該項(xiàng)目它正常工作,但如果我在系統(tǒng)生成器或黑盒vhdl中更改某些內(nèi)容,則會(huì)出現(xiàn)此錯(cuò)誤:Xilinx模塊庫(kù)中發(fā)

2018-10-30 11:07:57

本帖最后由 何立立 于 2018-1-9 17:29 編輯

在Microblaze系統(tǒng)中添加用戶(hù)自定義IP,可以使用Xilinx Platform Studio (XPS) Create

2018-01-09 14:53:42

以及用于約束文件的編輯 Constraint Editor 等。? 綜合(Synthesis) ISE 的綜合工具不但包括了 Xilinx 自身提供的綜合工具 XST,同時(shí)還可以集成 Mentor

2018-09-27 09:29:57

介紹ViCANdo工具支持的另外一個(gè)功能:XCP解析功能集成。

2020-12-28 07:41:52

Vivado中xilinx_courdic IP核(求exp指數(shù)函數(shù))使用

2021-03-03 07:35:03

本帖最后由 lee_st 于 2017-11-2 15:01 編輯

《FPGACPLD設(shè)計(jì)工具──Xilinx+ISE使用詳解》第 1 章 ISE 系統(tǒng)簡(jiǎn)介

2017-11-02 10:02:32

除了在Xilinx官網(wǎng)上在哪里能下載到Xilinx IP Core 及l(fā)icense? 如FFTFIRCORDIC核等!

2013-06-20 23:51:39

Logic組件仍在使用中。如果我使用Xilinx / Logicore DMA,請(qǐng)確認(rèn)它沒(méi)有使用任何將超時(shí)的Northwest Logic DMA系統(tǒng)。如果它不使用和Northwest Logic組件,我將在我能夠達(dá)到銷(xiāo)售時(shí)立即訂購(gòu)該板,并且在該板中不存在與以太網(wǎng)相關(guān)的另一個(gè)問(wèn)題。謝謝!

2019-10-08 07:54:35

System View公司是一家位于美國(guó)加州的早期創(chuàng)業(yè)型公司,公司的主要產(chǎn)品和業(yè)務(wù)是設(shè)計(jì)開(kāi)發(fā)當(dāng)今嵌入式系統(tǒng)集成開(kāi)發(fā)所使用的工具,打破傳統(tǒng),推出更加高效便捷的開(kāi)發(fā)工具。近期該公司推出一款嵌入式系統(tǒng)開(kāi)發(fā)工具,命名為“可視化系統(tǒng)集成器(VSI)”。

2019-10-09 07:56:13

設(shè)備接口,如 NVMe? 固態(tài)盤(pán)和主機(jī)處理器內(nèi)置 100G EMAC 硬 IP,用于高速 100G 網(wǎng)絡(luò)接口DDR4 和 LPDDR4 內(nèi)存接口協(xié)同優(yōu)化工具和調(diào)試方法Vivado? ML, Vitis

2022-11-25 16:29:20

大家好我可以在Matlabwith Vivado上安裝Xilinxsystem生成器嗎?有了ISE,有一個(gè)應(yīng)用程序調(diào)用System Generator Matlab Configuration

2018-12-27 10:57:02

HI, 我正在嘗試使用浮點(diǎn)IP在Zedboard上生成一個(gè)系統(tǒng)(SoC)(使用VIVADO 2016.4)。由于這個(gè)IP具有分層接口,我使用AXI DMA將此ip添加到AXI系統(tǒng)總線。但現(xiàn)在我的問(wèn)題是如何使用Xilinx SDK檢查此IP? (表示如何向IP發(fā)送輸入以及如何檢查輸出)。謝謝

2020-05-26 14:04:10

,它們具有eval和完整版本的IP,但是當(dāng)您使用設(shè)計(jì)中提供的tcl腳本創(chuàng)建項(xiàng)目時(shí),它使用NWL IP的eval版本創(chuàng)建項(xiàng)目。我想知道是否有人知道eval版本的實(shí)際限制是什么,以及是否可以使用完整版IP的許可證來(lái)使用Northwest Logic提供的后端DMA創(chuàng)建新設(shè)計(jì)。祝你有個(gè)好的一天,史蒂夫

2019-09-19 08:25:52

我想使用系統(tǒng)生成器來(lái)生成sinc信號(hào)。但我不知道在哪里可以獲得這個(gè)系統(tǒng)生成器?這是xilinx ISE設(shè)計(jì)工具的一部分。如果是這樣,請(qǐng)告訴我如何使用它來(lái)生成sinc信號(hào)?謝謝以上來(lái)自于谷歌翻譯以下

2019-01-28 06:37:12

如何利用Xilinx FPGA和存儲(chǔ)器接口生成器簡(jiǎn)化存儲(chǔ)器接口?

2021-05-06 07:23:59

您好,我被要求執(zhí)行序列生成器。我已經(jīng)用紙做過(guò)一切,但我不知道如何在Xilinx上正確創(chuàng)建它。我完成了轉(zhuǎn)換表和輸出表。我的輸出函數(shù)已經(jīng)用karnaugh等進(jìn)行了簡(jiǎn)化。但是當(dāng)我實(shí)現(xiàn)它時(shí),我認(rèn)為它在

2019-01-10 10:39:50

將Xilinx SDK集成到現(xiàn)有的構(gòu)建系統(tǒng)中?除了確保ARM工具鏈二進(jìn)制文件是可訪問(wèn)的之外,還需要使用像gcc -'s -isystem選項(xiàng)這樣的東西來(lái)確保交叉編譯器的頭文件文件在本機(jī)標(biāo)頭之前找到。我也

2020-05-20 10:06:37

我想用ip核心生成器實(shí)現(xiàn)DCM,但我無(wú)法實(shí)現(xiàn)設(shè)計(jì)。我有這個(gè)錯(cuò)誤。我認(rèn)為問(wèn)題出在.ucf檔案中。請(qǐng)幫幫我

2019-07-24 12:11:54

大家好!!! 我正在使用xilinx系統(tǒng)生成器實(shí)現(xiàn)ofdm。在發(fā)送器部分,對(duì)于星座映射,我使用的是16位QAM,這是一個(gè)matlab文件。通過(guò)使用“Mcode塊”,我有點(diǎn)將matlab包含

2019-04-19 10:32:12

無(wú)線充方案:IP6806 5W過(guò)QI認(rèn)證 全集成概述IP6806 是一款無(wú)線充電發(fā)射端控制SoC 芯片, 兼容WPC Qi v1.2.4 最新標(biāo)準(zhǔn),支持 A11 或A11a 線圈,支持5W、蘋(píng)果

2021-09-11 10:03:44

你能告訴我用戶(hù)邏輯是什么嗎?我理解的是user_logic是vhdl模板的主/從ip實(shí)現(xiàn)的?我對(duì)嗎?無(wú)論如何,如果你能詳細(xì)說(shuō)明一下,我會(huì)很高興非常感謝您的幫助!!

2019-11-11 13:54:56

。(http://www.xilinx.com/support/answers/54025.html)但是我找不到與我正在使用的完全相同的內(nèi)存。我嘗試過(guò)使用xilinx mig(內(nèi)存接口生成器)ip并創(chuàng)建

2020-04-23 08:44:28

親愛(ài)的Xilinx:光纖通道IP核支持VII pro,V4 FX,它們都有ppc硬核,但自從V5 FXT宣布這么長(zhǎng)時(shí)間以來(lái),為什么V5 FXT不支持這個(gè)核心?V4 FX中的光纖通道IP核可以4Gbps運(yùn)行,但V5 LXT只能運(yùn)行2Gbps。謝謝

2020-06-02 12:30:33

IJF編碼是什么原理?如何實(shí)現(xiàn)IJF編碼?采用FPGA和集成器件來(lái)實(shí)現(xiàn)IJF編碼

2021-04-13 06:56:04

使用的人太少了,xilinx就沒(méi)有做這些加密IP的庫(kù),也不提供任何技術(shù)支持,除非你自己去折騰。。。除了仿真工具,另外也有一些第三方的EDA的工具可以用于XILINX的FPGA開(kāi)發(fā)。下面是我自己從

2013-03-14 11:49:58

FPGACPLD設(shè)計(jì)工具——Xilinx ISE使用詳解的主要內(nèi)容:第1章 ISE系統(tǒng)簡(jiǎn)介第2章 工程管理器與設(shè)計(jì)輸入工具第3章 ModelSim仿真工具第4章 ISE中集成的綜合工具第5章 約束第6章

2009-07-24 16:06:58 198

198 Xilinx ISE Design Suite 12.4 現(xiàn)在將更好地幫助您全面提升和改進(jìn)設(shè)計(jì)。

Spartan-6 FPGA 將靜態(tài)功耗削減 30%,性能提升 12%

AMBA 4 AXI4 工具和 IP 支持現(xiàn)已開(kāi)始投產(chǎn),可滿(mǎn)足即插即用

2010-12-23 21:55:07 1310

1310

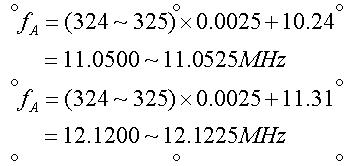

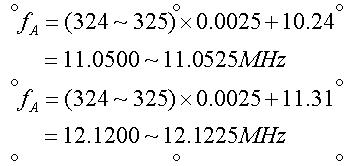

CMOS集成雙環(huán)合成器

環(huán)路的輸出頻率

2008-04-21 14:32:57 987

987

什么是Application Logic

英文縮寫(xiě): Application Logic

中文譯名: 應(yīng)用邏輯

分 類(lèi): IP與多媒體

解 釋: 一個(gè)應(yīng)

2010-02-22 10:17:18 1045

1045 集成鎖相環(huán)頻率合成器,什么是集成鎖相環(huán)頻率合成器

頻率合成的歷史

頻率合成器被人們喻為眾多電子系統(tǒng)

2010-03-23 11:45:44 956

956 MIPS和Virage Logic合作提供優(yōu)化嵌入式內(nèi)存IP

美普思科技公司(MIPS Technologies, Inc.)和備受半導(dǎo)體業(yè)界信賴(lài)的IP伙伴Virage Logic 共同宣布

2010-04-07 09:44:26 716

716 通過(guò)將第三方IP集成到NI LABVIEW軟件中,您可以使用許多為XILINX現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)精調(diào)過(guò)的算法實(shí)現(xiàn)高性能,并且提高代碼重用度。LABVIEW FPGA模塊為導(dǎo)入外部IP提供了兩個(gè)方法:組件級(jí)知識(shí)產(chǎn)權(quán)(CLIP)節(jié)點(diǎn)和結(jié)合XILINX核心生成器的IP集成節(jié)點(diǎn)。本技

2011-03-15 13:25:58 98

98 Xilinx 是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商,研發(fā)、制造并銷(xiāo)售應(yīng)用范圍廣泛的

高級(jí)集成電路、軟件設(shè)計(jì)工具以及定義系統(tǒng)級(jí)功能的 IP(Intellectual Property)核,長(zhǎng)期

2016-02-18 18:18:23 0

0 Xilinx FPGA工程例子源碼:Xilinx TCP_IP協(xié)議實(shí)現(xiàn)

2016-06-07 14:54:57 33

33 Xilinx FPGA工程例子源碼:Xilinx 的IP:1024點(diǎn)FFT快速傅立葉變換

2016-06-07 15:07:45 51

51 FPGA學(xué)習(xí)資料教程之Xilinx-FPGA高級(jí)開(kāi)發(fā)工具,感興趣的可以看看。

2016-09-01 15:27:27 0

0 Xilinx采用先進(jìn)的 EDA 技術(shù)和方法,提供了全新的工具套件Vivado,面向未來(lái)“All-Programmable”器件。Vivado開(kāi)發(fā)套件提供全新構(gòu)建的SoC 增強(qiáng)型、以IP和系統(tǒng)為中心

2017-02-08 04:10:11 881

881 Synopsys公司發(fā)布了新DesignWare 混合IP原型工具包,其集成了基于ARMv8基礎(chǔ)平臺(tái)的虛擬開(kāi)發(fā)工具包(VDK)和DesignWare IP原型工具包。 混合IP原型工具包為軟件工程

2017-02-09 03:56:21 493

493 Xilinx針對(duì)不同類(lèi)型的調(diào)試IP核,提供了不同的核生成器。本節(jié)重點(diǎn)介紹Xilinx Core Generator Tool(Xilinx IP核生成器)所支持的ChipScope Pro調(diào)試IP核ICON、ILA、VIO和ATC2及其屬性

2017-02-11 07:14:11 1113

1113

當(dāng)ISE調(diào)用ModelSim進(jìn)行仿真的時(shí)候,如果在FPGA設(shè)計(jì)中使用了Xilinx提供的的IP core或者其他的原語(yǔ)語(yǔ)句,ModelSim不添加Xilinx相應(yīng)的庫(kù)文件的話,是無(wú)法仿真的。

2017-02-11 15:22:37 1766

1766

Express Logic 的 ThreadX RTOS 現(xiàn)已支持 MIPS 64 位 I6400 CPU 2017 年 3 月 14 日 ─ Imagination Technologies

2017-04-10 10:12:49 2004

2004 。 使用Xilinx內(nèi)核生成器IP函數(shù)實(shí)現(xiàn)FPGA VI中不同的Xilinx內(nèi)核生成器IP。LabVIEW使用IP集成節(jié)點(diǎn)實(shí)現(xiàn)上述函數(shù)。函數(shù)名稱(chēng)和說(shuō)明來(lái)自于Xilinx數(shù)據(jù)表。單擊Xilinx內(nèi)核生成器配置對(duì)話框的數(shù)據(jù)表按鈕,了解IP內(nèi)核的詳細(xì)信息。 選板隨終端變化且僅顯示FPGA設(shè)備系列支持的IP。

2017-11-18 05:54:05 1780

1780 僅支持FPGA設(shè)備支持的IP。并非全部FPGA設(shè)備系列均支持所有IP。關(guān)于FPGA設(shè)備支持的詳細(xì)信息,見(jiàn)IP數(shù)據(jù)表。單擊Xilinx內(nèi)核生成器配置對(duì)話框的數(shù)據(jù)表按鈕,了解IP內(nèi)核的詳細(xì)信息。 注: Xilinx提供并維護(hù)Xilinx內(nèi)核生成器IP。由于Xilinx可能不再支持或更新早期版本的IP內(nèi)核。

2017-11-18 05:55:51 5498

5498 LabVIEW使用IP集成節(jié)點(diǎn)方便的整合Xilinx內(nèi)核生成IP至FPGA VI。按照下列步驟添加Xilinx內(nèi)核生成器IP至FPGA VI。 1、在支持的FPGA終端下新建一個(gè)空白VI,并顯示VI

2017-11-18 05:56:22 2433

2433 All Programmable技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc.,(NASDAQ:XLNX))宣布,將在2月7日- 10日歐洲最大規(guī)模系統(tǒng)集成展ISE 2018

2018-02-09 12:55:26 8209

8209 Xilinx是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商。Xilinx研發(fā)、制造并銷(xiāo)售范圍廣泛的高級(jí)集成電路、軟件設(shè)計(jì)工具以及作為預(yù)定義系統(tǒng)級(jí)功能的IP(Intellectual Property)核。

2018-03-23 11:00:29 42634

42634 用戶(hù)可以使用IP集成器連接IP模塊創(chuàng)建復(fù)雜的系統(tǒng)設(shè)計(jì)。通過(guò)接口構(gòu)建基于模塊的設(shè)計(jì),一般情況下接口包含多個(gè)總線和大量的信號(hào)線。因此,為了方便在硬件上調(diào)試那些包含大量接口的設(shè)計(jì),就需要驗(yàn)證設(shè)計(jì)的接口連接。

2018-04-18 15:28:24 3578

3578

在xilinx下每種操作其實(shí)都對(duì)應(yīng)著一種工具,邏輯綜合,網(wǎng)表與constraint fie的合并,布局布線等等。下面就對(duì)各個(gè)工具做一個(gè)總結(jié)。 1、XST(Xilinx Synthesis

2018-05-28 11:42:14 10050

10050 DocNav(Documentation Navigator)可以看作是Xilinx的文檔、視頻“集裝箱”,幾乎所有與芯片、開(kāi)發(fā)工具、設(shè)計(jì)方法、IP等相關(guān)的文檔和視頻都可以在這里找到,更重要的是它

2018-06-05 05:05:00 21810

21810 Xilinx(賽靈思)是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商。Xilinx研發(fā)、制造并銷(xiāo)售范圍廣泛的高級(jí)集成電路、軟件設(shè)計(jì)工具以及作為預(yù)定義系統(tǒng)級(jí)功能的IP(Intellectual

2018-11-26 08:21:00 2742

2742

通過(guò)探索答案,文檔或使用社區(qū)論壇與同行聯(lián)系,在Xilinx支持站點(diǎn)上查找解決方案。

2019-01-16 07:40:00 3005

3005 了解Vivado中的Logic Debug功能,如何將邏輯調(diào)試IP添加到設(shè)計(jì)中,以及如何使用Vivado Logic Analyzer與邏輯調(diào)試IP進(jìn)行交互。

2018-11-30 06:22:00 3889

3889 即將推出的Xilinx ST 2059 IP內(nèi)核的早期技術(shù)演示展示了將時(shí)序和同步功能集成到ST 2022網(wǎng)絡(luò)中,并將針對(duì)KC705Kintex?-7評(píng)估平臺(tái)。

2018-11-28 06:19:00 3671

3671 Xilinx Logicore IP直接數(shù)字合成器(DDS)編譯核心采用Axi4流兼容接口,實(shí)現(xiàn)高性能、優(yōu)化的相位生成和相位-正弦電路。

2019-09-09 08:00:00 23

23 xilinx logicore?ip塊內(nèi)存生成器(bmg)核心是一個(gè)高級(jí)內(nèi)存構(gòu)造函數(shù),它使用xilinx fpgas中的嵌入式塊ram資源生成面積和性能優(yōu)化的內(nèi)存。用戶(hù)可以快速創(chuàng)建優(yōu)化的內(nèi)存,以利

2019-10-30 08:00:00 5

5 DDR對(duì)于做項(xiàng)目來(lái)說(shuō),是必不可少的。一般用于數(shù)據(jù)緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開(kāi)發(fā)工具:Vivado

2020-11-26 15:02:11 10426

10426

Xilinx FIR IP的介紹與仿真 1 xilinx fir ip 簡(jiǎn)介 1)符合 AXI4-Stream 的接口 2)高性能有限脈沖響應(yīng)(FIR),多相抽取器,多相內(nèi)插器,半帶,半帶抽取器和半

2020-10-30 12:29:01 2178

2178 Xilinx LogiCORE IP塊內(nèi)存生成器(BMG)內(nèi)核是一種高級(jí)內(nèi)存構(gòu)造函數(shù),它使用XilinxFPGAs中的嵌入式塊RAM資源生成區(qū)域和性能優(yōu)化的內(nèi)存。

2020-12-09 15:31:00 22

22 本文介紹如何在 vivado 開(kāi)發(fā)教程(一) 創(chuàng)建新工程 的基礎(chǔ)上, 使用IP集成器, 創(chuàng)建塊設(shè)計(jì)。

2022-02-08 10:47:39 3601

3601

使用具有PFD輸出的合成器的HMC設(shè)計(jì)工具

2021-05-09 08:45:35 2

2 Processor is ready. Configure programable logic.在新專(zhuān)欄 Rapid TCP/IP on Zynq 中,將圍繞 Xilinx Zynq 系列芯片,從 SDK 驅(qū)動(dòng),PS-...

2022-02-07 10:59:19 1

1 Xilinx快速傅立葉變換(FFT IP)內(nèi)核實(shí)現(xiàn)了Cooley-Tukey FFT算法,這是一種計(jì)算有效的方法,用于計(jì)算離散傅立葉變換(DFT)。

2022-03-30 11:01:31 4200

4200 簡(jiǎn)介 Librtmp是用于RTMP流的工具包。 支持所有形式的RTMP,包括rtmp://,rtmpt://,rtmpe://,rtmpte://和rtmps://。 集成 在OHOS中集成 首先在

2022-04-06 09:32:15 1

1 DVK是用于解碼器IP設(shè)計(jì)和合規(guī)性驗(yàn)證的比特流和軟件工具鏈。它是芯片RTL設(shè)計(jì)、目標(biāo)設(shè)備集成(如智能手機(jī)、智能電視、機(jī)頂盒)、發(fā)貨給客戶(hù)前的軟件堆棧驗(yàn)證的必備工具。

2022-10-08 11:06:11 2151

2151 電子發(fā)燒友網(wǎng)站提供《關(guān)于Ultra96的Xilinx DDS編譯器IP教程.zip》資料免費(fèi)下載

2022-12-13 10:17:40 1

1 Xilinx LabTools工具是Xilinx FPGA單獨(dú)的編程和調(diào)試工具,是從ISE或Vivado中獨(dú)立出來(lái)的實(shí)驗(yàn)室工具,只能用來(lái)下載FPGA程序和進(jìn)行ILA調(diào)試,支持所有的FPGA系列,無(wú)需

2023-03-28 10:46:56 9161

9161 DDS(Direct Digital Frequency Synthesizer) 直接數(shù)字頻率合成器,本文主要介紹如何調(diào)用Xilinx的DDS IP核生成某一頻率的Sin和Cos信號(hào)。

2023-07-24 11:23:29 8502

8502

IP6822 全集成15W無(wú)線充方案soc 支持PD快充輸入BPP認(rèn)證ip6822規(guī)格書(shū)

IP6805U IP6806 IP6822 IP6808 附相關(guān)原理圖/規(guī)格書(shū)/BOM等現(xiàn)ip

2023-08-24 10:37:47 3057

3057

在給Vivado中的一些IP核進(jìn)行配置的時(shí)候,發(fā)現(xiàn)有Shared Logic這一項(xiàng),這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 3014

3014

上文XILINX FPGA IP之FIFO對(duì)XILINX FIFO Generator IP的特性和內(nèi)部處理流程進(jìn)行了簡(jiǎn)要的說(shuō)明,本文通過(guò)實(shí)際例子對(duì)該IP的使用進(jìn)行進(jìn)一步的說(shuō)明。本例子例化一個(gè)讀數(shù)

2023-09-07 18:31:35 3352

3352

Configurator代碼生成器中。此次集成將為Renesas新推出的R9A02G021系列MCU提供端到端的開(kāi)發(fā)工具支持,標(biāo)志著瑞薩電子在通用應(yīng)用領(lǐng)域首次推出32位RISC-V MCU的重大突破。

2024-05-10 14:25:31 1527

1527 IP2320是一款支持雙節(jié)串聯(lián)的升壓充電芯片,IP2320集成功率MOS,采用同步開(kāi)關(guān)充電,外圍少BOM成本低, 5V輸入同步升壓充電,恒壓充電電壓外部電阻可調(diào),恒流充電電流外部電阻可調(diào),支持NTC

2024-05-18 00:39:53 0

0 在使用FPGA的時(shí)候,有些IP核是需要申請(qǐng)后才能使用的,本文介紹如何申請(qǐng)xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

。Shift RAM IP 提供靈活的輸入/輸出接口和控制信號(hào),支持同步操作,廣泛應(yīng)用于數(shù)字信號(hào)處理(DSP)、通信系統(tǒng)和數(shù)據(jù)流處理。

2025-05-14 09:36:22 913

913

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論