本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時(shí)序邏輯來(lái)詳細(xì)的分析。

2018-04-18 09:06:24 18789

18789

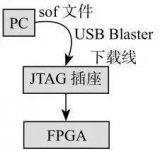

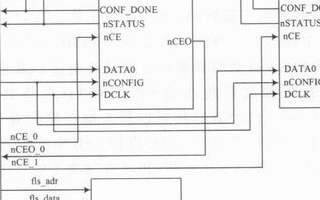

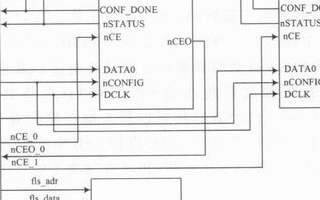

在需要多個(gè)FPGA芯片的應(yīng)用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過(guò)“成組”加載方式同時(shí)加載;

2023-02-20 10:18:27 8049

8049

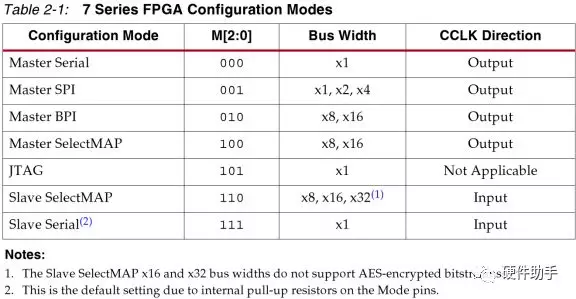

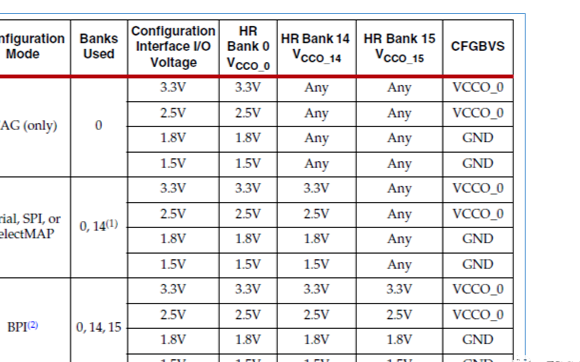

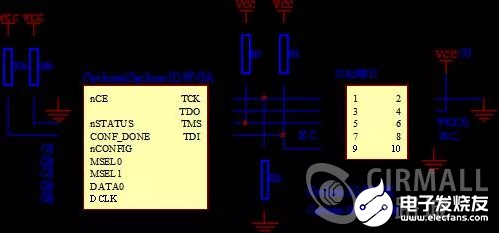

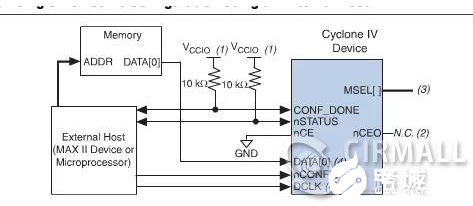

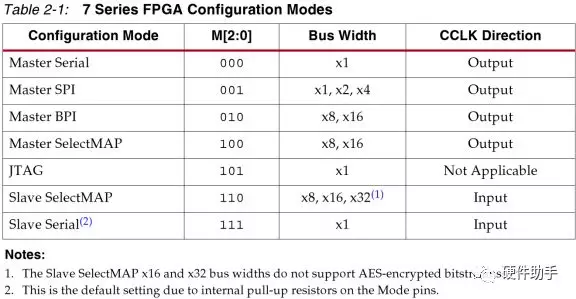

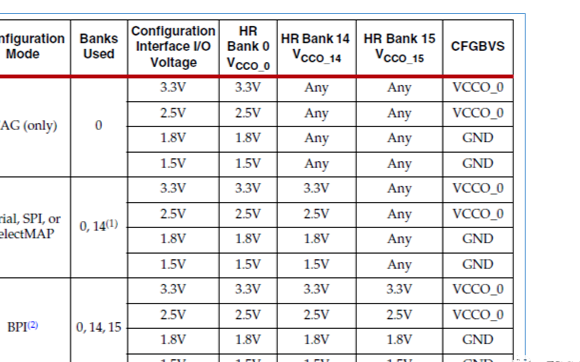

本文旨在通過(guò)講解不同模式的原理圖連接方式,進(jìn)而配置用到引腳的含義(手冊(cè)上相關(guān)引腳含義有四、五頁(yè),通過(guò)本文理解基本上能夠記住所有引腳含義以及使用場(chǎng)景),熟悉xilinx 7系列配置流程,以及設(shè)計(jì)原理圖時(shí)需要注意的一些事項(xiàng),比如flash與FPGA的上電時(shí)序。

2025-08-30 14:35:28 9296

9296

當(dāng)FPGA 完成上電自動(dòng)加載初始化的比特流后,可以通過(guò)觸發(fā)FPGA 內(nèi)部的多重啟動(dòng)事件使得FPGA 從外部配置存儲(chǔ)器(SPI FLASH)指定的地址自動(dòng)下載一個(gè)新的比特流來(lái)重新配置。

2015-02-02 11:09:51 1629

1629

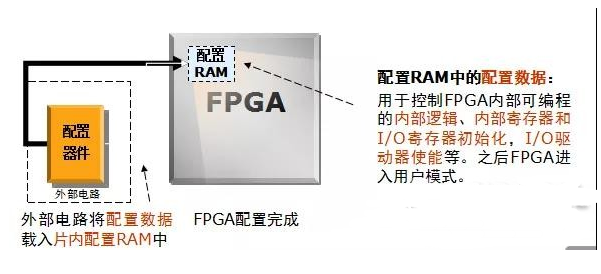

大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行。

2019-07-01 17:16:45 17573

17573 本文主要介紹Xilinx FPGA的配置模式。

2021-01-01 10:12:00 29342

29342

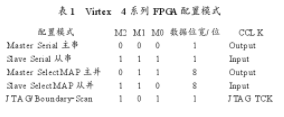

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為

2022-09-22 09:13:59 4864

4864 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行。

2022-10-24 14:52:00 1224

1224 目前,大多數(shù) FPGA 芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 3584

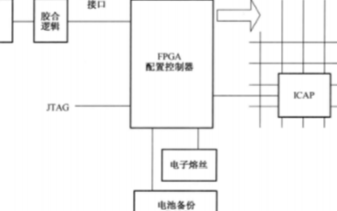

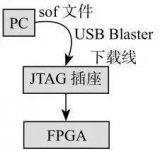

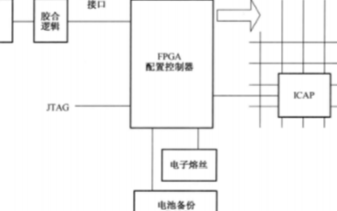

3584 我們所說(shuō)的FPGA配置電路,一方面要完成從PC上把bit文件下載到FPGA或存儲(chǔ)器的任務(wù),另一方面則要完成FPGA上電啟動(dòng)時(shí)加載配置數(shù)據(jù)的任務(wù)。

2023-06-10 10:09:52 1107

1107

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 4234

4234 Multiboot是一種在AMD Xilinx 7系列FPGA上實(shí)現(xiàn)雙鏡像(或多鏡像)切換的方案。它允許在FPGA中加載兩個(gè)不同的配置鏡像,并在需要時(shí)切換。

2024-02-25 10:54:32 2398

2398

`FPGA 上電配置時(shí)候IO口會(huì)有一個(gè)短暫的3.3V 10ms 的電平,導(dǎo)致我控制端出現(xiàn)問(wèn)題,我想問(wèn)下如何可以避免這個(gè)電平`

2020-11-23 10:31:40

FPGA配置引腳說(shuō)明使用EMCCLK引腳,全速加載程序FPGA加載時(shí)序

2021-02-03 06:47:35

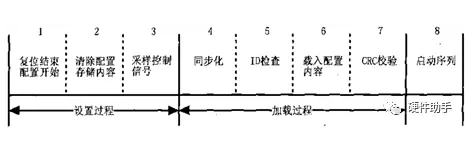

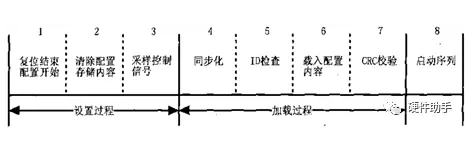

。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN屬性在Vivado中設(shè)置ExMasterCclk_en選項(xiàng) 三、FPGA加載時(shí)序 上電時(shí)序圖 上電時(shí)序圖 上電配置流程 其配置過(guò)程分解為8個(gè)步驟。 1、上電 7

2021-01-15 16:43:43

使用的是SPARTAN-3E的開(kāi)發(fā)板,在fpga配置文件時(shí),.bit文件的下載時(shí),程序可以在線正常運(yùn)行。但使用.mcs文件配置時(shí),ISE上顯示program success,但板子上的FPGA并沒(méi)有加載

2015-03-16 17:05:25

發(fā)出低脈沖 后,FPGA芯片經(jīng)過(guò)一個(gè)初始化序列清空內(nèi)部FPGA配置存儲(chǔ)器。此序列開(kāi)始時(shí),DONE和INIT_B引腳均轉(zhuǎn)為低。初始化完成后,INIT_B引腳轉(zhuǎn) 為高,并采樣芯片的配置模式及變量選擇引腳

2012-08-12 11:56:42

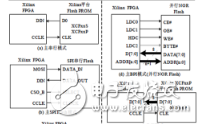

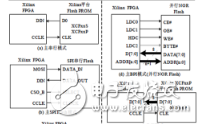

]圖1]3 基于CPLD 的FPGA 加載方案3.1]在 設(shè)備端通信產(chǎn)品中,基于CPLD 的FPGA 從并加載框如圖2 所示,配置數(shù)據(jù)存儲(chǔ)在FLASH 中,且在加載數(shù)據(jù)之前,CPU 通過(guò)局部總線和雙倍

2019-07-12 07:00:09

進(jìn)行編程。用戶可以根據(jù)不同的配置模式,采用不同的編程方式。FPGA 的使用非常靈活。目前,大部分的 FPGA 在使用時(shí)都需要外接一個(gè) EPROM 保存其程序,加電時(shí),FPGA 芯片將 EPROM 中

2018-09-06 09:11:58

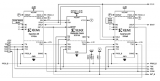

; (3)加載FPGA 電路配置數(shù)據(jù)流; (4)FPGA 電路配置完成,啟動(dòng)電路就緒序列。 主串模式電路連接圖見(jiàn)圖1。圖1 FPGA 配置主串模式連接圖 系統(tǒng)或芯片上電后,信號(hào)引腳PROG_B被拉低

2011-09-13 09:22:08

攝像頭系統(tǒng)的快速啟動(dòng)時(shí)間要求就是很好的一個(gè)例子——車(chē)輛啟動(dòng)后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設(shè)計(jì)挑戰(zhàn)。上電后,FPGA立即加載存儲(chǔ)于NOR器件中的配置比特流。傳輸完成后,FPGA轉(zhuǎn)換

2021-09-03 07:00:00

”信息。在彈出的界面中,點(diǎn)擊OK,如下圖所示:圖 4雙擊FPGA芯片圖標(biāo),在彈出的對(duì)話框中選擇需要加載的.bit文件,例如光盤(pán)“Demo\app\LED\bin”路徑下的led.bit文件,然后

2020-09-25 09:57:45

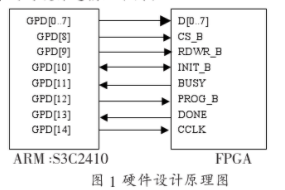

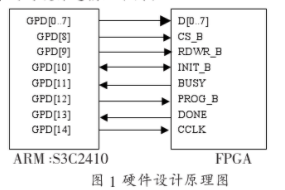

FPGA加載程序時(shí),可以采用串行從模式、并行從模式,甚至于 JTAG模式。本文選擇并行從模式,原因在于更高的配置速率。2、 FPGA程序數(shù)據(jù)的產(chǎn)生FGPA的程序加載即是要把好的程序文件按一定的時(shí)序寫(xiě)入

2019-12-10 17:42:18

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊(cè)主要介紹從動(dòng)串行(SS)加載模式以及從動(dòng)串行級(jí)聯(lián)加載模式的使用。內(nèi)容包括使用從動(dòng)串行加載模式的軟件配置,使用從動(dòng)串行加載模式和從動(dòng)串行級(jí)聯(lián)加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動(dòng)串行加載的主控器件時(shí)的軟件工作流程。

2022-10-27 08:03:06

安路 EG4X FPGA 器件支持多種程序加載模式。本手冊(cè)主要介紹從動(dòng)并行(SP)加載模式以及從動(dòng)并行級(jí)聯(lián)加載模式的使用。內(nèi)容包括使用從動(dòng)并行加載模式的軟件配置,使用從動(dòng)并行加載模式和從動(dòng)并行級(jí)聯(lián)加載模式的硬件電路連接,另外包括 MCU 作為控制 FPGA 從動(dòng)并行加載的主控器件時(shí)的軟件工作流程。

2022-10-27 07:31:16

1.同樣的板子,用過(guò)好多塊,都沒(méi)有問(wèn)題,就這塊無(wú)法加載,應(yīng)該不是PCB設(shè)計(jì)問(wèn)題。2.我設(shè)計(jì)的是主串加載模式(Master Serial)。硬件上將FPGA的M2~M0直接接到GND上。3.上電以后

2015-08-15 09:20:26

的內(nèi)部的一些特性來(lái)試圖解決這個(gè)問(wèn)題。 要解決這個(gè)問(wèn)題首先要了解FPGA上電初始化過(guò)程,這里我們是以ALTERA的ArriaGX的AS模式來(lái)進(jìn)行研究。第一步控制POR時(shí)間 FPGA的AS配置主要分為

2015-01-22 14:41:34

是用于設(shè)置FPGA初上電時(shí)的啟動(dòng)模式,我們的FPGA上電使用Standard AS模式從SPI Flash里面加載配置數(shù)據(jù)。 圖2.24 MSEL引腳配置說(shuō)明的截圖有了前面的理論做鋪墊,我們的設(shè)計(jì)也就

2016-08-10 17:03:57

我用的是Spartan-3E系列的芯片。我想有兩種下載方式,方式一是通過(guò)JTAG直接給FPGA下載程序,方便調(diào)試。方式二是將程序燒到PROM里面,在上電時(shí)FPGA自動(dòng)從PROM進(jìn)行配置。現(xiàn)在的問(wèn)題是

2013-10-18 10:06:47

,我們肯定不希望每次重新上電后都用PC去下載一次,工程實(shí)現(xiàn)也不允許我們這么做。所以,通常FPGA旁邊都有一顆配置芯片,它通常是一片F(xiàn)LASH,或者是并行或者是串行接口的。不管是串行還是并行的FLASH

2018-03-04 22:12:49

過(guò)程。FPGA上電后,內(nèi)部的控制器首先工作,確認(rèn)當(dāng)前的配置模式,如果是外部配置芯片啟動(dòng),則通過(guò)和外部配置芯片的接口(如我們的SPI接口)將配置芯片的數(shù)據(jù)加載到FPGA的RAM中,配置完成后開(kāi)始正式運(yùn)行

2018-03-05 16:30:35

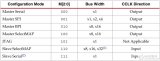

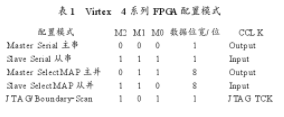

對(duì)配置模式需要作出合適的選擇。 2.2 Viretex 系列FPGA 的配置模式 Viretex 系列FPGA 的配置模式是由上電時(shí)其專用配置管腳的狀態(tài)決定的,對(duì)應(yīng)的關(guān)系 如下表所示:因在系統(tǒng)中使

2015-03-05 15:31:07

攝像頭系統(tǒng)的快速啟動(dòng)時(shí)間要求就是很好的一個(gè)例子——車(chē)輛啟動(dòng)后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設(shè)計(jì)挑戰(zhàn)。上電后,FPGA立即加載存儲(chǔ)于NOR器件中的配置比特流。傳輸完成后,FPGA轉(zhuǎn)換

2021-05-26 07:00:00

我正在研究Zedboard,我需要將FPGA配置文件(.mcs文件)存儲(chǔ)到Flash上??。Zedboard在JTAG模式下工作正常。但是,如果我選擇加載文件的flash方法,FPGA

2020-05-20 10:31:51

的內(nèi)部的一些特性來(lái)試圖解決這個(gè)問(wèn)題。 要解決這個(gè)問(wèn)題首先要了解FPGA上電初始化過(guò)程,這里我們是以ALTERA的ArriaGX的AS模式來(lái)進(jìn)行研究。第一步控制POR時(shí)間 FPGA的AS配置主要分為三個(gè)過(guò)程

2015-01-20 17:37:04

各位前輩,FPGA采用并行加載方式,現(xiàn)CPLD外掛一片F(xiàn)LASH,要求用CPLD控制加載時(shí)序,從FLASH讀取代碼,送入FPGA,應(yīng)該怎么用CPLD控制加載時(shí)序,程序應(yīng)該怎么寫(xiě),有可以參考的資料嗎,謝謝各位了!

2013-02-21 12:07:34

現(xiàn)在的FPGA還嚴(yán)格要求上電時(shí)序嗎?想請(qǐng)教一下大家

2017-09-26 15:39:07

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行

2019-07-18 08:10:11

設(shè)計(jì)者對(duì)于FPGA的配置設(shè)計(jì)是一個(gè)基本要求,當(dāng)然一般不可能要求每個(gè)FPGA硬件設(shè)計(jì)者對(duì)每一種配置模式都很熟悉,但是由于每個(gè)人的設(shè)計(jì)習(xí)慣、方法以及使用的器件不同從而在產(chǎn)品研發(fā)中設(shè)計(jì)FPGA的加載模式也

2015-01-28 10:27:03

概述EasyGo FPGA Solver是EasyGo開(kāi)發(fā)的專門(mén)部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會(huì)有不同的FPGA Solver 選擇

2022-05-19 09:21:43

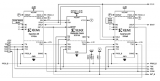

介紹如何用PowerPC860(MPC860)進(jìn)行FPGA(Xilinx 的Virtex-II 系列)的配置;給出進(jìn)行FPGA 配置所需的詳細(xì)時(shí)序圖和原理圖。本配置基本原理對(duì)其它FPGA 的配置也適用。

2009-04-16 14:11:36 18

18 什么是FPGA?FPGA是什么意思,本內(nèi)容詳加描述了FPGA的相關(guān)知識(shí)包括FPGA配置模式,PPGA特點(diǎn)及應(yīng)用

2011-12-07 13:39:00 82353

82353 摘要: 介紹基于SRAM LUT結(jié)構(gòu)的FPGA器件的上電配置方式;著重介紹采用計(jì)算機(jī)串口下載配置數(shù)據(jù)的方法和AT89C2051單片機(jī)、串行EEPROM組成的串行配置系統(tǒng)的設(shè)計(jì)方法及

2009-06-20 10:57:26 1326

1326

摘要:介紹如何用PowerPC860(MPC860)進(jìn)行FPGA(Xilinx的Virtex-II系列)的配置;給出進(jìn)行FPGA配置所需的詳細(xì)時(shí)序圖和原理圖。本配置基本原理對(duì)其它FPGA的配置也適用。

2009-06-20 11:02:38 1182

1182

介紹了一種基于SRAM技術(shù)的FPGA可編程邏輯器件的編程方法,能在系統(tǒng)復(fù)位或上電時(shí)自動(dòng)對(duì)器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問(wèn)題,針對(duì)當(dāng)前系統(tǒng)規(guī)模的日益增大,本文提出了一種用單片機(jī)對(duì)多片FPGA自動(dòng)加載配置的解決方案.

2011-03-15 16:41:22 21

21 根據(jù)FPGA芯片加載時(shí)序分析,本文提出了采用通過(guò)市面上常見(jiàn)的Flash ROM芯片替代專用PROM的方式,通過(guò)DSP的外部高速總線進(jìn)行FPGA加載;既節(jié)約了系統(tǒng)成本,也能達(dá)到FPGA上電迅速加載的目的

2011-08-16 16:26:14 2130

2130

FPGA有多種配置模式:并行主模式為一片FPGA加一片EPROM的方式;主從模式可以支持一片PROM編程多片FPGA;串行模式可以采用串行PROM編程FPGA;外設(shè)模式可以將FPGA作為微處理器的外設(shè),由微處理

2011-09-08 17:50:27 2183

2183 3 FPGA設(shè)計(jì)流程 完整的FPGA 設(shè)計(jì)流程包括邏輯電路設(shè)計(jì)輸入、功能仿真、綜合及時(shí)序分析、實(shí)現(xiàn)、加載配置、調(diào)試。FPGA 配置就是將特定的應(yīng)用程序設(shè)計(jì)按FPGA設(shè)計(jì)流程轉(zhuǎn)化為數(shù)據(jù)位流加載

2013-01-16 11:52:22 16

16 當(dāng)你的FPGA設(shè)計(jì)不能滿足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時(shí)序約束方法很好地資料,兩大主流的時(shí)序約束都講了!

2015-12-14 14:21:25 19

19 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 Xilinx FPGA編程技巧常用時(shí)序約束介紹,具體的跟隨小編一起來(lái)了解一下。

2018-07-14 07:18:00 5223

5223

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為CCLK) 由FPGA內(nèi)部產(chǎn)生,且FPGA控制整個(gè)配置過(guò)程

2017-02-11 16:36:09 2288

2288

fpga時(shí)序收斂

2017-03-01 13:13:34 23

23 基于Xilinx芯片的FPGA集成了越來(lái)越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內(nèi)部RAM 資源。在FPGA的電路設(shè)計(jì)中,上電配置電路至關(guān)重要。其中,DONE信號(hào)上拉電阻阻值的選擇很

2017-11-15 14:41:01 9168

9168

一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來(lái)越重要的作用。毋庸置疑,時(shí)序約束的最終目的是實(shí)現(xiàn)時(shí)序收斂。時(shí)序收斂作為

2017-11-17 07:54:36 2967

2967

通過(guò)SELECTMAP32接口配置和回讀XILINX公司生產(chǎn)的V5系列SRAM型FPGA,被配置的FPGA以下簡(jiǎn)稱DUT,產(chǎn)生配置時(shí)序的FPGA簡(jiǎn)稱配置FPGA。首先硬件上應(yīng)將M[2:0]接成110

2017-11-17 10:16:01 10667

10667 現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 3842

3842 滿足設(shè)計(jì)需求。FPGA的多重加載可以解決可編程資源不足的難題。FPGA多重加載是將設(shè)計(jì)的多個(gè)模式的比特文件存儲(chǔ)到Flash,用戶可以根據(jù)需要選擇加載不同模式的比特文件。FPGA的多重加載解決了可編程資源不足的問(wèn)題,提高了FPGA可編程資源的利用率。

2017-11-18 04:41:50 8767

8767

時(shí)序以及各階段I/O 管腳狀態(tài),說(shuō)明了FPGA上電配置對(duì)電路功能的嚴(yán)重影響,最后針對(duì)不同功能需求的FPGA外圍電路提出了有效的設(shè)計(jì)建議。

2017-11-22 07:18:34 8500

8500

FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失(斷電不丟數(shù)據(jù))性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)(稱為

2017-11-22 09:24:02 7490

7490 FPGA配置方式靈活多樣,根據(jù)芯片是否能夠自己主動(dòng)加載配置數(shù)據(jù)分為主模式、從模式以及JTAG模式。典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為

2017-11-26 08:12:51 8993

8993

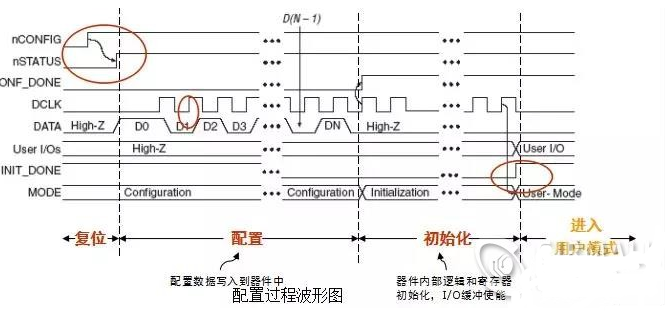

盡管FPGA的配置模式各不相同,但整個(gè)配置過(guò)程中FPGA的工作流程是一致的,分為三個(gè)部分:設(shè)置、加載、啟動(dòng)。

2018-08-01 15:32:54 5330

5330

FPGA 的配置數(shù)據(jù)通常存放在系統(tǒng)中的存儲(chǔ)器件中,上電后控制器讀取存儲(chǔ)器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實(shí)現(xiàn)方式基本都是一樣的。

2018-10-30 08:58:00 9336

9336

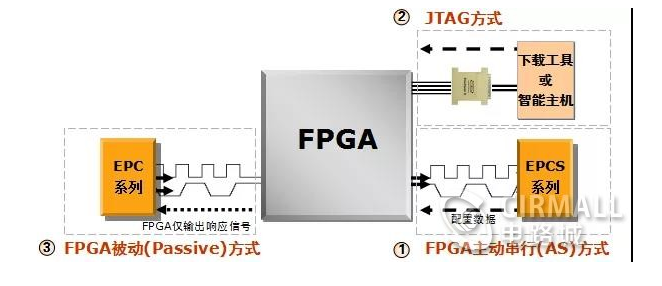

FPGA有多種配置/加載方式。粗略可以分為主動(dòng)和被動(dòng)兩種。主動(dòng)加載是指由FPGA控制配置流程,被動(dòng)加載是指FPGA僅僅被動(dòng)接收配置數(shù)據(jù)。

2018-10-05 10:12:00 19146

19146 單片機(jī)是基于FLASH結(jié)構(gòu)的,所以單片機(jī)上電直接從本地FLASH中運(yùn)行。但SRAM 架構(gòu)的FPGA是基于SRAM結(jié)構(gòu)的,掉電數(shù)據(jù)就沒(méi)了,所以需要借助外部電路來(lái)配置運(yùn)行的數(shù)據(jù),其實(shí)我們可以借助Vivado來(lái)學(xué)習(xí)FPGA的各種配置模式。

2018-11-05 15:12:57 8477

8477 Altera FPGA支持AS,PS,JTAG等幾種較常見(jiàn)的配置方法。 當(dāng)為AS配置模式時(shí),FPGA為主設(shè)備,加載外部FLASH中的數(shù)據(jù)至內(nèi)部RAM中運(yùn)行。當(dāng)為PS配置模式時(shí),FPGA為從設(shè)備,外部

2018-11-18 18:05:01 831

831 可編程的雙重優(yōu)點(diǎn),被廣泛應(yīng)用于通信領(lǐng)域中。FPGA在上電后,需要加載配置文件對(duì)內(nèi)部各功能模塊進(jìn)行初始化,而配置文件加載的效率直接影響系統(tǒng)的初始化時(shí)間。因此如何設(shè)計(jì)一種高效的FPGA加載方案,是通信系統(tǒng)設(shè)計(jì)中的一個(gè)重要環(huán)節(jié)。

2019-02-19 14:49:08 2849

2849

加載系統(tǒng)。該系統(tǒng)通過(guò)USB芯片將PC中的配置文件傳送給CPLD,CPLD再將其寫(xiě)入FLASH芯片,F(xiàn)LASH芯片可以長(zhǎng)久地存儲(chǔ)配置文件。這樣FPGA每次上電后CPLD將FLASH中的配置文件讀出來(lái)配置

2019-02-20 15:36:23 3797

3797

在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過(guò)程被稱為程序加載。多數(shù)情況下,從外部專用的 讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且 FPGA要加載的程序可以

2019-03-22 16:20:14 1470

1470 今天咱們聊聊xilinx7系列FPGA配置的相關(guān)內(nèi)容。總所周知FPGA上電后,其工作的邏輯代碼需要從外部寫(xiě)入FPGA,FPGA掉電后其邏輯代碼就丟失,因此FPGA可以被無(wú)限次的配置不同的邏輯代碼,但

2019-10-20 09:02:00 3778

3778

FPGA ,每一次上電您都必須重新初始化FPGA 內(nèi)部的CCL 。Spartan-6 FPGA 的加電配置隨應(yīng)用的不同而不同。

2020-01-10 15:28:51 28

28 FPGA是基于SRAM編程的,編程信息在系統(tǒng)掉電時(shí)會(huì)丟失,每次上電時(shí),都需要從器件外部的FLASH或EEPROM中存儲(chǔ)的編程數(shù)據(jù)重現(xiàn)寫(xiě)入內(nèi)部的SRAM中。FPGA在線加載需要有CPU的幫助,并且在加載前CPU已經(jīng)啟動(dòng)并工作。FPGA的加載模式主要有以下幾種:

2020-04-07 08:00:00 16

16 FPGA在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過(guò)程被稱為程序加載。多數(shù)情況下,FPGA從外部專用的 EPROM讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且

2020-08-13 17:16:46 2922

2922

賽靈思公司的FPGA芯片具有IEEE 1149.1/1532協(xié)議所規(guī)定的JTAG接口,只要FPGA上電,不論模式選擇管腳M[1:0] 的電平,都可用采用該配置模式。JTAG模式不需要額外的掉電非易失

2020-12-31 17:30:55 13

13 選擇。 3、PROGRAM_B(input) 低電平有效,為低時(shí),配置信息被清空,將配置過(guò)程重新進(jìn)行。上電時(shí)保持PROGRAM_B為低電平不會(huì)使FPGA配置保持復(fù)位狀態(tài)。而是使用INIT_B來(lái)延遲上電配置序列。 4、INIT_B(ino

2021-01-18 13:43:10 13937

13937

方式 1、主動(dòng)配置方式(AS) 2、被動(dòng)配置方式(PS) 3、JTAG方式 1、AS模式(active serial configuration mode):FPGA器件每次上電時(shí)作為控制器,由

2021-03-12 16:26:58 14350

14350

基于SRAM結(jié)構(gòu)的FPGA容量大,可重復(fù)操作,應(yīng)用相當(dāng)廣泛;但其結(jié)構(gòu)類(lèi)似于SRAM,掉電后數(shù)據(jù)丟失,因此每次上電時(shí)都需重新加載。

2021-03-26 13:52:58 6318

6318

所有現(xiàn)代FPGA的配置分為兩類(lèi):基于SRAM的和基于非易失性的。其中,前者使用外部存儲(chǔ)器來(lái)配置FPGA內(nèi)的SRAM后者只配置一次。 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置

2021-07-02 16:01:40 4459

4459

。 FPGA器件配置方式分三大類(lèi):主動(dòng)配置、被動(dòng)配置和JTAG配置。 主動(dòng)配置:由FPGA器件引導(dǎo)配置操作過(guò)程。 被動(dòng)配置:由計(jì)算機(jī)或控制器控制配置過(guò)程。上電后,控制器件或主控器把存儲(chǔ)在外部存儲(chǔ)器中的數(shù)據(jù)送入FPGA器件內(nèi),配置完成之后將對(duì)器件I/O和寄存器進(jìn)行初始化。初始化完成后,進(jìn)入用戶

2021-09-06 09:41:56 7483

7483 典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為CCLK) 由FPGA內(nèi)部產(chǎn)生,且FPGA控制整個(gè)配置過(guò)程。

2022-03-14 14:02:50 2381

2381 上一篇《FPGA時(shí)序約束分享01_約束四大步驟》一文中,介紹了時(shí)序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來(lái)源于配置的明德?lián)P時(shí)序約束專題課視頻。

2022-05-11 10:07:56 4989

4989

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行。

2022-08-15 09:13:31 2967

2967 電子發(fā)燒友網(wǎng)站提供《安路EG4X FPGA從動(dòng)串行加載模式.pdf》資料免費(fèi)下載

2022-09-27 10:55:18 2

2 電子發(fā)燒友網(wǎng)站提供《安路EG4X FPGA從動(dòng)并行加載模式.pdf》資料免費(fèi)下載

2022-09-27 10:44:27 1

1 盡管FPGA的配置模式各不相同,但整個(gè)配置過(guò)程中FPGA的工作流程是一致的,分為三個(gè)部分:設(shè)置、加載、啟動(dòng)。

2022-10-10 14:37:57 2187

2187 數(shù)據(jù)模式。 FPGA配置方式 根據(jù)FPGA配置過(guò)程控制者的不同,我們將配置方式主要分為三類(lèi): FPGA控制配置過(guò)程 第一種最常見(jiàn)的模式是,從片外FLASH中加載配置所需的比特流,FPGA內(nèi)部產(chǎn)生時(shí)鐘,整個(gè)過(guò)程有FPGA自主控制。FPGA 上電以后,將配置數(shù)據(jù)從FLASH中,讀入到

2022-11-21 21:45:10 1998

1998 Lattice和Actel的FPGA使用稱為反熔絲的非易失性配置技術(shù),其主要優(yōu)點(diǎn)是系統(tǒng)設(shè)計(jì)更加簡(jiǎn)單、不需要外部存儲(chǔ)器和配置控制器、功耗低、成本低和FPGA配置時(shí)間更快。最大的缺點(diǎn)在于配置是固定的。

2022-12-01 11:08:45 2130

2130 典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱為CCLK) 由FPGA內(nèi)部產(chǎn)生,且FPGA控制整個(gè)配置過(guò)程。

2023-02-15 09:57:24 1177

1177 總結(jié)Xilinx? FPGA 的上電模式可以分為以下4類(lèi)型: 主模式 從模式 JTAG模式(調(diào)試模式) 系統(tǒng)模式(多片配置模式) 1、主模式 典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性

2023-03-29 14:50:06 2111

2111 在不帶內(nèi)置ARM核的AMD FPGA產(chǎn)品系列中,FPGA的程序加載方式并沒(méi)有發(fā)生大的變化

2023-07-07 14:14:58 4513

4513

FPGA高級(jí)時(shí)序綜合教程

2023-08-07 16:07:55 9

9 應(yīng)用中得到廣泛采用。汽車(chē)場(chǎng)景中攝像頭系統(tǒng)的快速啟動(dòng)時(shí)間要求就是很好的一個(gè)例子——車(chē)輛啟動(dòng)后后視圖像在儀表板顯示屏上的顯示速度是最為突出的設(shè)計(jì)挑戰(zhàn)。 上電后,FPGA立即加載存儲(chǔ)于NOR器件中的配置比特流。傳輸完成后,FPGA轉(zhuǎn)換為活動(dòng)(已配置)狀態(tài)。FP

2023-08-15 13:55:02 1338

1338

AMD FPGA在配置了適當(dāng)?shù)膯?dòng)模式后,上電即會(huì)按該模式去加載配置文件。以7系列FPGA為例,假設(shè)設(shè)置模式引腳M[2:0]=3’b001,上電后FPGA會(huì)以Master SPI方式嘗試從FLASH加載配置文件,其與工程是否含有MicroBlaze IP無(wú)關(guān)。

2024-04-25 12:49:14 1406

1406

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論