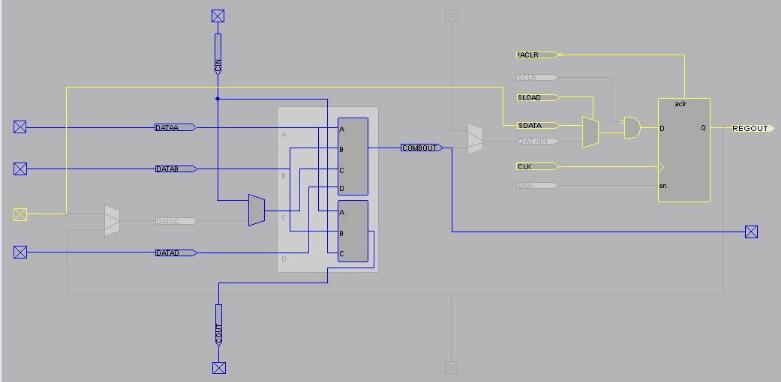

表。 這4類(lèi)路徑中,我們最為關(guān)心是②的同步時(shí)序路徑,也就是FPGA內(nèi)部的時(shí)序邏輯。 時(shí)序模型 典型的時(shí)序模型如下圖所示,一個(gè)完整的時(shí)序路徑包括源時(shí)鐘路徑、數(shù)據(jù)路徑和目的時(shí)鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 3687

3687

作者: 小魚(yú),Xilinx學(xué)術(shù)合作 一. 概述 時(shí)序邏輯示意圖,如下圖所示。數(shù)據(jù)從一個(gè)寄存器出來(lái),經(jīng)過(guò)組合邏輯到達(dá)下一個(gè)寄存器。 在學(xué)習(xí)數(shù)字電路的過(guò)程中,我們都知道時(shí)序邏輯,但是大家對(duì)時(shí)序邏輯真的

2020-12-25 14:39:28 6509

6509

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi):一類(lèi)叫做組合邏輯電路,簡(jiǎn)稱(chēng)組合電路或組合邏輯;另一類(lèi)叫做時(shí)序邏輯電路,簡(jiǎn)稱(chēng)時(shí)序電路或時(shí)序邏輯。

2022-12-01 09:04:04 1445

1445 數(shù)字門(mén)級(jí)電路可分為兩大類(lèi):組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

2023-01-13 13:57:47 3032

3032

數(shù)字邏輯電路分為組合邏輯電路和時(shí)序邏輯電路。時(shí)序邏輯電路是由組合邏輯電路和時(shí)序邏輯器件構(gòu)成(觸發(fā)器),即數(shù)字邏輯電路是由組合邏輯和時(shí)序邏輯器件構(gòu)成。

2023-03-21 09:49:49 1443

1443 芯片設(shè)計(jì)是現(xiàn)代電子設(shè)備的重要組成部分,其中組合邏輯和時(shí)序邏輯是芯片設(shè)計(jì)中非常重要的概念。組合邏輯和時(shí)序邏輯的設(shè)計(jì)對(duì)于構(gòu)建復(fù)雜的電路系統(tǒng)至關(guān)重要。

2023-08-30 09:32:15 1843

1843 大神求救!我現(xiàn)在想要用FPGA實(shí)現(xiàn)一個(gè)數(shù)與一個(gè)數(shù)組(寬度為64)數(shù)相乘,累加,再取平均,用的是時(shí)序邏輯加上非阻塞賦值的方法實(shí)現(xiàn),即從數(shù)組0開(kāi)始相乘,一直到數(shù)組63,當(dāng)乘完63時(shí),將累加的數(shù)取平均輸出

2017-09-13 11:02:51

FPGA中組合邏輯門(mén)占用資源過(guò)多怎么降低呢?有什么方法嗎?

2023-04-23 14:31:17

的邏輯粘合。所謂的邏輯粘合,無(wú)非是一些與、或、非等邏輯門(mén)電路簡(jiǎn)單拼湊的組合邏輯,沒(méi)有時(shí)序邏輯,因此不需要引入時(shí)鐘。而今天的FPGA器件的各種資源都非常豐富,已經(jīng)很少有人只是用其實(shí)現(xiàn)簡(jiǎn)單的組合邏輯功能,而是

2015-06-29 09:31:03

很小的干擾濾除。但是,我們現(xiàn)在是在FPGA器件內(nèi)部,還真沒(méi)有這樣的條件和可能性這么處理,那么只能放棄這種方案。另一種辦法其實(shí)也就是引入時(shí)序邏輯,用寄存器多輸出信號(hào)打一拍,這其實(shí)也是時(shí)序邏輯明顯優(yōu)于組合

2015-07-08 10:38:02

基本的時(shí)序分析理論1本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 何謂靜態(tài)時(shí)序分析(STA,Static

2015-07-09 21:54:41

基本的時(shí)序分析理論2本文節(jié)選自特權(quán)同學(xué)的圖書(shū)《FPGA設(shè)計(jì)實(shí)戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 下面我們?cè)賮?lái)看一個(gè)例子,如圖8.2所示

2015-07-14 11:06:10

延時(shí),這個(gè)路徑中不經(jīng)過(guò)任何寄存器,它的整個(gè)路徑延時(shí)基本上只是一些組合邏輯延時(shí)和走線(xiàn)延時(shí)。這類(lèi)路徑在純組合邏輯電路中比較常見(jiàn),也必須在時(shí)序分析中覆蓋到。這類(lèi)路徑也沒(méi)有所謂的建立時(shí)間和保持時(shí)間,設(shè)計(jì)者關(guān)心

2015-07-20 14:52:19

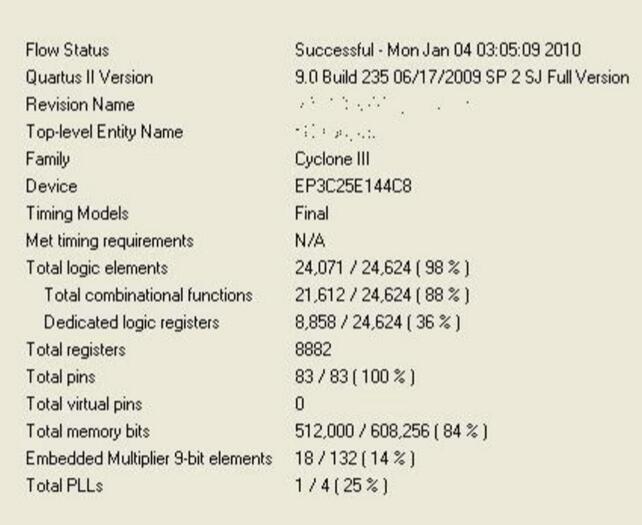

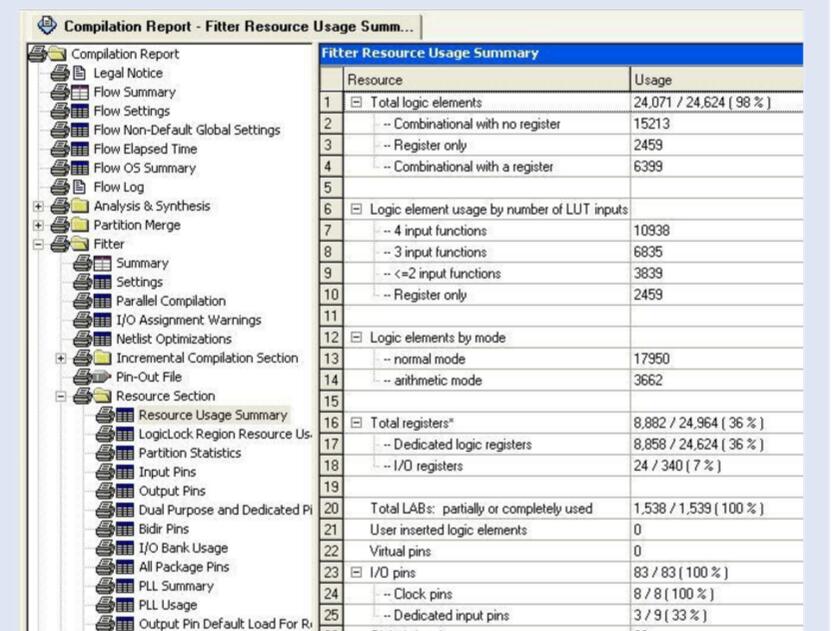

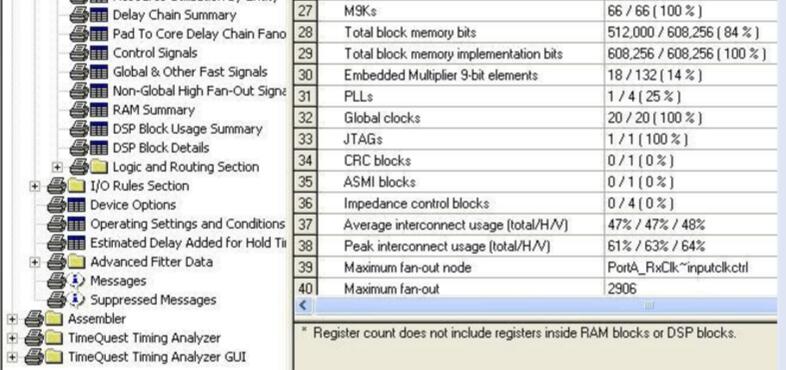

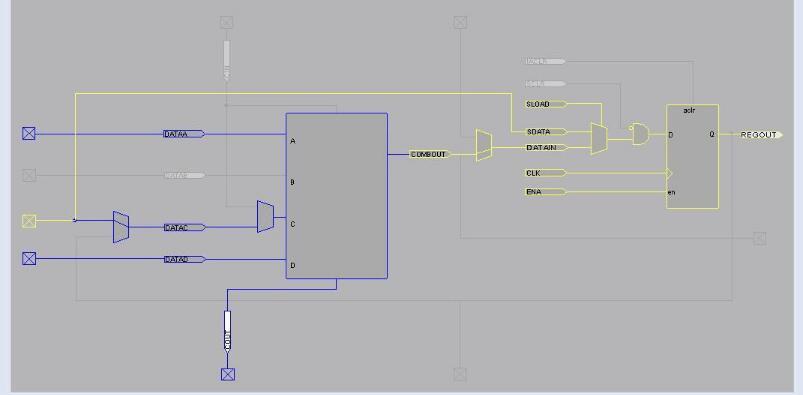

如何得到LUT與REG的使用比例?如何分析FPGA芯片上的組合邏輯(LUT)和時(shí)序邏輯(REG)的利用率?

2021-09-17 07:01:26

實(shí)戰(zhàn)應(yīng)用,這種快樂(lè)試試你就會(huì)懂的。話(huà)不多說(shuō),上貨。 數(shù)字電路中的組合邏輯 根據(jù)邏輯功能的不同特點(diǎn),可以將數(shù)字電路分為兩大類(lèi),一類(lèi)稱(chēng)為組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)稱(chēng)為時(shí)序邏輯電路(簡(jiǎn)稱(chēng)

2023-02-21 15:35:38

fpga時(shí)序邏輯電路的分析和設(shè)計(jì) 時(shí)序邏輯電路的結(jié)構(gòu)及特點(diǎn)時(shí)序邏輯電路——任何一個(gè)時(shí)刻的輸出狀態(tài)不僅取決于當(dāng)時(shí)的輸入信號(hào),還與電路的原狀態(tài)有關(guān)。[hide][/hide]

2012-06-20 11:18:44

的話(huà),不能保證所有的情況都有賦值,就會(huì)在內(nèi)部形成一個(gè)鎖存器,不再是一個(gè)純粹的組合邏輯了,電路性能就會(huì)下降.例如:case({a,b})2'b11 e=b;2'b10 e=a;endcase//不加

2018-03-24 11:04:41

電路的邏輯功能。時(shí)序邏輯電路對(duì)于時(shí)序邏輯電路,分析電路的最終目的是什么?實(shí)際情況往往是:已知時(shí)序電路圖,要求找出該電路的功能。時(shí)序邏輯電路一般分析方法1、驅(qū)動(dòng)方程:按組合邏輯電路的分析方法,寫(xiě)出觸發(fā)器輸入

2021-11-18 06:30:00

組合邏輯電路實(shí)驗(yàn)實(shí)驗(yàn)三 組合邏輯電路一、 實(shí)驗(yàn)?zāi)康?、 掌握組合邏輯電路的功能測(cè)試2、 驗(yàn)證半加器和全加器的邏輯功能3、 學(xué)會(huì)

2009-03-20 18:11:09

如何檢查 Android 應(yīng)用的內(nèi)存使用情況

2020-03-30 13:36:17

CUBEIDE運(yùn)行完可以看RAM的使用情況,運(yùn)行中可以實(shí)時(shí)查看RAM的使用情況嗎?以及負(fù)載情況?

圖片是運(yùn)行完可以看RAM使用情況,是否可以運(yùn)行中實(shí)時(shí)查看?是不是cubemonitor可以實(shí)時(shí)查看?

2024-03-12 07:56:43

第10章 STM32H7的FLASH,RAM和棧使用情況(map和htm文件)本章為大家介紹編譯器生成的map和htm文件進(jìn)行解析,通過(guò)這兩個(gè)文件可以讓大家對(duì)工程代碼的認(rèn)識(shí)程度提升一個(gè)檔次。10.1 初學(xué)者重要提示10...

2021-08-03 06:18:13

查看系統(tǒng)內(nèi)存:

free -h

查看ION內(nèi)存

NPU內(nèi)存使用情況:

cat /sys/kernel/debug/ion/bm_npu_heap_dump/summary | head -2VPU

2023-09-19 07:23:11

想查看系統(tǒng)動(dòng)態(tài)如CPU使用情況內(nèi)存使用情況和管理進(jìn)程可以使用下面這個(gè)工具,打開(kāi)systems-administartor中的synaptic package manager,按CTRL+R然后按

2015-12-26 11:38:08

邏輯反映的電路也有不同,時(shí)序邏輯相當(dāng)于在組合邏輯的基礎(chǔ)上多了一個(gè)D觸發(fā)器。 波形圖層面,組合邏輯的波形是即刻反映變化的,與時(shí)鐘無(wú)關(guān);但是時(shí)序邏輯的波形不會(huì)立刻反映出來(lái),只有在時(shí)鐘的上升沿發(fā)生變化。用一個(gè)

2020-03-01 19:50:27

為什么FPGA可以用來(lái)實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

2023-04-23 11:53:26

本文將為您詳細(xì)說(shuō)明幾種OTDR現(xiàn)場(chǎng)使用情況。

2021-05-11 07:18:13

1、FPGA開(kāi)發(fā)板上組合邏輯電路的設(shè)計(jì)實(shí)現(xiàn)在之前的文章中已經(jīng)介紹過(guò)了安路EG4S20 FPGA開(kāi)發(fā)板以及TD工具的使用,從這篇文章開(kāi)始,我們將介紹和分享一系列的基礎(chǔ)實(shí)例,期望能幫助大家逐步

2022-07-21 15:38:45

```勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載25:組合邏輯與時(shí)序邏輯特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 數(shù)字電路按照邏輯

2017-11-17 18:47:44

呢? 舉例說(shuō)明:目前要設(shè)計(jì)模塊A,不涉及反饋,不涉及時(shí)序對(duì)齊等,可以采取組合邏輯設(shè)計(jì)也可以采用時(shí)序邏輯設(shè)計(jì)。 模塊A的輸出連接到模塊B,經(jīng)過(guò)一些變換(組合邏輯N)連接到某個(gè)寄存器K上。如果模塊A采用

2023-03-06 16:31:59

些涉及時(shí)序邏輯電路的實(shí)例,希望能夠幫助大家理解在FPGA中實(shí)現(xiàn)時(shí)序邏輯電路。與組合邏輯電路相比,時(shí)序邏輯電路需要時(shí)鐘的參與,電路中會(huì)有存儲(chǔ)器件的參與,時(shí)序邏輯電路的輸出不僅取決于這一時(shí)刻的輸入,也受此

2022-07-22 15:25:03

Verilog程序模塊的結(jié)構(gòu)是由哪些部分組成的?如何去實(shí)現(xiàn)時(shí)序邏輯電路和組合邏輯電路的設(shè)計(jì)呢?

2021-11-03 06:35:57

嗨, 我正在使用STM32L053 Nucleo,我已經(jīng)為它運(yùn)行了一些代碼,我希望做一個(gè)RAM估計(jì)來(lái)查看當(dāng)前固件的RAM使用情況。如何查看RAM使用情況? 問(wèn)候#記憶

2019-08-05 10:08:20

在板上運(yùn)行 Qt6 應(yīng)用程序,想觀察該 Qt6 應(yīng)用程序?qū)?GPU 的使用情況。

如何檢查應(yīng)用程序的 GPU 使用情況或該應(yīng)用程序是否真的在使用 GPU?我們可以查看和確認(rèn)該使用情況的任何日志文件

2023-05-22 07:04:17

STVD - 宇宙 - 我如何知道閃存代碼和內(nèi)存使用情況?以上來(lái)自于谷歌翻譯以下為原文 STVD - Cosmic - how do I know the flash code and ram usage?

2019-05-08 15:22:24

(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門(mén)電路數(shù)有限的缺點(diǎn)。 本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時(shí)序邏輯來(lái)詳細(xì)的分析

2019-06-17 09:03:28

電池使用情況信息根據(jù)電池使用情況統(tǒng)計(jì)信息和電源配置文件中的值計(jì)算得出。電池使用情況統(tǒng)計(jì)信息框架可通過(guò)跟蹤設(shè)備組件在不同狀態(tài)下維持的時(shí)間來(lái)自動(dòng)確定電池使用情況統(tǒng)計(jì)信息。當(dāng)組件(WLAN 芯片組、手機(jī)

2021-12-31 07:01:56

組合邏輯電路的基本模塊是什么?時(shí)序邏輯電路怎樣進(jìn)行工作的?

2021-09-18 09:19:42

組合邏輯電路(簡(jiǎn)稱(chēng)組合電路)任意時(shí)刻的輸出信號(hào)僅取決于該時(shí)刻的輸入信號(hào),與信號(hào)作用前電路原來(lái)的狀態(tài)無(wú)關(guān)時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)任意時(shí)刻的輸出信號(hào)不僅取決

2009-07-15 18:45:58 0

0 組合邏輯電路電子教案:數(shù)字邏輯電路可分為兩大類(lèi): 一類(lèi)叫組合邏輯電路;另一類(lèi)叫時(shí)序邏輯電路。本章首先介紹組合邏輯電路的共同特點(diǎn)和描述方法,然后重點(diǎn)介紹組合邏輯電

2009-09-01 08:58:29 0

0 同步時(shí)序邏輯電路:本章系統(tǒng)的講授同步時(shí)序邏輯電路的工作原理、分析方法和設(shè)計(jì)方法。從同步時(shí)序邏輯電路模型與描述方法開(kāi)始,介紹同步時(shí)序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 異步時(shí)序邏輯電路:本章主要從同步時(shí)序邏輯電路與異步時(shí)序邏輯電路狀態(tài)改變方式不同的特殊性出發(fā), 系統(tǒng)的介紹異步時(shí)序邏輯電路的電路結(jié)構(gòu)、工作原理、分析方法和設(shè)計(jì)方法。

2009-09-01 09:12:34 0

0 數(shù)字邏輯電路按邏輯功能和電路組成的特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路兩大類(lèi)。

2010-08-10 11:51:58 39

39 數(shù)字邏輯電路可分為組合邏輯電路和時(shí)序邏輯電路兩大類(lèi)。組合邏輯電路在任一時(shí)刻的穩(wěn)定輸出只取決于當(dāng)前的輸入,而與過(guò)去的輸入無(wú)關(guān)。在結(jié)構(gòu)上,組合邏輯電路僅由若干邏

2010-08-12 15:54:42 0

0 數(shù)字電路分為組合邏輯電路(簡(jiǎn)稱(chēng)組合電路)和時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)兩類(lèi)。在第三章中討論的電路為組合電路。組合電路的結(jié)構(gòu)模型如圖4.1所示,它的輸出函數(shù)表達(dá)式為

2010-08-13 15:23:02 24

24 數(shù)字集成電路,根據(jù)原理可分為兩大類(lèi),既組合邏輯電路和時(shí)序邏輯電路。

組合邏輯電路的組成是邏輯門(mén)電路。電路的輸出狀態(tài)僅由同一時(shí)刻的輸入狀態(tài)決定,與電路的原

2010-08-18 15:05:23 55

55 組合邏輯電路的分析與設(shè)計(jì)-邏輯代數(shù)

在任何時(shí)刻,輸出狀態(tài)只決定于同一時(shí)刻各輸入狀態(tài)的組合,而與先前狀態(tài)無(wú)關(guān)的邏輯電路稱(chēng)為組合邏輯電路。

2009-04-07 10:07:57 3922

3922

時(shí)序邏輯電路的特點(diǎn)

在第三章所討論的組合邏輯電路中,任一時(shí)刻的輸出信號(hào)僅僅取決于該時(shí)刻的輸入信號(hào),而與電路原來(lái)

2009-09-30 18:19:22 10881

10881

時(shí)序邏輯電路實(shí)例解析

一、觸發(fā)器 1、電位觸發(fā)方式觸發(fā)器

2010-04-15 13:46:25 6161

6161 邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。

2017-05-22 15:15:59 77019

77019

90%以上甚至更多。為此系統(tǒng)管理員在必要的時(shí)候,仍然需要監(jiān)視系統(tǒng)資源的使用情況。筆者今天就給大家介紹一下,在Linux操作系統(tǒng)下如何監(jiān)視這個(gè)系統(tǒng)資源,做到心中有數(shù)。 一、如何監(jiān)視系統(tǒng)資源? 在Windows操作系統(tǒng)中,可以通過(guò)任務(wù)管理器來(lái)查詢(xún)各個(gè)進(jìn)程所占

2017-11-03 12:39:43 0

0 由于同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器SDRAM內(nèi)部結(jié)構(gòu)原因?qū)е缕淇刂?b class="flag-6" style="color: red">邏輯比較復(fù)雜。現(xiàn)場(chǎng)可編程邏輯門(mén)陣列FPGA作為一種半定制電路具有速度快、內(nèi)部資源豐富、可重構(gòu)等優(yōu)點(diǎn)。本文設(shè)計(jì)了一種基于FPGA的SDRAM

2017-11-18 12:42:03 2520

2520

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2017-11-20 12:26:21 9235

9235 主流GPS芯片使用情況

2017-11-27 14:34:08 13

13 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。

2018-01-30 16:24:25 40173

40173

邏輯電路按其邏輯功能和結(jié)構(gòu)特點(diǎn)可分為組合邏輯電路和時(shí)序邏輯電路。單一的與門(mén)、或門(mén)、與非門(mén)、或非門(mén)、非門(mén)等邏輯門(mén)不足以完成復(fù)雜的數(shù)字系統(tǒng)設(shè)計(jì)要求。組合邏輯電路是采用兩個(gè)或兩個(gè)以上基本邏輯門(mén)來(lái)實(shí)現(xiàn)更實(shí)用、復(fù)雜的邏輯功能。

2018-01-30 17:05:44 67767

67767

組合邏輯電路和時(shí)序邏輯電路都是數(shù)字電路,組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。而時(shí)序邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出不僅取決于當(dāng)時(shí)的輸入信號(hào),而且還取決于電路原來(lái)的狀態(tài),或者說(shuō),還與以前的輸入有關(guān)。

2018-01-30 17:26:04 94951

94951

模塊的模板包括了輸入輸出信號(hào)列表、信號(hào)定義,組合邏輯和時(shí)序邏輯等,這是一個(gè)模塊常用的組件。學(xué)員只需要理解各個(gè)部分的意義,按要求來(lái)填空就可以,完全沒(méi)有必要去記住。我看很多學(xué)員剛開(kāi)始學(xué)習(xí)時(shí),花費(fèi)大量的時(shí)間去記住、背熟模塊,這是沒(méi)有意義的。

2018-04-20 15:40:00 1957

1957

數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-02-26 15:22:20 32848

32848 時(shí)序邏輯電路是由組合邏輯電路與記憶電路(又稱(chēng)存儲(chǔ)電路) 組合而成的。 常見(jiàn)時(shí)序邏輯電路有觸發(fā)器、 寄存器和計(jì)數(shù)器等。

2019-02-26 15:25:01 52417

52417 組合邏輯電路是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入,與電路原來(lái)的狀態(tài)無(wú)關(guān)。而時(shí)序邏輯電路不僅僅取決于當(dāng)前的輸入信號(hào),而且還取決于電路原來(lái)的狀態(tài),或者說(shuō),還與以前的輸入有關(guān)。

2019-02-26 15:32:30 67227

67227 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2019-05-16 18:32:37 8978

8978

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線(xiàn),全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-05 07:08:00 3476

3476

本課程以目前流行的Xilinx 7系列FPGA的開(kāi)發(fā)為主線(xiàn),全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語(yǔ)言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開(kāi)發(fā)開(kāi)始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-03 07:04:00 3009

3009

本文檔的主要內(nèi)容詳細(xì)介紹的是組合邏輯電路和時(shí)序邏輯電路的學(xué)習(xí)課件免費(fèi)下載包括了:任務(wù)一 組合邏輯電路,任務(wù)二 編碼器,任務(wù)三 譯碼器,任務(wù)四 集成觸發(fā)器,任務(wù)五 寄存器,任務(wù)六 計(jì)數(shù)器。

2020-10-27 15:58:24 31

31 ,包括進(jìn)程、線(xiàn)程、程序堆棧、內(nèi)存、Swap、CPU調(diào)度、內(nèi)存調(diào)度、網(wǎng)絡(luò)連接和IO讀寫(xiě)等。 本文介紹了Linux查看資源使用情況和性能調(diào)優(yōu)常用的命令,包括top、htop、ps、free、vmstat

2020-11-12 17:54:43 4943

4943 打開(kāi)電腦的任務(wù)管理器,看著跳動(dòng)的 CPU 使用率,發(fā)現(xiàn)很舒服。每一個(gè)線(xiàn)程占用了多少 CPU 清清楚楚,也就能針對(duì)性的確認(rèn)為啥你的電腦跑的慢了。今天這篇筆記不講每個(gè)任務(wù)(或線(xiàn)程)CPU 的使用情況,而是單片機(jī)整體的 CPU 使用情況,先易后難嘛。

2020-11-25 15:58:00 12

12 組合邏輯電路是指在任何時(shí)刻,輸出狀態(tài)只決定于同一時(shí)刻各組合邏輯電路輸入狀態(tài)的組合,而與電路以前狀態(tài)無(wú)關(guān)而與其他時(shí)間的狀態(tài)無(wú)關(guān)。如:加法器、編碼器、譯碼器、選擇器等

2020-12-09 14:49:02 12

12 STM32/KEIL/MDK 查看 FLASH 和 RAM 使用情況

2021-12-02 09:06:08 13

13 這里使用Windows自帶的東西查看電源使用情況。1.按Win鍵+R,輸入cmd,回車(chē)。2.輸入Powercfg /batteryreport回車(chē)。3.根據(jù)提示找到電池報(bào)告文件,雙擊打開(kāi)即可。????...

2022-01-05 14:18:43 0

0 時(shí)序問(wèn)題跟代碼風(fēng)格本身、資源使用情況等都有關(guān)系,代碼本身占很大部分,比較復(fù)雜的邏輯由于代碼沒(méi)寫(xiě)好,導(dǎo)致最終出現(xiàn)時(shí)序問(wèn)題的情況比比皆是,這就需要多積累多練習(xí),后續(xù)我還會(huì)持續(xù)分享時(shí)序方面自己的心得。

2022-09-06 09:27:00 2237

2237 從今天開(kāi)始新的一章-Circuits,包括基本邏輯電路、時(shí)序電路、組合電路等。

2022-10-10 15:39:01 2278

2278 在進(jìn)行MCU開(kāi)發(fā)時(shí),有時(shí)需要用到一些簡(jiǎn)單的數(shù)字邏輯電路,LPC804與LPC55XX系列集成了PLU(Programmable Logic Unit),即可編程邏輯單元,可創(chuàng)建小型組合與時(shí)序邏輯電路,降低成本。

2022-12-01 09:17:42 2388

2388 數(shù)字門(mén)級(jí)電路可分為兩大類(lèi):組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

2022-12-21 09:18:32 1882

1882 數(shù)字門(mén)級(jí)電路可分為兩大類(lèi):組合邏輯和時(shí)序邏輯。鎖存器是組合邏輯和時(shí)序邏輯的一個(gè)交叉點(diǎn),在后面會(huì)作為單獨(dú)的主題處理。

2023-02-12 10:28:36 2026

2026 數(shù)字電路根據(jù)邏輯功能的不同特點(diǎn),可以分成兩大類(lèi),一類(lèi)叫組合邏輯電路(簡(jiǎn)稱(chēng)組合電路),另一類(lèi)叫做時(shí)序邏輯電路(簡(jiǎn)稱(chēng)時(shí)序電路)。組合邏輯電路在邏輯功能上的特點(diǎn)是任意時(shí)刻的輸出僅僅取決于該時(shí)刻的輸入

2023-03-14 17:06:50 8730

8730

時(shí)序邏輯的代碼一般有兩種: 同步復(fù)位的時(shí)序邏輯和異步復(fù)位的時(shí)序邏輯。在同步復(fù)位的時(shí)序邏輯中復(fù)位不是立即有效,而在時(shí)鐘上升沿時(shí)復(fù)位才有效。 其代碼結(jié)構(gòu)如下:

2023-03-21 10:47:07 1239

1239 時(shí)序邏輯電路分析和設(shè)計(jì)的基礎(chǔ)是組合邏輯電路與觸發(fā)器,所以想要分析和設(shè)計(jì),前提就是必須熟練掌握各種常見(jiàn)的組合邏輯電路與觸發(fā)器功能,尤其是各種觸發(fā)器的特征方程與觸發(fā)模式,因此前幾文的基礎(chǔ)顯得尤為重要。 本文主要介紹時(shí)序邏輯電路的分析方法。

2023-05-22 18:24:31 5502

5502

電子發(fā)燒友網(wǎng)站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費(fèi)下載

2023-06-15 09:14:49 0

0 電子發(fā)燒友網(wǎng)站提供《LPC86x上的開(kāi)關(guān)矩陣使用情況.pdf》資料免費(fèi)下載

2023-08-17 10:48:40 0

0 電子發(fā)燒友網(wǎng)站提供《LPC86x ACMP使用情況.pdf》資料免費(fèi)下載

2023-08-17 10:34:04 0

0 電子發(fā)燒友網(wǎng)站提供《LPC86x ADC使用情況.pdf》資料免費(fèi)下載

2023-08-16 10:42:40 0

0 Web服務(wù)器上,您可以在“內(nèi)存”選項(xiàng)卡的“診斷”網(wǎng)頁(yè)上找到有關(guān)各個(gè)內(nèi)存區(qū)域當(dāng)前使用情況的信息。

2023-12-18 10:18:05 1592

1592

組合邏輯電路和時(shí)序邏輯電路是數(shù)字電路中兩種重要的邏輯電路類(lèi)型,它們主要區(qū)別在于其輸出信號(hào)的依賴(lài)關(guān)系和對(duì)時(shí)間的敏感性。

2024-02-04 16:00:27 7168

7168 時(shí)序邏輯電路是一種能夠存儲(chǔ)信息并根據(jù)時(shí)鐘信號(hào)按照特定順序執(zhí)行操作的電路。它是計(jì)算機(jī)硬件中非常重要的一部分,用于實(shí)現(xiàn)存儲(chǔ)器、時(shí)序控制器等功能。與之相對(duì)的是組合邏輯電路,它根據(jù)輸入信號(hào)的組合情況,立即

2024-02-06 11:18:34 13635

13635 組成:組合邏輯電路和時(shí)鐘電路。組合邏輯電路是一種基本的邏輯電路,其輸出僅僅取決于當(dāng)前的輸入信號(hào),與時(shí)間無(wú)關(guān)。組合邏輯電路由門(mén)電路(如與門(mén)、或門(mén)、非門(mén)等)組成,通過(guò)門(mén)的組合和連接構(gòu)成了復(fù)雜的邏輯功能。時(shí)序邏輯電路將

2024-02-06 14:30:23 4294

4294 什么是組合邏輯電路和時(shí)序邏輯電路?時(shí)序邏輯電路和組合邏輯電路的區(qū)別是什么? 組合邏輯電路和時(shí)序邏輯電路是數(shù)字電路中兩種基本類(lèi)型的電路設(shè)計(jì)。 組合邏輯電路是由邏輯門(mén)組成的,邏輯門(mén)的輸出僅由它的當(dāng)前輸入

2024-03-26 16:12:14 6631

6631 時(shí)序邏輯電路是一種數(shù)字電路,它根據(jù)輸入信號(hào)和電路內(nèi)部狀態(tài)的變化產(chǎn)生輸出信號(hào)。時(shí)序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。 一、時(shí)序邏輯電路概述 時(shí)序邏輯電路是一種動(dòng)態(tài)邏輯電路,其輸出不僅取決于

2024-07-30 15:02:11 3422

3422 時(shí)序邏輯電路本身并不直接“產(chǎn)生”鎖存器,但鎖存器是時(shí)序邏輯電路中的重要組成部分。時(shí)序邏輯電路(Sequential Logic Circuits)與組合邏輯電路(Combinational

2024-08-28 11:03:47 1319

1319 加法器不是時(shí)序邏輯電路 ,而是組合邏輯電路的一種。時(shí)序邏輯電路和組合邏輯電路的主要區(qū)別在于它們?nèi)绾翁幚磔敵鲂盘?hào)。 組合邏輯電路的輸出僅依賴(lài)于當(dāng)前的輸入信號(hào),而不依賴(lài)于電路之前的狀態(tài)或輸入歷史。這

2024-08-28 11:05:51 2051

2051 時(shí)序邏輯電路是數(shù)字電路中的一種重要類(lèi)型,其特點(diǎn)是電路的輸出不僅取決于當(dāng)前的輸入,還取決于電路的狀態(tài)。時(shí)序邏輯電路廣泛應(yīng)用于計(jì)算機(jī)、通信、控制等領(lǐng)域。 1. 引言 在數(shù)字電路設(shè)計(jì)中,時(shí)序邏輯電路是實(shí)現(xiàn)

2024-08-28 11:41:38 1914

1914 時(shí)序邏輯電路確實(shí)具有記憶功能 。這一特性是時(shí)序邏輯電路與組合邏輯電路的本質(zhì)區(qū)別之一。

2024-08-29 10:31:28 2362

2362

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論