大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 17573

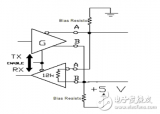

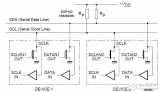

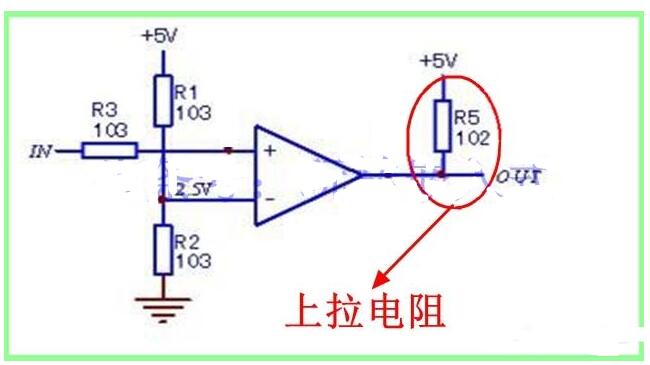

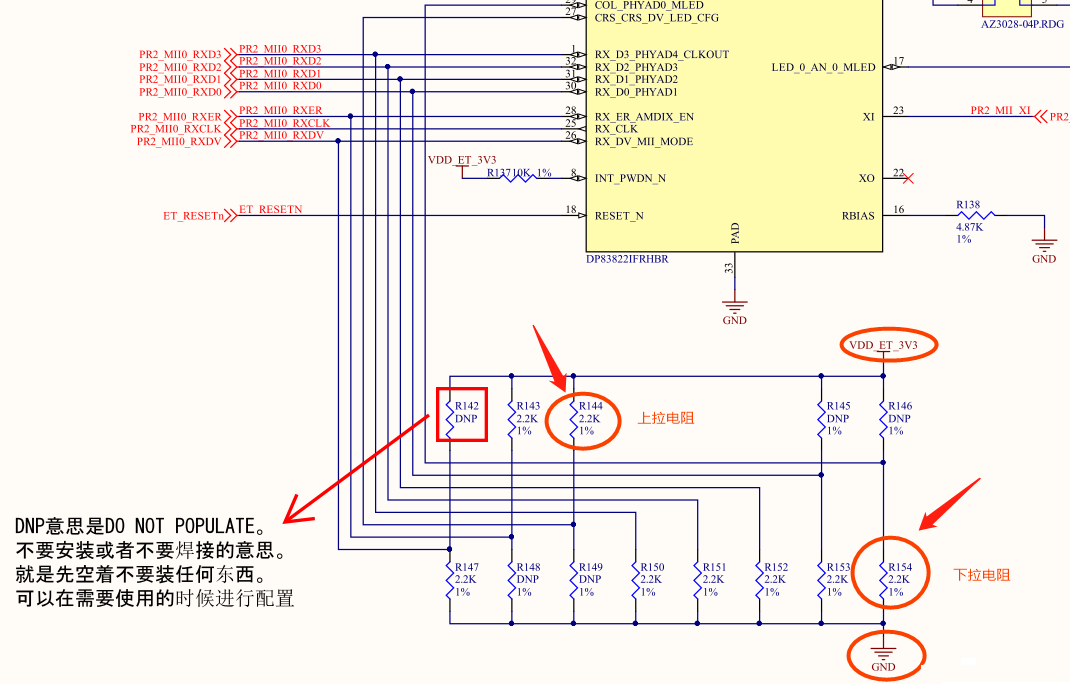

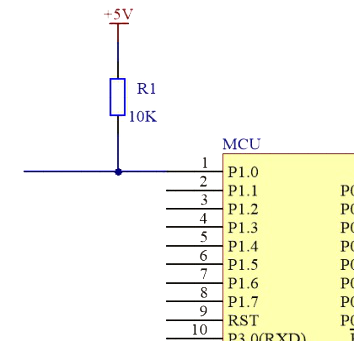

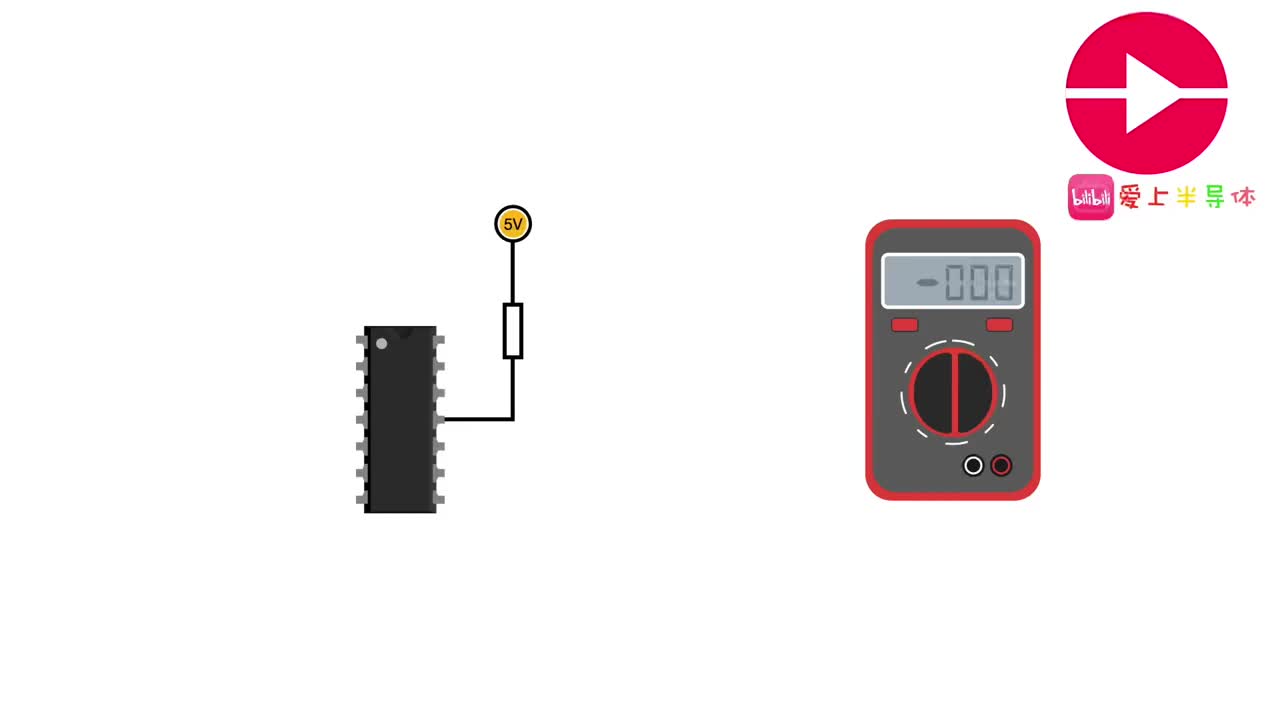

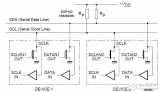

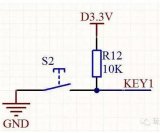

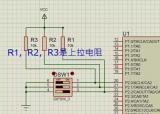

17573 我們知道,在I2C的電路中,在SCL、SDA線與電源之間通常會接一個電阻,這個電阻稱之為上拉電阻。 但什么是上拉電阻? 上拉電阻主要用于為信號線或GPIO引腳提供默認狀態(tài)。

2022-09-08 14:43:24 8554

8554 目前,大多數(shù) FPGA 芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 3584

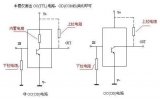

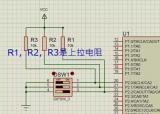

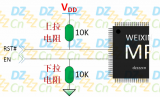

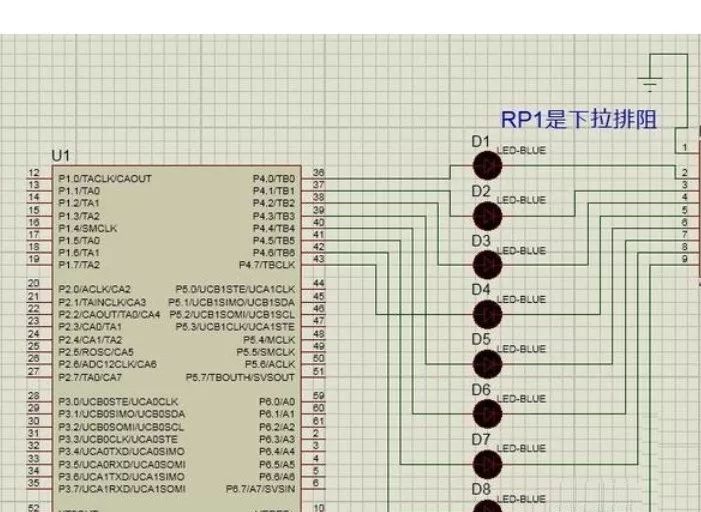

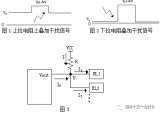

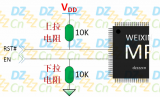

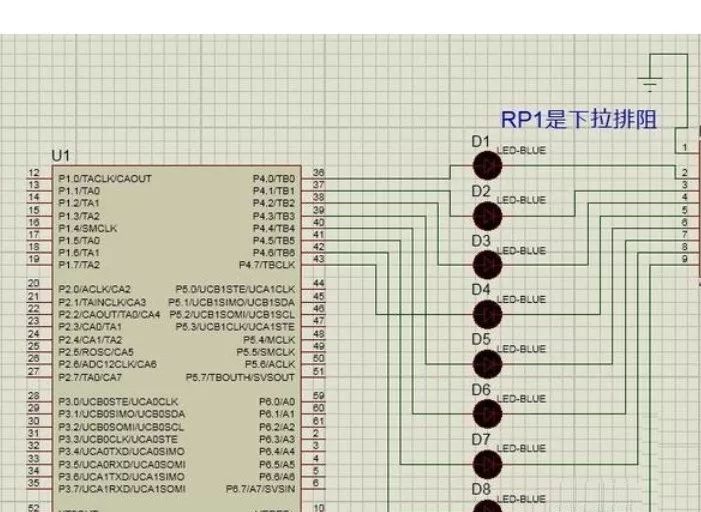

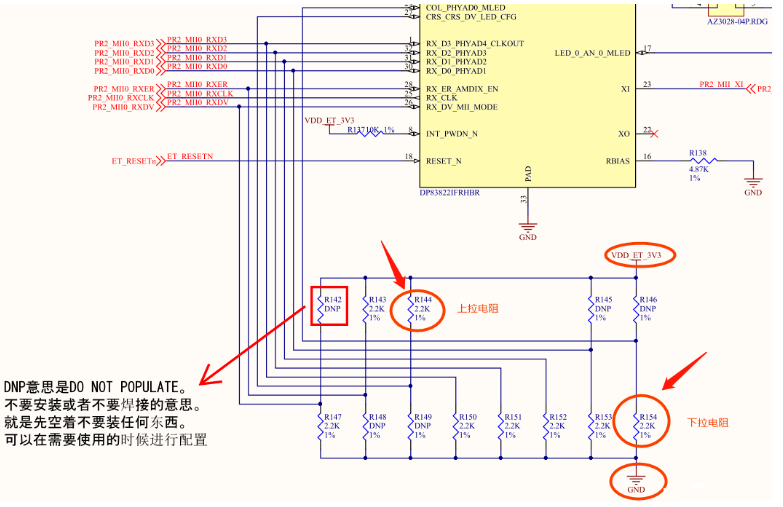

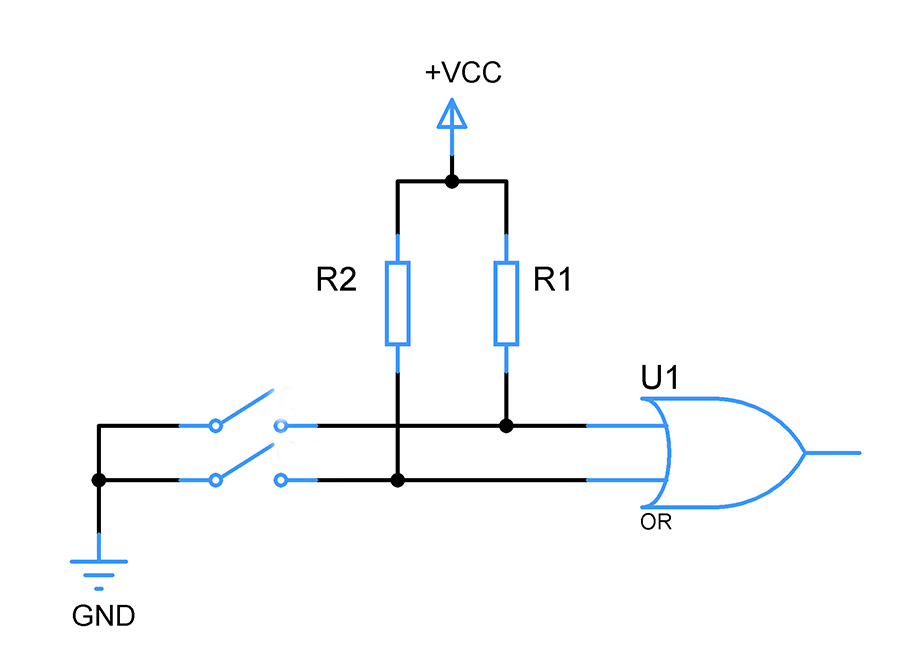

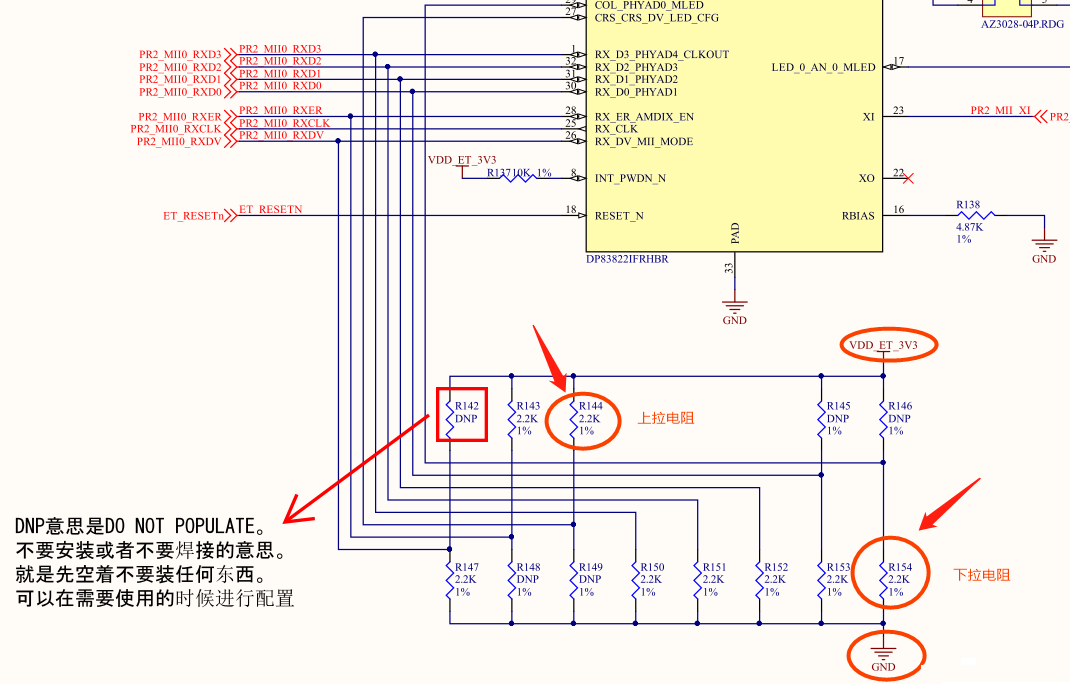

3584 一、上下拉電阻介紹 ??上拉電阻:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平。作用:上拉是對器件注入電流;灌電流;當一個接有上拉電阻的IO端口設(shè)置為輸入狀態(tài)時,它的常態(tài)為高電平

2023-04-21 09:49:34 18733

18733 什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。那么,上拉電阻和下拉電阻的用處和區(qū)別分別又是什么呢?

2023-05-26 10:16:01 4486

4486

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個系統(tǒng)的設(shè)計中都用到了大量的上拉電阻和下拉電阻,這兩者統(tǒng)稱為“拉電阻”,最基本的作用是:將狀態(tài)不確定的信號線通過一

2023-06-07 15:20:05 4301

4301

芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn) 生降低輸入阻抗,提供泄荷通路。5、 芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、 提高總線

2017-08-28 09:27:18

芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn) 生降低輸入阻抗,提供泄荷通路。5、 芯片的管腳加上拉電阻來提高輸出電平,從而提高芯片輸入信號的噪聲容限增強抗干擾能力。6、 提高總線

2017-11-16 17:14:38

硬件電路中的上拉電阻為什么能上拉?

2021-01-28 07:50:20

高電平的值。 2、OC門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉

2019-06-27 05:55:08

上拉電阻對編碼器信號造成什么影響?為什么DMA能夠不需要CPU的介入傳輸數(shù)據(jù)?

2021-10-19 09:01:15

。2、OC 門電路必須加上拉電阻,以提高輸出的搞電平值。3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS 芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉...

2021-07-27 06:52:51

。2、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗

2014-05-12 08:24:37

Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法Quartus II 中管腳上拉電阻(弱上拉)的設(shè)置方法在使用 Altera 的 FPGA 時候,根據(jù)系統(tǒng)設(shè)計需要在管腳的內(nèi)部加上上拉電阻

2012-08-12 16:10:09

的內(nèi)部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為

2015-01-22 14:41:34

在使用TPL0501可編程電阻的過程中,發(fā)現(xiàn)上單默認阻值好像會變化,但是在手冊中好像沒有相關(guān)的描述?

應(yīng)用的場景為在電源電路中使用TPL0501作為分壓電阻,使用程序來控制輸出電壓。剛開始

2024-11-26 06:58:18

fpga管腳接上拉電阻,此時我不能將此管腳配置為輸出0,但可以輸出1,不知道這是為什么,還請高手解答!

2014-04-09 15:00:25

請問在tpl0102的使用過程中,如果SCL,SDA,沒有接上拉電阻,直接連接到了P1.6P1.7上,會造成什么后果,會使單片機無法控制那塊芯片嗎?因為已經(jīng)制成pcb,請問出了再影接上拉電阻,有沒有通過程序來修改這個后果的方法。謝謝!

2025-02-10 06:14:39

嗨,專家我記得以前的FPGA,例如Virtx5,在配置指南中。它說用戶應(yīng)該在CCLK中添加一個上拉和下拉電阻,值為100歐姆。雖然在7系列配置指南中沒有這種要求,但只提到“將CCLK視為關(guān)鍵時鐘信號

2020-07-14 06:04:38

的內(nèi)部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為三個過程

2015-01-20 17:37:04

嗨,大家好,我遇到了Xilinx ISE映射過程的棘手問題。當我綜合我的設(shè)計時,我得到了一些FPGA資源的利用。雖然在映射過程中映射到FPGA上的LUT時,所有利用率都會達到0%。他很可能是由于

2020-06-13 09:57:50

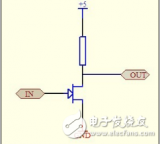

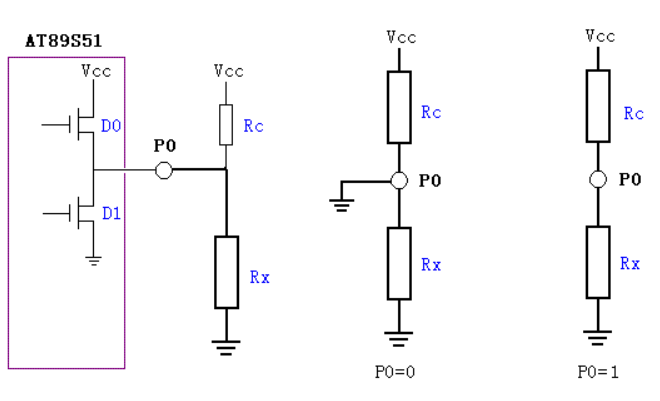

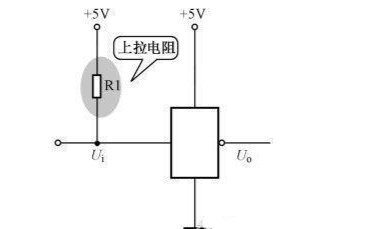

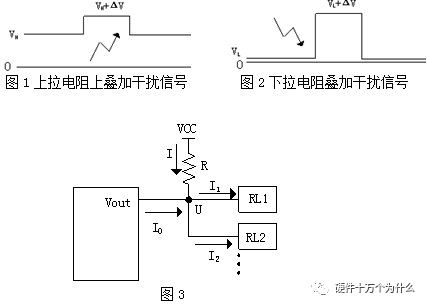

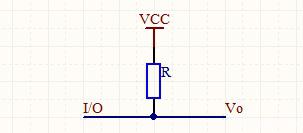

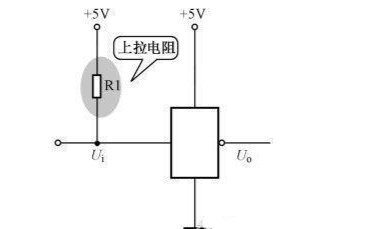

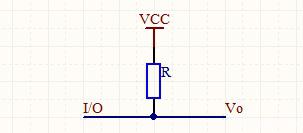

”,造成電路的不穩(wěn)定;一、上拉電阻如圖所示:1、概念:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平; 2、上拉是對器件注入電流;灌電流; 3、當一個接有上拉電阻

2022-01-14 08:28:26

。

4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。同時管腳懸空就比較容易接受外界的電磁干擾(MOS器件為高輸入阻抗,極容易引入外界干擾

2024-08-22 13:59:35

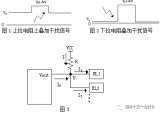

上電過程 上電過程電源不是線性增加,而會出現(xiàn)電壓降低的現(xiàn)象,如圖所示,稱為上電回溝。 這個問題覺得應(yīng)該分兩種情況分析: 1. 高速電路上信號線的回鉤:反射,串擾,負載瞬變... 2. 電源電路上的回

2021-12-31 06:59:38

本帖最后由 一只耳朵怪 于 2018-6-14 10:48 編輯

請問TMS320F28035上電過程中是否將IO口設(shè)置為輸入狀態(tài)?上拉電阻多大?

2018-06-14 06:26:13

上拉電阻與下拉電阻

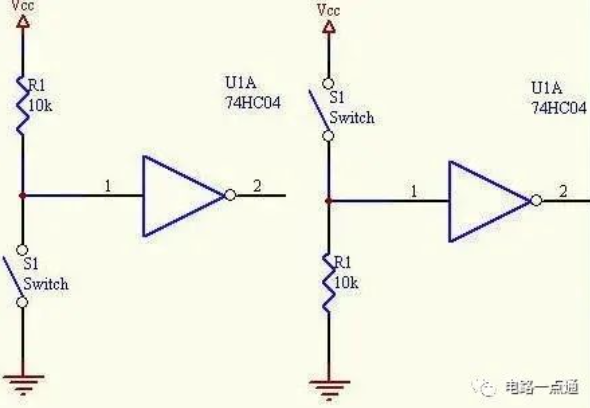

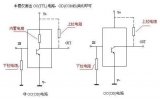

上下拉電阻: 1、當TTL電路驅(qū)動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),

2008-01-14 13:10:44 6894

6894 AVR管腳外部上拉電阻阻值選擇分析

AVR微控制器的I/O口是雙向口。具有如下的特點:

AVR IO具備多種IO模式:

2008-10-26 10:48:44 1833

1833

上拉電阻在什么情況下使用:

2、OC門電路必須加上拉電阻,才能使用。3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上

2009-05-24 11:27:15 4812

4812 什么是上拉電阻,什么是下拉電阻?它們的作用是什么?

上拉電阻一般是一端接電源,一端接芯片管腳的電路中的電阻,下拉電阻一般是指一端接芯片管

2009-06-28 10:13:44 112840

112840

上拉下拉電阻(zz)基礎(chǔ)知識

一、什么是上拉電阻?什么是下拉電阻?

上拉就是將不確定的信號通過

2009-11-23 09:16:09 5711

5711 上拉電阻和下拉電阻的選型和計算,根據(jù)不同情況選擇不同上下拉電阻的方法

2015-11-30 18:20:28 0

0 關(guān)于上拉電阻和下拉電阻的入門必知,新手要學(xué)

2016-02-17 11:21:25 0

0 上拉電阻在電路中的主要作用就是對電流起到限流作用,在一些設(shè)計當中經(jīng)常會用到上拉與下拉電阻,但電源的設(shè)計者們往往對這兩種電阻了解的不多,正因如此,在電路出現(xiàn)因為上拉與下拉電阻而導(dǎo)致的問題時,設(shè)計者們卻會找不到相應(yīng)的解決方法。

2016-05-30 13:46:53 3337

3337 電子專業(yè)單片機相關(guān)知識學(xué)習(xí)教材資料——上拉電阻與下拉電阻的應(yīng)用,感興趣的小伙伴們可以瞧一瞧。

2016-09-13 17:46:48 0

0 上拉電阻、下拉電阻、限流電阻的原理和作用

2016-11-11 18:42:28 59

59 上拉電阻和下拉電阻的作用及選擇

2016-12-15 18:39:07 27

27 介紹上拉電阻

2017-02-28 22:08:55 2

2 上拉電阻的作用

2017-03-04 17:53:55 9

9 所謂上,就是指高電平;所謂下,是指低電平。上拉,就是通過一個電阻將信號接電源,一般用于時鐘信號數(shù)據(jù)信號等。下拉,就是通過一個電阻將信號接地,一般用于保護信號。

2017-08-23 18:00:14 40166

40166

上拉電阻及其應(yīng)用

2017-09-26 08:39:19 15

15 上拉電阻很大,提供的驅(qū)動電流很小,叫弱上拉;反之叫強上拉。為什么要使用拉電阻:上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用,下拉同理。。上拉是對器件注入電流,下拉是輸出電流,弱強只是上拉電阻的阻值不同

2017-10-25 11:17:14 49919

49919

門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗,提供泄荷通路。 5、芯片的管腳加上拉電阻來提高輸出電平,從而提

2017-11-17 16:11:45 33

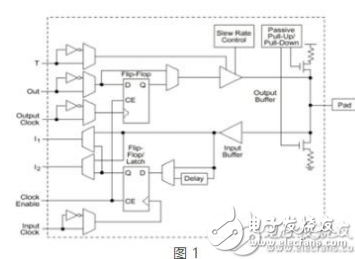

33 提出了由于FPGA容量的攀升和配置時間的加長,采用常規(guī)設(shè)計會導(dǎo)致系統(tǒng)功能失效的觀點。通過詳細描述Xilinx FPGA各種配置方式及其在電路設(shè)計中的優(yōu)缺點,深入分析了FPGA上電時的配置步驟和工作

2017-11-22 07:18:34 8500

8500

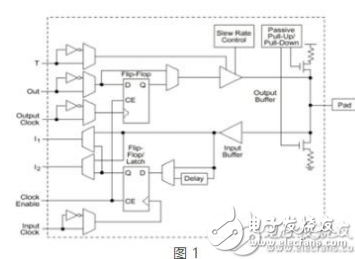

在進行FPGA硬件設(shè)計時,引腳分配是非常重要的一個環(huán)節(jié),特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態(tài),會對硬件設(shè)計、引腳分配產(chǎn)生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態(tài)進行分析。

2017-11-28 14:41:06 16918

16918

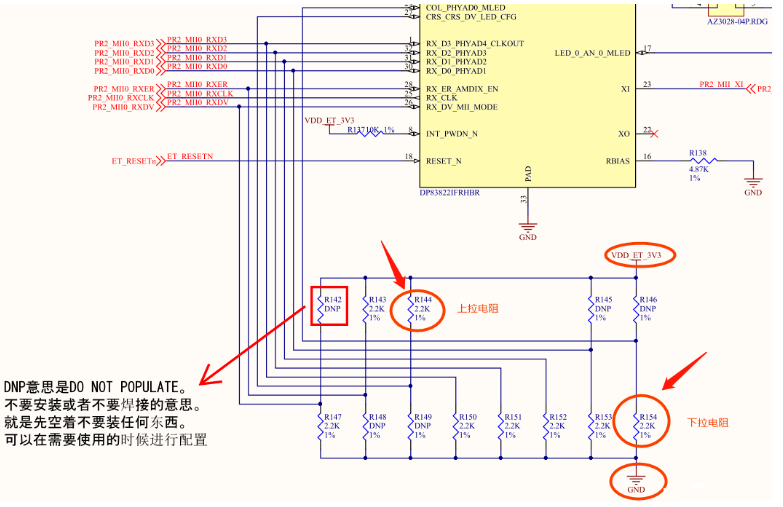

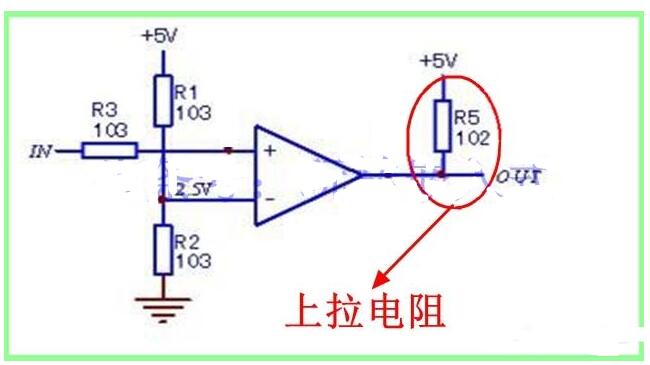

手機原理設(shè)計中,上拉電阻常用在中斷,GPIO控制,I2C等信號上,本文希望能通過實例分析加深對上拉電阻的理解。

2017-12-21 17:03:44 5968

5968

上拉電阻的作用及阻值的選擇原則

2018-03-21 11:17:55 2

2 對于驅(qū)動TTL集成電路,上拉電阻的阻值要用1~10K之間的,有時候電阻太大的話是拉不起來的,因此用的阻值較小。但是對于CMOS集成電路,上拉電阻的阻值就可以用的很大,一般不小于20K,通常用100K

2018-05-26 09:16:09 25913

25913

管腳的電路中的電阻,下拉電阻一般是指一端接芯片管腳一端接地的電阻。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。

2018-08-30 18:33:16 132792

132792 本文首先介紹了上拉電阻阻值的選擇原則,其次介紹了上拉電阻阻值計算原則。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2018-08-30 18:37:13 21819

21819 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻

2018-10-28 09:32:49 23753

23753

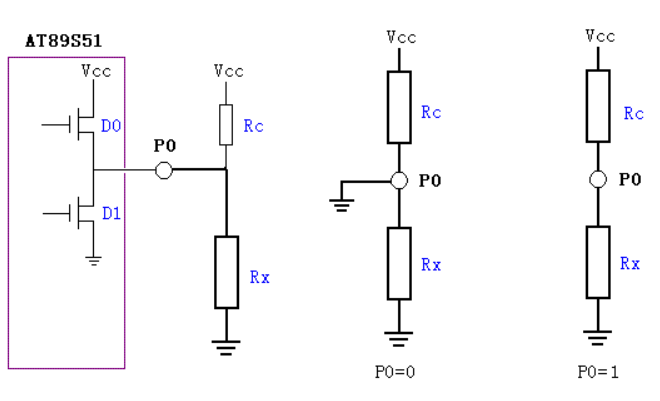

在學(xué)習(xí)單片機的時候,我們經(jīng)常遇到一組名詞:上拉電阻和下拉電阻,通過學(xué)習(xí)我們知道上下拉電阻不僅能使當前電平穩(wěn)定避免受到干擾,同時上拉電阻還能提高單片機的驅(qū)動能力。

2019-02-11 10:00:00 26607

26607

在數(shù)字電路的應(yīng)用中,時常會聽到上拉電阻、下拉電阻,上拉電阻、下拉電阻起著穩(wěn)定電路工作狀態(tài)的作用。

2019-08-07 14:30:02 11412

11412

接電源正極的拉電阻稱之為上拉電阻,接電源負極的拉電阻稱之為下拉電阻;在數(shù)字電路的世界中只能識別“0”和“1”,加入上拉電阻,可以把未知狀態(tài)的電路控制為高電平“1”;加入下拉電阻,可以把未知狀態(tài)的電路控制為低電平“0”,可以有效的防止意外發(fā)生。

2019-09-07 10:01:44 21234

21234

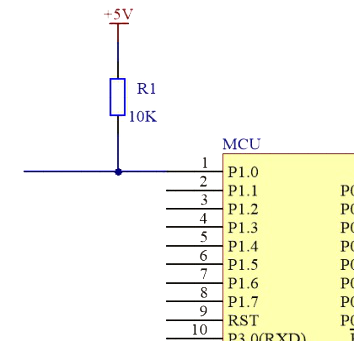

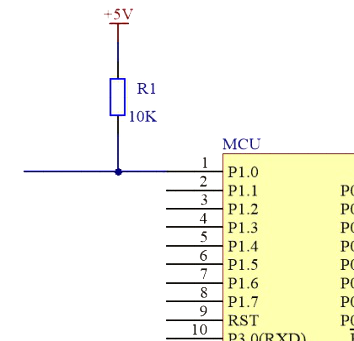

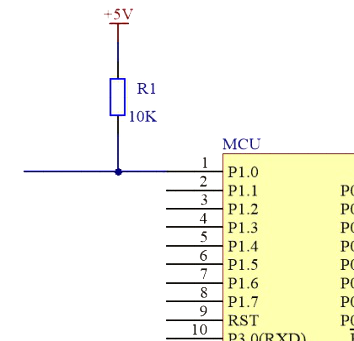

所謂上拉電阻,就是將單片機的GPIO口通過一個電阻接至電源,在初始情況下給該GPIO引腳一個確定的高電平,防止沒有上拉電阻而導(dǎo)致誤動作。

2019-10-11 15:32:21 49588

49588

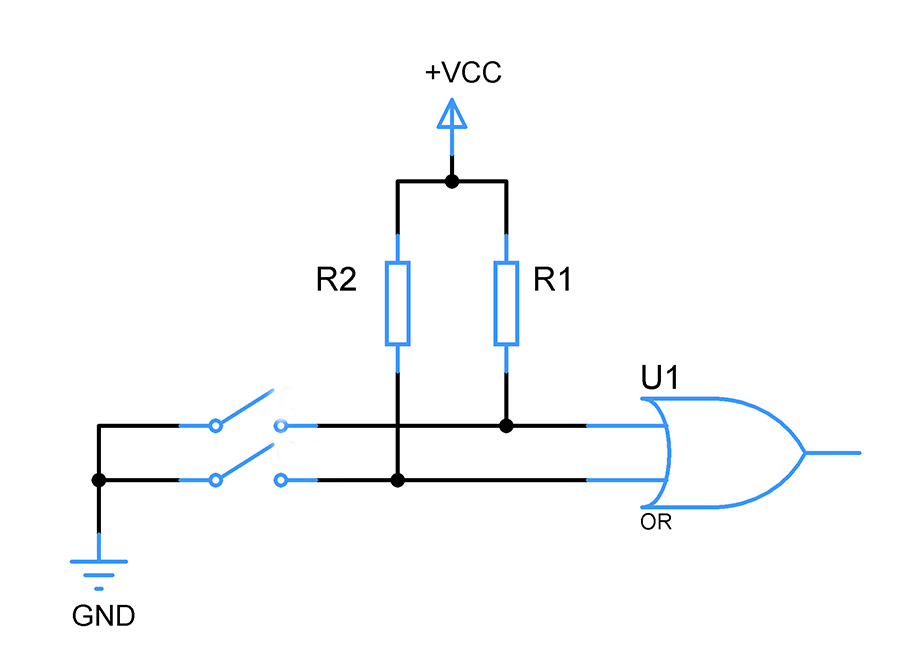

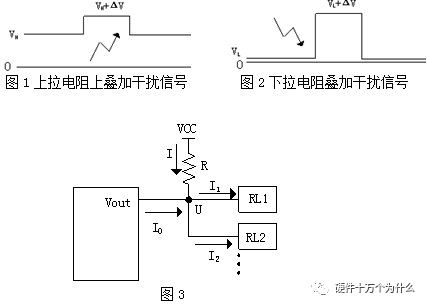

在上拉電阻和下拉電阻的電路中,經(jīng)常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經(jīng)常會串一個電阻?

2020-04-28 14:17:04 12802

12802

電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個系統(tǒng)的設(shè)計中都用到了大量的上拉電阻和下拉電阻。

在上拉電阻和下拉電阻的電路中,經(jīng)常有的疑問是:上拉電阻為何能上拉?下拉電阻為何能下拉?下拉電阻旁邊為何經(jīng)常會串一個電阻?

2021-01-27 08:43:08 28

28 在使用Altera的FPGA時候,由于系統(tǒng)需求,需要在管腳的內(nèi)部加上上拉電阻。Quartus II軟件中在Assignment Editor中可以設(shè)置。具體過程如下:

2021-01-29 16:26:51 16

16 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2021-02-20 14:20:15 10694

10694

經(jīng)常看到芯片設(shè)計手冊時,芯片外圍會有上拉或者下拉電阻還有一些無源器件。如何選擇正確值的上拉電阻和下拉電阻?上拉電阻和下拉電阻是如何確定?還是在選擇此類電阻的時候,有個特定的范圍?對上拉電阻和下拉電阻

2021-11-07 13:51:03 27

27 門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻...

2021-11-17 15:36:01 8

8 門電路必須加上拉電阻,才能使用。 3、為加大輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。 4、在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻...

2021-11-24 11:51:07 3

3 上拉電阻和下拉電阻上拉電阻(Pull-Up)所謂上拉電阻就是用一個電阻將VCC和單片機的IO口直接連接起來,目的是當IO在沒有輸出一個確定信號時將IO的電位鉗在一個高電平上。上拉電阻作用如下:1.當

2021-12-01 09:21:05 11

11 1、介紹使用微控制器(MCUs) 或任何數(shù)字邏輯設(shè)備時,上拉電阻器非常常見。本教程將解釋何時何地使用上拉電阻器,然后我們將做一個簡單的計算,以顯示為什么上拉很重要。2、上拉電阻是什么?假...

2021-12-05 18:36:04 17

17 電阻,以提高輸出高電平的值。2、OC門電路必須使用上拉電阻,以提高輸出的高電平值。3、為增強輸出引腳的驅(qū)動能力,有的單片機管腳上也常使用上拉電阻。4、在CMOS芯片上,為了防止靜電造成損壞,不用的管腳

2022-01-14 13:58:34 3

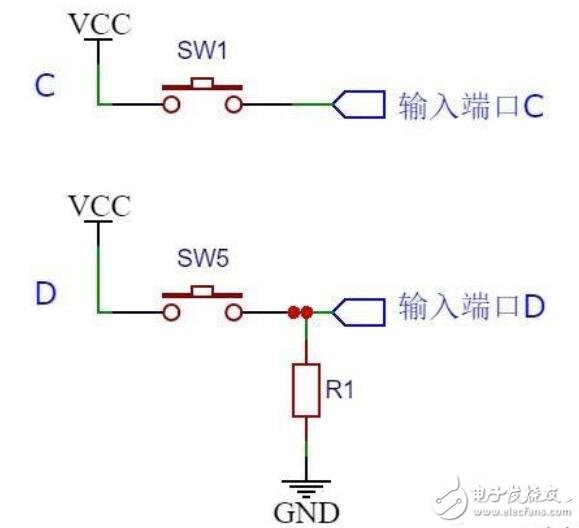

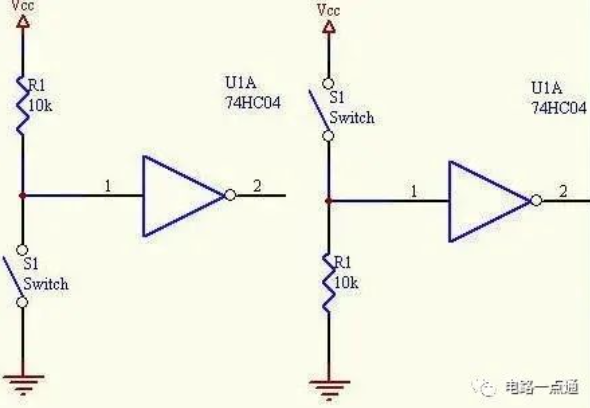

3 上拉電阻和下拉電阻的區(qū)別及案列分析上拉電阻在一個信號未過來之前、默認(保證)該電位的電平信號是高電平,在信號過來后如果是高電平、那么保持高電平。如果過來低電平信號、那么輸出的信號就會變成低電平。改圖

2022-01-14 14:02:34 26

26 上拉電阻和下拉電阻的選型和計算上下拉電阻的出發(fā)點在正常工作或單一故障狀態(tài)下,管腳均不應(yīng)出現(xiàn)不定狀態(tài)從功耗角度考慮,在長時間的管腳等待狀態(tài)下,管腳端口的電阻不應(yīng)消耗太多電流上下拉的選擇從抗擾角度出發(fā)

2022-01-14 14:06:35 34

34 的原理與應(yīng)用 2者共同的作用是:避免電壓的“懸浮”,造成電路的不穩(wěn)定; 一、上拉電阻如圖所示: 1、概念:將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平; 2、上拉是對器件注入電流;灌電流; 3、當一個接有上拉電阻

2022-01-14 14:07:36 22

22 拉下拉。電阻在電路上拉或者下拉,常見于單片機的IO端口,以及MOS的驅(qū)動輸出或者I2C這樣的信號上,有人選擇1K,有人選擇10K,有人選擇100K,那么我們在電路設(shè)計中,到底選擇多大的電阻比較合適呢

2022-01-14 14:09:36 4

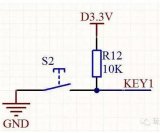

4 I2C上拉電阻 在一些PCB的layout中,大家往往會看到在I2C通信的接口處,往往會接入一個4.7K的電阻,有的datasheet上面明確有要求,需要接入,有的則沒有要求。 I2C接口 對于

2022-01-14 14:10:36 10

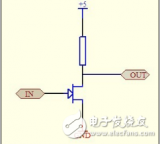

10 連接io口。而基極通過某種控制開關(guān)連接電源正極,當基極沒有電流流過時發(fā)射極和集電極處于斷開狀態(tài),此時io口為低電平。此時如果沒有上拉電阻就算將基極所連開關(guān)導(dǎo)通,集電極與發(fā)射極導(dǎo)通io口仍為低電...

2022-01-14 14:11:36 3

3 一些單片機型號內(nèi)部設(shè)置上拉電阻,因此有些上拉能力夠,可以不加上拉電阻,有些不夠,主要看所使用的單片機是否使用標準的IIC接口,若使用標準IIC接口,在使能引腳時即將進入漏極開路模式,可不用外部上拉

2022-01-14 14:16:37 6

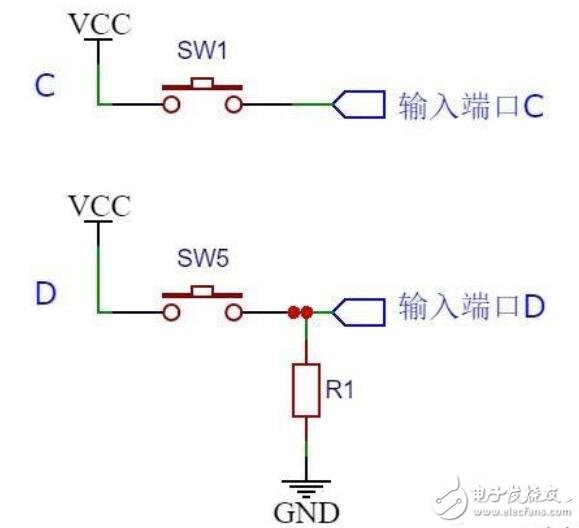

6 在電路設(shè)計中,為了將電阻鉗位維持在高電平,會借助上拉電阻來實現(xiàn)電阻的穩(wěn)定,因此上拉電阻開始大量出現(xiàn)在電路設(shè)計中。本文從以鍵盤電路實例為切入點,為大家分析一種由于上拉電阻位置原因?qū)е?1單片機電路無法正常運行的情況。

2022-02-09 11:32:03 1

1 上拉(Pull Up )或下拉(Pull Down)電阻(兩者統(tǒng)稱為“拉電阻”)最基本的作用是:將狀態(tài)不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉),無論它的具體用法如何,這個

2022-02-11 10:50:27 29

29 把一個信號通過一個電阻接到高電平,叫作上拉,這個電阻充當?shù)淖饔镁褪?b class="flag-6" style="color: red">上拉電阻。

2022-03-29 14:16:51 4

4 目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-08-15 09:13:31 2967

2967 是將電壓拉低,主要用在 三極管 或場管的控制極的電位,因為只有滿足電壓差才會工作。 上拉電阻: 下拉電阻: 總之: 2者共同的作用是:避免電壓的“懸浮”,造成電路的不穩(wěn)定; ? 一、上拉電阻如圖所示: 1、概念:將一個不確定

2023-02-23 16:20:02 3416

3416 電阻在電路中起限制電流的作用。上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個系統(tǒng)的設(shè)計中都用到了大量的上拉電阻和下拉電阻。

2023-03-17 15:51:07 7441

7441

上拉就是將不確定的信號通過一個電阻嵌位在高電平!電阻同時起限流作用!下拉同理

2、上拉是對器件注入電流,下拉是輸出電流

3、弱強只是上拉電阻的阻值不同,沒有什么嚴格區(qū)分

4、對于非集電極

2023-03-17 15:57:32 3946

3946

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號通過一個電阻鉗位在低電平。

2023-05-31 13:57:02 4053

4053

電阻在電路中起限制電流的作用,而上拉電阻和下拉電阻是經(jīng)常提到也是經(jīng)常用到的電阻。在每個系統(tǒng)的設(shè)計中都用到了大量的上拉電阻和下拉電阻,這兩者統(tǒng)稱為“拉電阻”,最基本的作用是:將狀態(tài)不確定的信號線通過一

2023-06-10 14:17:53 5264

5264

上拉和下拉電阻是許多數(shù)字電路的組成部分。了解什么是上拉電阻或下拉電阻很重要?為什么將其用于數(shù)字電路?以及如何選擇這些的價值?本文將回答這三個問題,并讓您更好地了解它。

2023-06-18 15:25:17 8234

8234

什么是上拉電阻?上拉電阻和下拉電阻都是電阻元器件,所謂上拉電阻就是接電源正極,下拉的就是接負極或地。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理,也是將不確定的信號

2023-06-29 17:04:31 14290

14290

上拉電阻是一個電阻,它通常被連接到電路中的高電平值,以提供一個上拉電壓。這個電阻的作用是限制電流的流動,同時為電路提供高電平值。

2023-09-06 09:16:32 3320

3320

深入分析上拉電路的原理和工作方式。 什么是上拉電路? 上拉電路是一種電路設(shè)計技術(shù),它的主要作用是將信號箝位在邏輯高電平。在數(shù)字系統(tǒng)中,邏輯高通常代表"1",而邏輯低則代表"0"。在一些情況下,我們需要將輸入的信號箝位

2023-09-12 11:36:42 5733

5733 本篇說明了在內(nèi)置上拉電阻、下拉電阻的IC中,如果沒有規(guī)定上拉電阻、下拉電阻的電阻值時的計算方法。

2023-10-18 09:27:45 4957

4957 這次簡單說說上拉電阻,那問題來了,什么是上拉電阻?上拉電阻從概念上理解就是一個電阻一端接到電源正極,一端接到輸出端。

2023-11-13 15:33:06 4779

4779

上拉電阻和下拉電阻的用處和區(qū)別? 上拉電阻和下拉電阻是電子電路中常用的兩種電阻配置方式,它們在電路中起到了關(guān)鍵的作用。下面將詳細介紹它們的用途和區(qū)別。 首先我們來介紹上拉電阻。上拉電阻是指將一個電路

2023-11-22 18:26:09 3114

3114 上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。而下拉電阻是直接接到地上,接二極管的時候電阻末端是低電平,將不確定的信號通過一個電阻鉗位在低電平。

2024-02-29 12:39:46 6264

6264

上拉電阻是一種用于保證輸入信號為預(yù)期邏輯電平的電阻元件。上拉電阻的作用在于通過一個串聯(lián)的電阻器將未定信號固定在邏輯高電平,該電阻器還具有限制電流的功能。 上拉涉及到向器件輸入端注入電流,而下拉則涉及

2024-05-02 14:51:00 5540

5540

上拉電阻有助于降低系統(tǒng)的總功耗,同時保持電路的功能性和穩(wěn)定性。那么上拉電阻如何實現(xiàn)低功耗設(shè)計呢? 以下是上拉電阻實現(xiàn)低功耗設(shè)計的幾種方法: 選擇合適的上拉電阻值: 功耗與電阻值成反比關(guān)系,一個較大

2024-05-02 15:00:00 2180

2180 在電子電路設(shè)計中,上拉電阻是一種常用的元件,它的阻值選擇至關(guān)重要,需要綜合考慮多個因素來確定合適的阻值。 一、功耗因素 功耗是選擇上拉電阻阻值時需要考慮的一個重要方面。當電阻兩端有電壓時,就會產(chǎn)生

2025-02-05 17:25:00 1424

1424 上拉電阻、下拉電阻在電子元器件間中,并不存在上拉電阻和下拉電阻這兩種實體的電阻,之所以這樣稱呼,原因是根據(jù)電阻不同使用的場景來定義的,其本質(zhì)還是電阻。上拉電阻的定義:在某信號線上,通過電阻與一個固定

2025-05-22 11:45:23 1821

1821

電子發(fā)燒友App

電子發(fā)燒友App

評論