對于 DSP、CPU、GPU、FPGA等高性能處理器而言,確保其各模塊所需電源的上電順序對實現其可靠運行、提高效率并保障整體系統健康至關重要。

2025-07-16 13:49:20 3076

3076

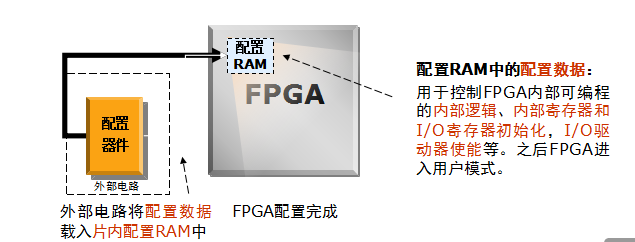

大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 17573

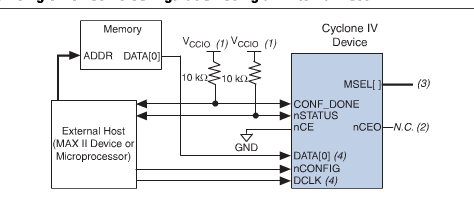

17573 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-10-24 14:52:00 1224

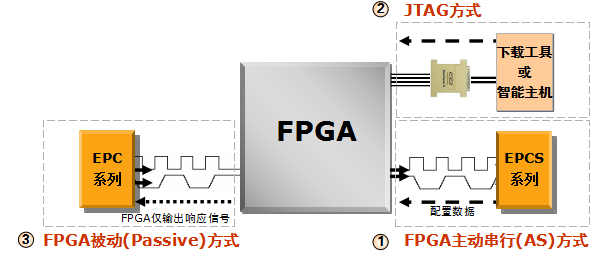

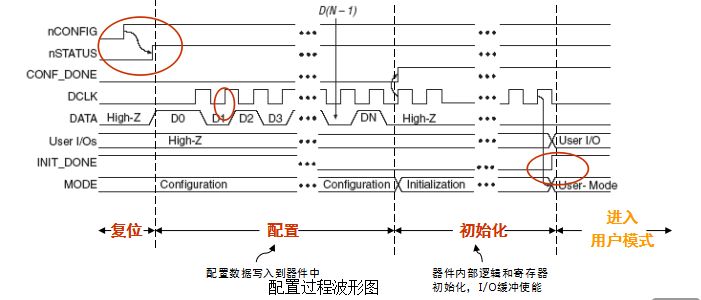

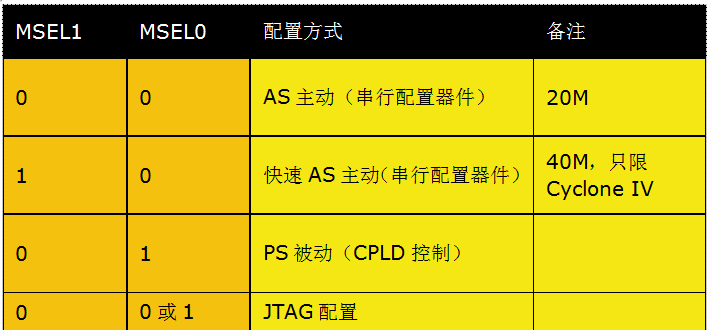

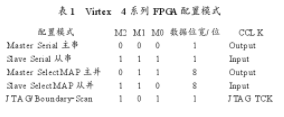

1224 等。 配置( configuration )是對FPGA的內容進行編程的過程。每次上電后都需要進行配置是基于SRAM工藝FPGA的一個特點,也可以說是一個缺點。FPGA配置過程如下:

2022-12-26 18:10:00 3584

3584 FPGA的功耗由4部分組成:上電功耗、配置功耗、靜態功耗和動態功耗。一般的FPGA都具有這4種功耗,但是Actel Flash FPGA由于掉電數據不丟失,無需配置芯片,所以上電后不需要一個很大的啟動電流,也不需要配置過程,只有靜態功耗和動態功耗,沒有上電功耗和配置功耗。

2024-07-18 11:11:00 3195

3195

`FPGA 上電配置時候IO口會有一個短暫的3.3V 10ms 的電平,導致我控制端出現問題,我想問下如何可以避免這個電平`

2020-11-23 10:31:40

FPGA上電瞬間IO管腳輸出的高電平怎么消除呢?

2023-04-23 14:48:08

FPGA與6678調試SRIO通信過程中,如DSP修改后重新編譯LOAD后,FPGA方無反應,需要斷電再上電才能通信正常,請問可能是什么原因,根據論壇例程改編的DSP程序。。。

2018-08-07 07:28:46

FPGA在軟件無線電中的應用本文結合各種實際測試介紹了羅德與施瓦茨公司的手持式頻譜儀R&S FSH在發射機與天饋線測試、無線電干擾查處以及電磁兼容診斷測試中的應用。

2012-08-12 11:55:19

的。除此之外,FPGA與傳統的開發是有很大區別的,FPGA開發的是硬件,需要對底層有深刻的了解,學習的過程也是很困難的,在這里分享幾點我的學習經驗。1、對于任何一門學問,并不是您有了所有知識儲備才開始,而是

2019-10-14 10:08:35

FPGA程序寫完編譯已用94%的資源。下載沒有問題,上電后,有時正常運行,有時一上電沒有現象,示波器看管腿的波形也沒有,懷疑FPGA沒有工作,有時epcs4的程序沒有正確下載。量了FPGA的供電也都正常。到底是什么問題呢?

2015-01-08 15:18:37

cyclone fpga jtag突然不能下載程序,測量了一下電壓,發現上電后 ,nstatus管教一直是低電平,其他供電正常 ,這是為什么呢?求幫忙解答,謝謝了

2016-09-27 20:40:03

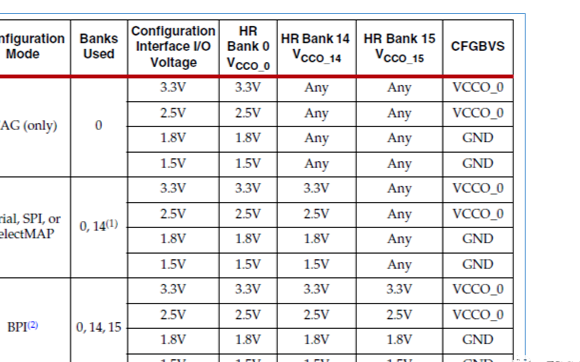

- 2.5VVCCO_35 - 2.5V連接到I / O bank的一些外部電路在2.5V FPGA電源軌之前上電(這超出了我的控制范圍)。這會以奇怪的方式導致2.5V FPGA電源軌斜坡,請參考附圖。基本上2.5VFPGA

2020-07-30 09:51:29

介紹一種無線電測向技術

2021-05-26 06:40:24

輸出。而另一個常用的組合邏輯電路有譯碼的功能,即譯碼器,其邏輯功能是編碼的逆過程,通常是將少比特的輸入編碼翻譯為多比特的數據信息輸出。由于兩者的實現方式非常類似,這里僅以編碼器中的優先編碼器為例介紹一下其在FPGA開發板上的實現過程。原作者:語雀

2022-07-21 15:38:45

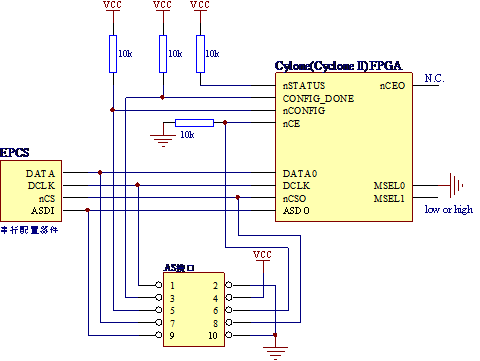

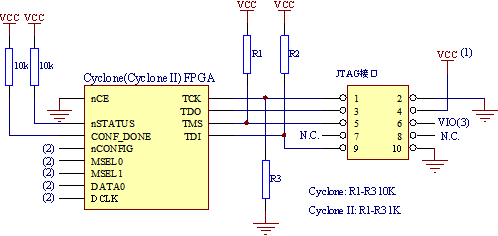

必要的。 本節介紹設計一款FPGA最小系統的過程,通過設計來學習PCB電路板(四層)和FPGA編程入門知識,具體要求如下: 方案:調試芯片+FPGA芯片+閃存要求: 01. 了解FPGA芯片最小

2023-03-27 11:57:14

ADS8686按照手冊使用fpga配置完成后,上電后出現偶發性數據全部為0.接上下載線調試,未出現過這種現象。

一般多天不用時,第一次上電出現ad輸出全部為0,但是第二次上電后全天不再出現這種現象。

2024-11-22 07:18:25

學習的時候了解到FPGA的多路供電要求一定的上電斷電順序,目前在搞Altera的Cyclone IV系列的FPGA,主要有內部邏輯供電VCCINT,PLL供電VCCD_PLL,IO口供電VCCIO等

2017-05-18 22:36:29

請問一下,LMK04806上電后,通過Microwire接口寫入寄存器的過程是怎樣的?是否有相關詳細的資料參考,謝謝。

2024-11-12 06:57:31

M032芯片的所有GPIO在MCU上電過程直到完成reset的這段過程中,是什么狀態?項目需要用GPIO控制多個外部IO,需要在設備上電過程中有明確的IO狀態。

I/O Initial State

2023-08-21 07:38:50

1,(正泰抵押研究院與翼輝信息):MCU上電后 到 用戶main函數運行 之間的過程?MCU上電也就想到與重啟復位,引起復位的原因有很多:1,上電復位2,外部產生的手動復位信號3,執行復位指令4

2021-12-13 08:05:05

和boot1電平對應的意義可能不同,下表是STM32F4xx系列的啟動方式選擇 當STM32上電時,無論哪種啟動模式,程序都將會從地址0x0000 0000開始執行,三種啟動模式只是將各自存儲空間映射到地址

2023-04-07 15:10:20

主機上掛了多個STM32 485從站, 主機不斷輪詢發送數據,STM32上電過程中如果主站已經在不斷發送數據了就STM32一直無法接收數據,不知道什么原因造成,請各位大俠指導一下。我使用中斷接收和發送方法,同時上電情況下STM32能正常發送和接收數據,實際使用過程無法保證每次都同時上電。

2025-03-13 08:11:29

STM32加電啟動的具體過程是怎樣的?

2021-11-29 06:57:08

1.同樣的板子,用過好多塊,都沒有問題,就這塊無法加載,應該不是PCB設計問題。2.我設計的是主串加載模式(Master Serial)。硬件上將FPGA的M2~M0直接接到GND上。3.上電以后

2015-08-15 09:20:26

的內部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為

2015-01-22 14:41:34

使得設計調試和檢驗變成設計周期中最困難的流程。本文重點介紹在調試FPGA系統時遇到的問題及有助于提高調試效率的技術,通過邏輯分析儀配合FPGA View軟件快速有效的觀測FPGA內部節點信號。最后提供了FPGA具體的調試過程和方法。

2019-06-25 07:51:47

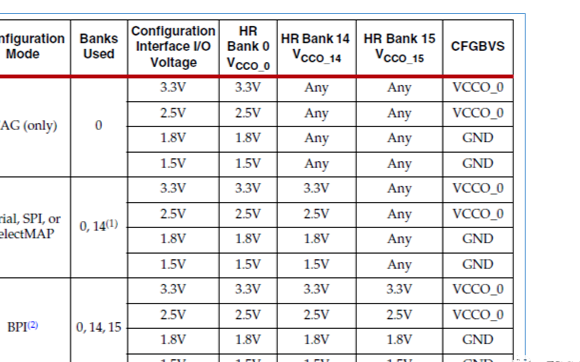

大家好,我們正在設計一個基于kintex-7 FPGA的電路板。該板具有DDR,QDR,BPI,以太網,UART等外設。我們有一個關于加電排序的查詢。有沒有要求外圍IC在FPGA上電之前應該上電,反之亦然。感謝致敬Tarang JIndal

2020-07-31 11:32:50

如何控制FPGA各電源的上電順序呢?請教一下大神

2023-03-27 13:48:32

你好,在我們的研究中,我們正在探索FPGA器件上SRAM的上電狀態的固有隨機性。因此,我們現在正試圖在啟動后從aVirtex-5器件讀出分配的RAM值。但是,根據“Virtex-5 FPGA配置指南

2020-06-18 09:26:09

最近在用AD7768在做數據采集,采用FPGA控制和處理轉換后的數據,但是將FPGA和AD7768端口鏈接后,每次上電AD都會發燙 ,斷開連線后正常,這是怎么回事

2018-08-06 09:17:15

問題描述如下:

我們的上電時序是CYUSB3014先上電,然后通過CYUSB3014的GPIO控制電源的使能讓FPGA再上電,因此CYUSB3014的3.3V_USB和FPGA的3.3V不是同一

2025-05-20 06:48:13

的內部的一些特性來試圖解決這個問題。 要解決這個問題首先要了解FPGA上電初始化過程,這里我們是以ALTERA的ArriaGX的AS模式來進行研究。第一步控制POR時間 FPGA的AS配置主要分為三個過程

2015-01-20 17:37:04

嗨,大家好,我遇到了Xilinx ISE映射過程的棘手問題。當我綜合我的設計時,我得到了一些FPGA資源的利用。雖然在映射過程中映射到FPGA上的LUT時,所有利用率都會達到0%。他很可能是由于

2020-06-13 09:57:50

本人做課設,想用FPGA輸出一個方波作為時鐘信號,使用FPGA的是Altera公司的EP1C12Q240I7,配置芯片是EPCS4I8,我用QuartusII下載了程序之后,發現只有上電和手動復位后

2016-12-08 16:20:03

有一個項目中用到OPA192這個放大器,有兩個問題:

1.V+是+12V供電的,V-是-12V供電的,想問下+12V和-12V這兩個電有沒有什么必須的上電時序需要控制?

2.還有就是我的項目

2024-07-29 08:30:16

求助:基于SRAM結構的FPGA上電瞬間電流大小如何去評估,上電瞬間的電流很大,比正常工作電流大很多,如何去評估?資料上沒找到描述,感謝討論

2019-04-18 16:50:00

求大神詳細介紹一下FPGA嵌入式系統開發過程中的XBD文件設計

2021-05-06 08:19:58

現在的FPGA還嚴格要求上電時序嗎?想請教一下大家

2017-09-26 15:39:07

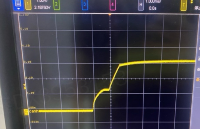

上電過程 上電過程電源不是線性增加,而會出現電壓降低的現象,如圖所示,稱為上電回溝。 這個問題覺得應該分兩種情況分析: 1. 高速電路上信號線的回鉤:反射,串擾,負載瞬變... 2. 電源電路上的回

2021-12-31 06:59:38

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行

2019-07-18 08:10:11

Hi all,

請教下Zstack中Coordinator上電過程PANID的選取問題.

跟蹤Zstack代碼最終將調用NLME接口函數NLME_NetworkFormationRequest()來

2018-06-01 12:36:31

大家好, 誰能告訴我Spartan-3AN的FPGA上電和閃存配置之間的時間間隔?謝謝RGDS以上來自于谷歌翻譯以下為原文Hi All, Could anyone tell me the Time

2019-06-27 08:15:46

請問CPLD/FPGA上電初始時IO口的狀態是怎么樣的呢?

2023-04-23 14:26:44

軟件無線電技術因為其靈活性被廣泛用于無線通信產品和射頻檢測儀器。本文介紹了軟件無線電在射頻檢測儀器和射頻檢測方法上的應用。按照軟件無線電原理,將無線產品看作射頻前端+基帶電路+輔助電路的模塊構架,就可以用射頻參數檢測替代昂貴的通信功能檢測,從而提高生產者的市場競爭力。

2019-07-22 07:32:59

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

簡化Xilinx和Altera FPGA調試過程:通過FPGAViewTM 解決方案,如混合信號示波器(MSO)和邏輯分析儀,您可以在Xilinx 和Altera FPGA 內部迅速移動探點,而無需重新編譯設計方案。能夠把內部FPGA

2009-11-20 17:46:26 27

27 摘要: 介紹基于SRAM LUT結構的FPGA器件的上電配置方式;著重介紹采用計算機串口下載配置數據的方法和AT89C2051單片機、串行EEPROM組成的串行配置系統的設計方法及

2009-06-20 10:57:26 1326

1326

本文在分析現有的解決方案優缺點的基礎上提出了一種在FPGA上實現ORB的改進設計方案,不但為彼此分離的、工作于多處理器平臺上的各個GPP,DSP和FPGA開發小組提供了通用的CORBA通信機制

2011-12-22 10:18:54 4705

4705

在使用MAX II給用戶做替代模塊的過程中,出現了一些很詭異的狀況,這些狀況也往往發生在上電伊始。因此,特權同學特別的花心思好好研究了一下MAX II的上電過程和簡單的RC復位。當

2012-05-16 15:44:02 2326

2326

本文著重介紹了 Xilinx Platform Flash PROM 如何幫助系統和電路板設計人員簡化 FPGA 配置設計。用于配置 FPGA 的可選解決方案有很多,但它們通常都需要大量的前期設計工作和時間。Platform

2013-03-14 15:18:22 64

64 Xilinx FPGA工程例子源碼:在FPGA上實現CRC算法的程序

2016-06-07 15:07:45 28

28 引腳和區域約束也就是LOC約束(location)。定義了模塊端口和FPGA上的引腳的對應關系。 那么我們應該怎么寫呢?

2018-07-14 02:49:00 11898

11898 基于Xilinx芯片的FPGA集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM 資源。在FPGA的電路設計中,上電配置電路至關重要。其中,DONE信號上拉電阻阻值的選擇很

2017-11-15 14:41:01 9168

9168

設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證

2017-11-17 03:06:01 21449

21449

一種基于FPGA的泥漿電參數測量系統的設計和實現過程,詳細介紹了每個電路模塊的功能和實現。首先從理論的角度分析了測量方法的思路,然后通過硬件電路測量不同阻抗與高精度阻抗分析儀測試結果進行對比,驗證

2017-11-17 04:23:30 1614

1614

提出了由于FPGA容量的攀升和配置時間的加長,采用常規設計會導致系統功能失效的觀點。通過詳細描述Xilinx FPGA各種配置方式及其在電路設計中的優缺點,深入分析了FPGA上電時的配置步驟和工作

2017-11-22 07:18:34 8500

8500

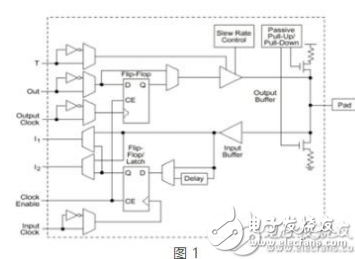

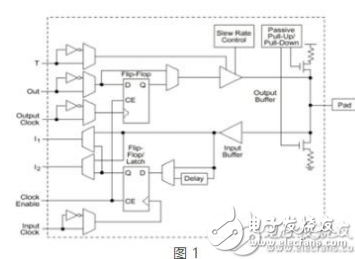

在進行FPGA硬件設計時,引腳分配是非常重要的一個環節,特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態,會對硬件設計、引腳分配產生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態進行分析。

2017-11-28 14:41:06 16918

16918

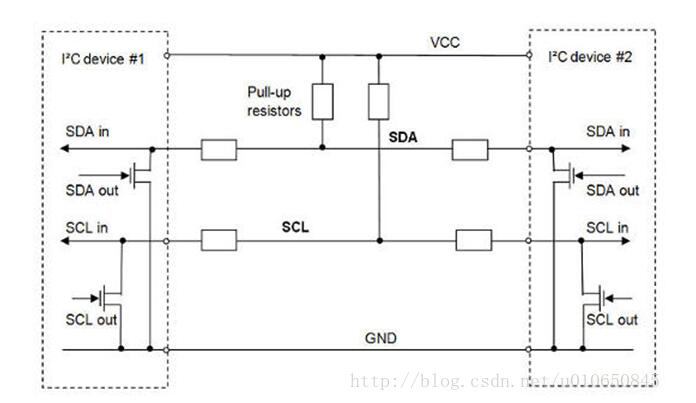

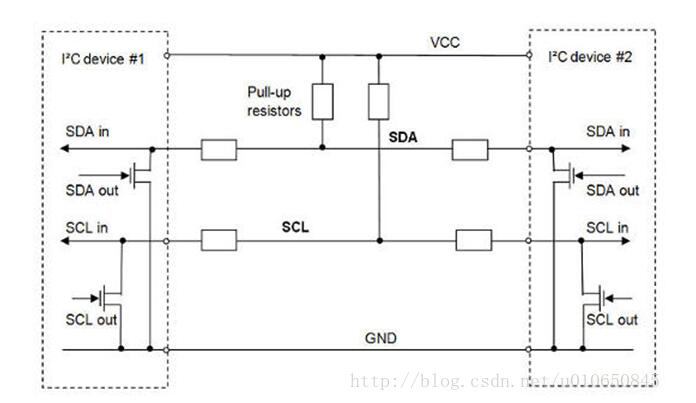

本文首先介紹了IIC總線概念和IIC總線硬件結構,其次介紹了IIC總線典型應用,最后詳細介紹了IIC總線的FPGA實現原理及實現過程。

2018-05-31 10:56:50 7184

7184

本文介紹了用FPGA來實現控制電阻的提供,用軟件的方式來設計硬件,設計過程中可用有關軟件進行各種仿真,同時整個系統可集成在一個芯片上,體積小、功耗低,可靠性高,又因為其內部有存儲單元,所以能夠滿足上述的“記憶”功能。

2018-06-14 09:06:00 4329

4329

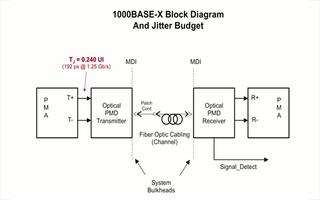

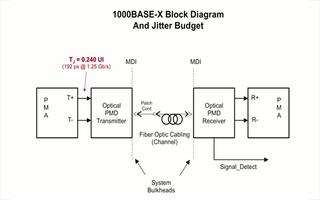

本視頻討論了UltraScale FPGA中的LVDS上的1000Base-X,支持通用I / O(SelectIO)和收發器。

演示重點關注RX和TX抖動要求。

2018-11-26 06:40:00 5194

5194

FPGA在上電后,會立刻將nSTATUS配置狀態管腳置成低電平,并在上電復位(POR)完成之后釋放它,將它置為高電平。作為配置狀態輸出管腳,在配置過程中如果有任何一個錯誤發生了,則nSTATUS腳會被置低。

2019-09-01 10:37:54 2885

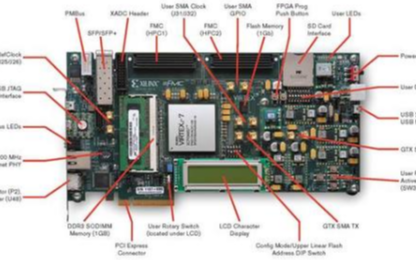

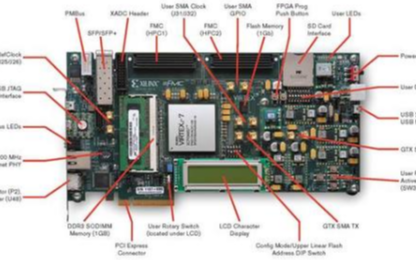

2885 FMC ( FPGA Mezzanine Card ) FPGA中間層板卡,整個FMC模塊由子板模塊、載卡兩部分構成。子板模塊和載卡之間由連接器連接,子板模塊上連接器使用公座(male),載卡上連接器使用母座(female)。

2019-10-25 14:34:56 7060

7060

本文主要介紹Xilinx FPGA的FMC接口。

2020-01-28 17:52:00 6756

6756 上一篇文章我寫了STM32的RAM和Flash,文章最后我建議大家來深入研究一下STM32上電啟動過程。同時有小伙伴留言說想讓我講一下IAP(在線升級程序)。其實如果搞懂STM32的上電啟動過程,那么IAP就可以信手拈來了。下面我們一起來研究研究。

2020-05-03 18:03:00 8761

8761 如果你在采用FPGA的電路板設計方面的經驗很有限或根本沒有,那么在新的項目中使用FPGA的前景就十分堪憂——特別是如果FPGA是一個有1000個引腳的大塊頭。繼續閱讀本文將有助于你的FPGA選型和設計過程,并且有助于你規避許多難題。

2020-11-01 09:44:54 2482

2482 AS模式(active serial configuration mode): FPGA每次上電時作為控制器,由FPGA器件引導配置操作過程,它控制著外部存儲器和初始化過程,向配置器件主動發出讀取

2021-01-05 16:21:16 21

21 選擇。 3、PROGRAM_B(input) 低電平有效,為低時,配置信息被清空,將配置過程重新進行。上電時保持PROGRAM_B為低電平不會使FPGA配置保持復位狀態。而是使用INIT_B來延遲上電配置序列。 4、INIT_B(ino

2021-01-18 13:43:10 13937

13937

FPGA本身是SRAM架構的,斷電之后,程序就消失,那么如何利用FPGA實現一個ROM呢,我們可以利用FPGA內部的RAM資源實現ROM,但不是真正意義上的ROM,而是每次上電都會把初始化的值先寫入RAM。本實驗將為大家介紹如何使用FPGA內部的ROM以及程序對該ROM的數據讀操作。

2021-02-26 06:22:53 3

3 基于SRAM結構的FPGA容量大,可重復操作,應用相當廣泛;但其結構類似于SRAM,掉電后數據丟失,因此每次上電時都需重新加載。

2021-03-26 13:52:58 6318

6318

fpga在工業上的應用有哪些?

2021-09-19 09:09:00 3799

3799 STM32上電后啟動過程

2021-11-15 18:21:02 16

16 上電過程 上電過程電源不是線性增加,而會出現電壓降低的現象,如圖所示,稱為上電回溝。 這個問題覺得應該分兩種情況分析: 1. 高速電路上信號線的回鉤:反射,串擾,負載瞬變... 2. 電源電路上的回

2022-01-11 12:02:39 13

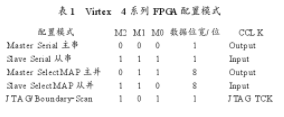

13 典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。

2022-03-14 14:02:50 2381

2381 fpga 會從 0 開始讀,地址不斷自增,直到讀取到有效的同步字 sync word(0xAA995566),才認為接下來的內容是一個有效的 bin 文件內容的開始。讀到有效 sync word 后不會再繼續讀搜尋其他的 bin 文件。如 UG470 文檔 page81 描述:

2022-07-13 09:42:08 1321

1321 電子發燒友網站提供《來自Digilent設計大賽的FPGA上的軟件定義無線電.zip》資料免費下載

2022-11-23 09:59:09 1

1 典型的主模式都是加載片外非易失( 斷電不丟數據) 性存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。

2023-02-15 09:57:24 1177

1177 存儲器中的配置比特流,配置所需的時鐘信號( 稱為CCLK) 由FPGA內部產生,且FPGA控制整個配置過程。? 在主模式下,FPGA上電后,自動將配置數據從相應的外存儲器讀入到SRAM中,實現內部結構映射;主模式根據比特流的位寬又可以分為:串行模式( 單比特流) 和并行模式( 字節寬度比

2023-03-29 14:50:06 2111

2111 電子發燒友網站提供《FPGA上的電子骰子.zip》資料免費下載

2023-06-15 11:03:49 1

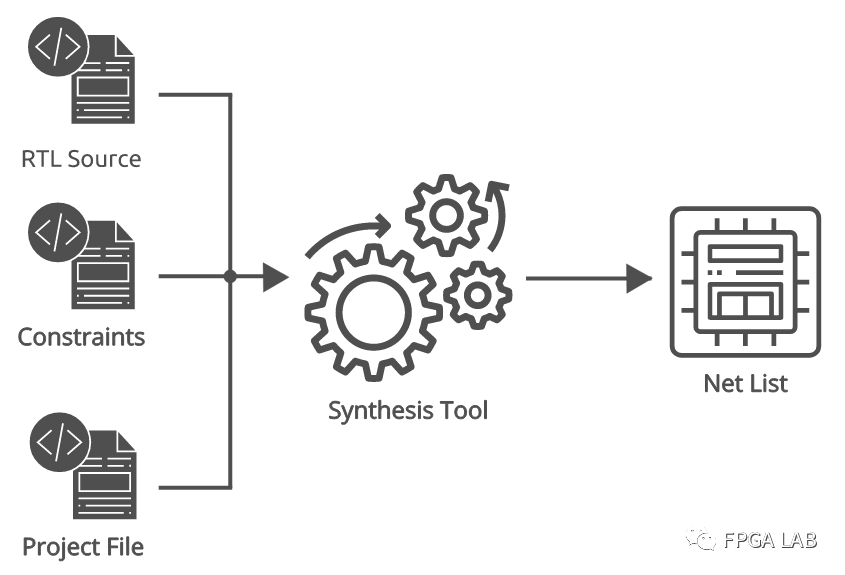

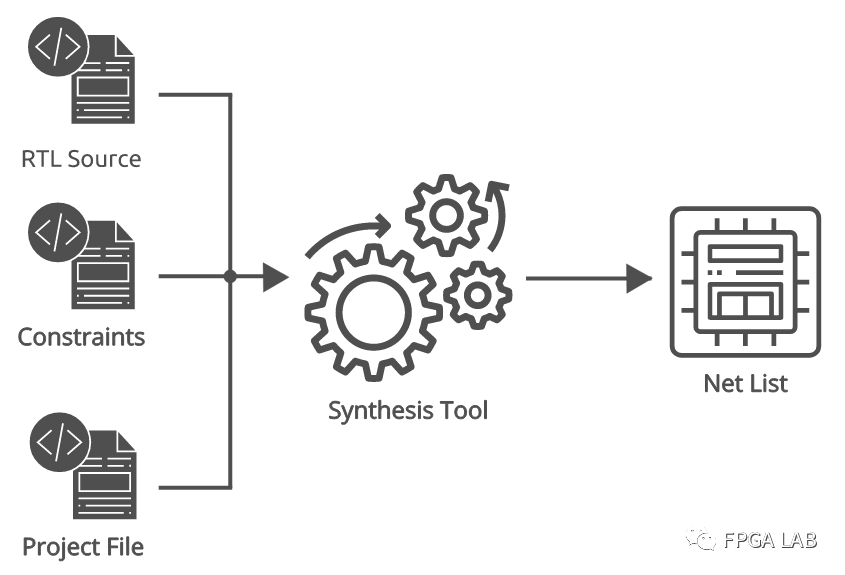

1 構建FPGA的第一階段稱為綜合。此過程將功能性RTL設計轉換為門級宏的陣列。這具有創建實現RTL設計的平面分層電路圖的效果。

2023-06-21 14:26:16 1337

1337

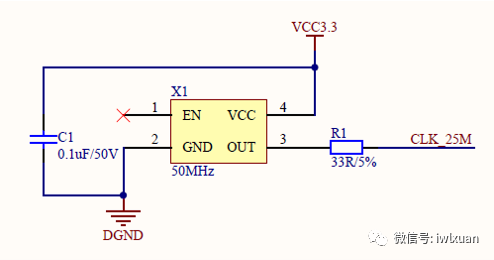

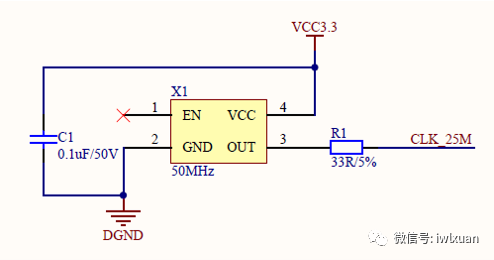

小編在本節介紹FPGA芯片外圍電路設計規范和配置過程,篇幅比較大,時鐘的設計原則就有17條,伙伴們耐心讀一讀。

2023-08-15 16:18:11 10883

10883

如何降低芯片上電時的峰值電流呢? 降低芯片上電時的峰值電流是提高芯片可靠性和效率的關鍵問題之一。在本文中,我將詳細介紹一些降低芯片上電時峰值電流的有效方法。 1. 電源設計優化 優化電源設計是降低

2023-11-07 10:42:16 3098

3098 為什么要測試芯片上下電功能?芯片上電和下電功能測試的重要性? 芯片上下電功能測試是集成電路設計和制造過程中的一個重要環節。它是確保芯片在正常的上電和下電過程中能夠正確地執行各種操作和功能的關鍵部分

2023-11-10 15:36:30 2857

2857 在MCU上電過程中,因為電源的設計或者其他器件上電導致上電波形有階梯等情況,比如下面這個VDD波形:

2024-02-19 09:40:59 2536

2536

電子發燒友App

電子發燒友App

評論