本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析。

2018-04-18 09:06:24 18789

18789

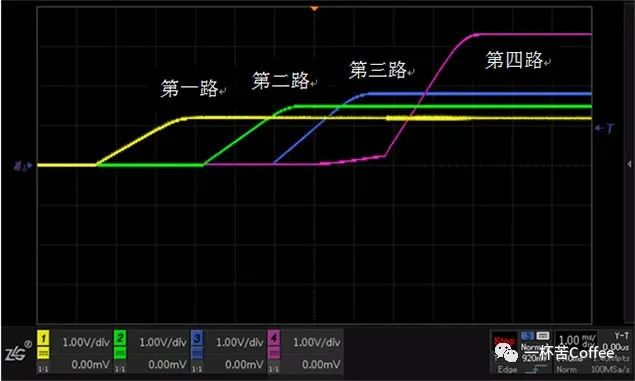

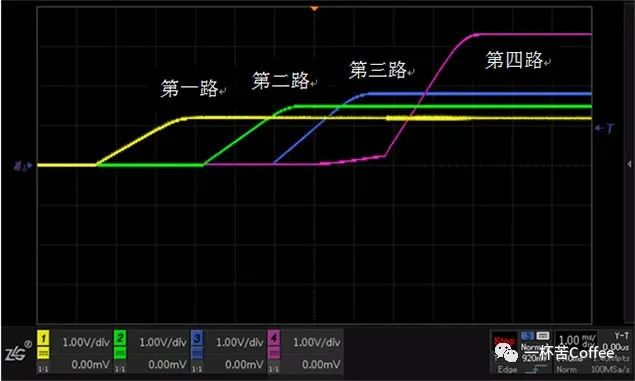

為什么電源紋波不能直接一鍵捕獲呢?為什么多路上電時序前后分析對比這么麻煩呢?

2017-04-19 10:42:54 8098

8098

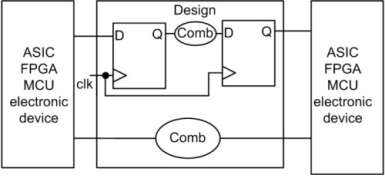

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

2017-06-21 16:05:57 8433

8433

大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2019-07-01 17:16:45 17573

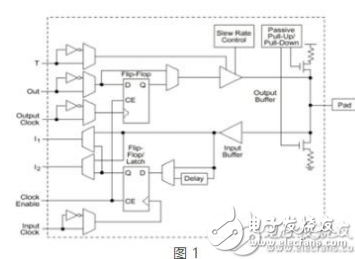

17573 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2395

2395 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-10-24 14:52:00 1224

1224 目前,大多數 FPGA 芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 3584

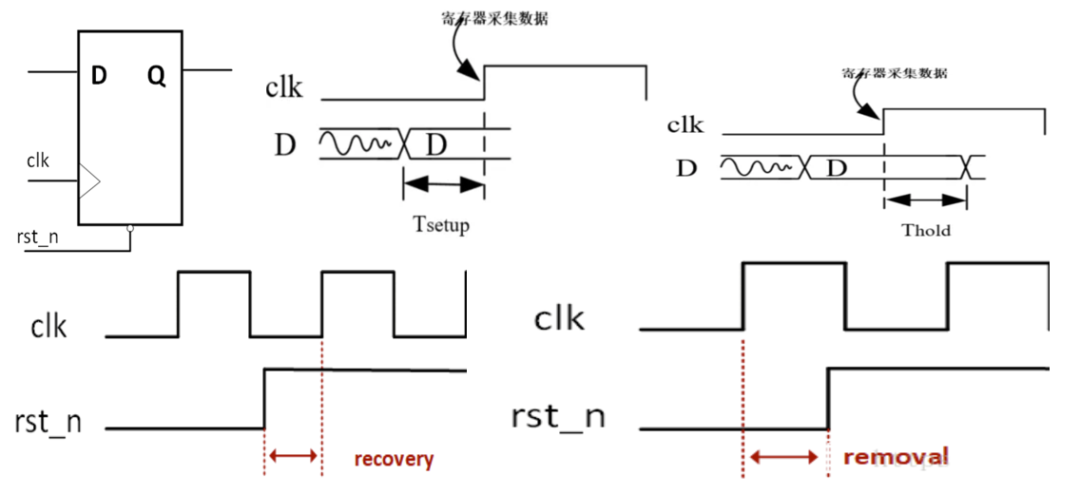

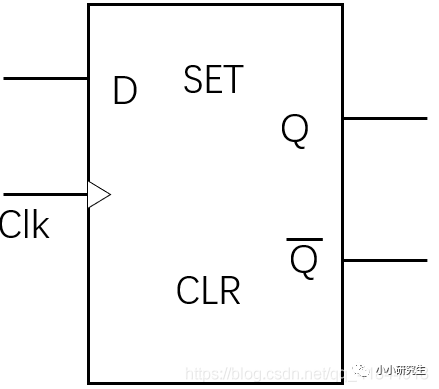

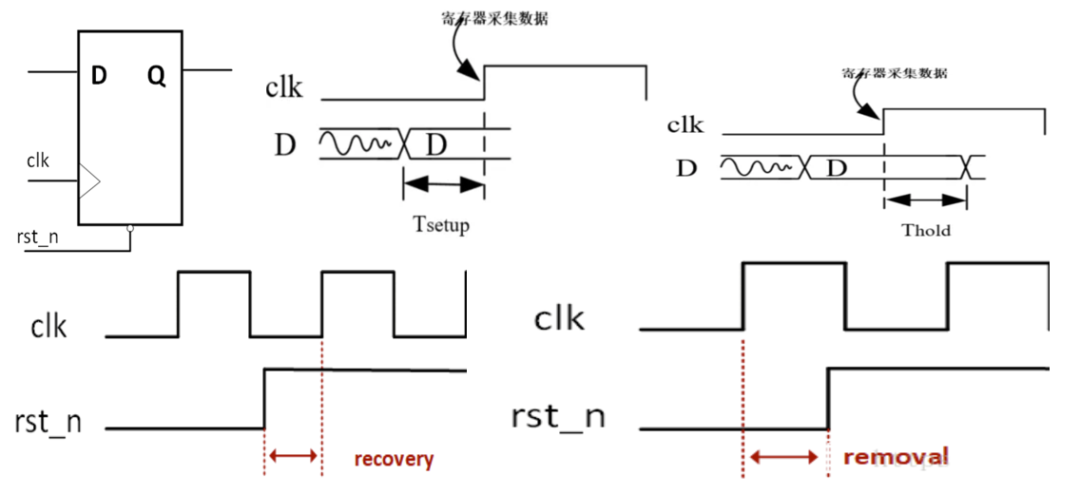

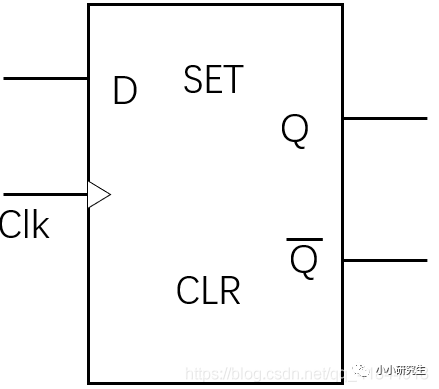

3584 時序分析本質上就是一種時序檢查,目的是檢查設計中所有的D觸發器是否能夠正常工作,也就是檢查D觸發器的同步端口(數據輸入端口)的變化是否滿足建立時間要求(Setup)和保持時間要求(Hold);檢查D

2023-07-14 10:48:19 5777

5777

今天跟大家分享的內容很重要,也是調試FPGA經驗的總結。隨著FPGA對時序和性能的要求越來越高,高頻率、大位寬的設計越來越多。在調試這些FPGA樣機時,需要從寫代碼時就要小心謹慎,否則寫出來的代碼

2023-08-01 09:18:34 3075

3075

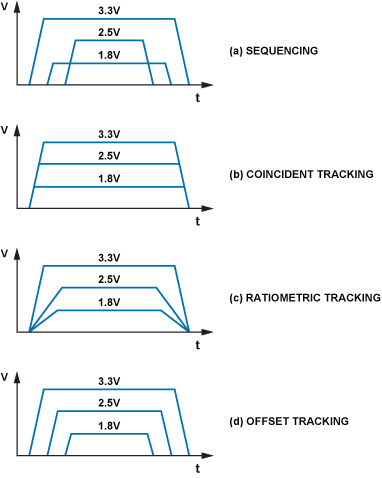

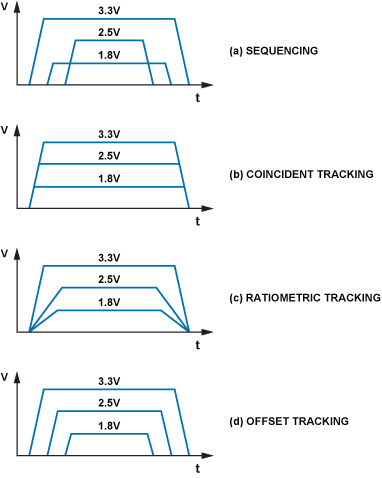

上電時序(Power-up Sequeence)是指各電源軌上電的先后關系。 與之對應的是下電時序,但是在電路設計過程中,一般不會去考慮下電時序(特殊的場景除外)。今天,我們主要了解一下上電時序控制相關內容。

2023-12-11 18:17:05 5626

5626

是 FPGA/ASIC 時序定義的基礎概念。后面要講到的其它時序約束都是建立在周期約束的基礎上的,很多其它時序公式,可以用周期公式推導。周期約束是一個基本時序和綜合約束,它附加在時鐘網線上,時序分析工具根據

2024-06-17 17:07:28

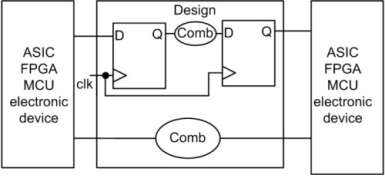

FPGA時序分析系統時序基礎理論對于系統設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數據傳輸的有效讀寫窗口越來越小,要想在很短的時間限制里,讓數據信號從驅動端完整

2012-08-11 17:55:55

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數據和時鐘傳輸路徑是由相應的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

FPGA時序分析與約束(2)——與門電路代碼對應電路模型的時序分本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:InterQuartesⅡ時序分析中常見的時間參數:Tclk1:時鐘從時鐘

2021-07-26 08:00:03

你好: 現在我使用xilinx FPGA進行設計。遇到問題。我不知道FPGA設計是否符合時序要求。我在設計中添加了“時鐘”時序約束。我不知道如何添加其他約束。一句話,我不知道哪條路徑應該被禁止。我

2019-03-18 13:37:27

經過兩天的惡補,特別是學習了《第五章_FPGA時 序收斂》及其相關的視頻后,我基本上明白了時序分析的概念和用法。之后的幾天,我會根據一些官方的文件對時序分析進行更系統、深入的學習。先總結一下之前

2011-09-23 10:26:01

影響FPGA本身的性能,而且也會給FPGA之外的電路或者系統帶來諸多的問題。(特權同學,版權所有)言歸正傳,之所以引進靜態時序分析的理論也正是基于上述的一些思考。它可以簡單的定義為:設計者提出一些特定的時序

2015-07-09 21:54:41

FPGA的時序優化高級研修班通知通過設立四大專題,幫助工程師更加深入理解FPGA時序,并掌握時序約束和優化的方法。1.FPGA靜態時序分析2.FPGA異步電路處理方法3.FPGA時序約束方法4.FPGA時序優化方法

2013-03-27 15:20:27

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-09-21 07:45:57

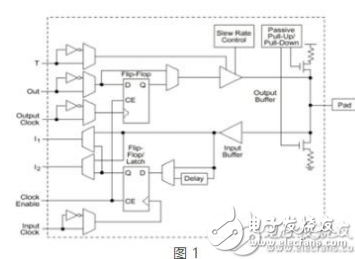

實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。1.2FPGA整體概念 由于IO口時序約束分析是針對于電路

2012-04-25 15:42:03

如題:fpga時序分析一般都做哪些分析我自己研究時序分析也有一段時間了 ,從理論到altera的timequest,差不多都了解了 ,但就是不知道一個具體的項目都要做哪些約束。求大神知道,或者有沒有這方面的資料(網上資料基本都看過了,沒有說明具體項目的)。

2012-10-22 22:20:32

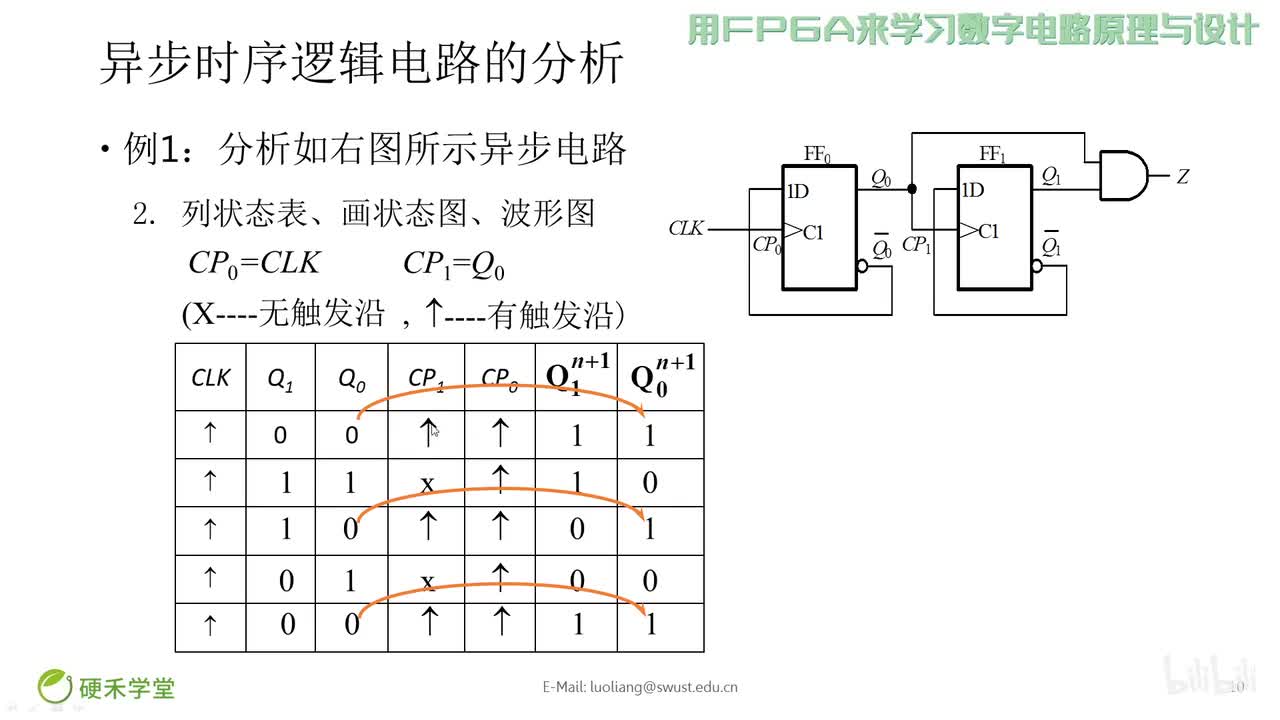

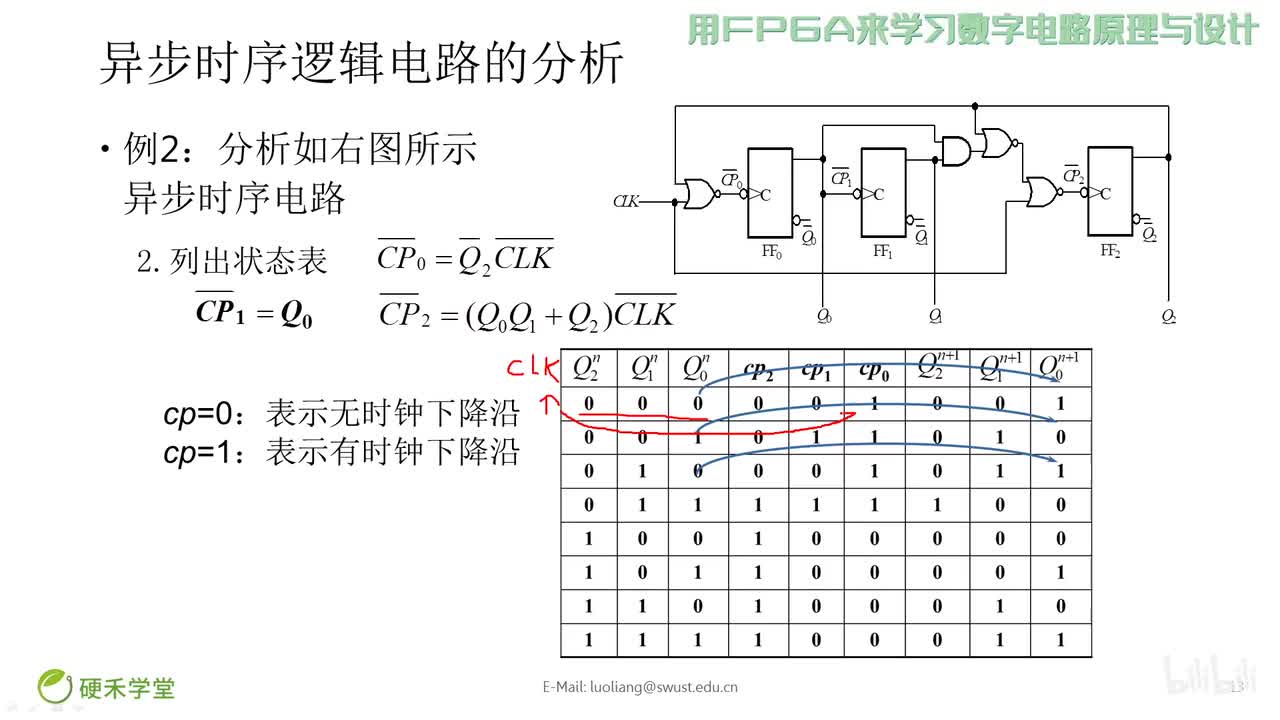

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經學習了組合邏輯電路的分析與設計的方法,這一章我們來學習時序電路的分析與設計的方法。在學習時序邏輯電路時應注意的重點是常用時序部件的分析與設計這一

2018-08-23 10:28:59

什么是時序分析?時序約束的作用是什么?FPGA組成的三要素分別是哪些?

2021-09-18 06:05:51

大家好,我們正在設計一個基于kintex-7 FPGA的電路板。該板具有DDR,QDR,BPI,以太網,UART等外設。我們有一個關于加電排序的查詢。有沒有要求外圍IC在FPGA上電之前應該上電,反之亦然。感謝致敬Tarang JIndal

2020-07-31 11:32:50

。掌握分析和確定關鍵路徑時序的方法,并通過分析找出關鍵路徑的時序問題,再對關鍵路徑進行優化,通過RTL層面的不斷優化,不斷修煉自己的設計能力,讓設計出來的電路更為靠譜有效!本資料屬大西瓜FPGA開發團隊,在此開源,與大家一起學習FPGA!

2017-02-26 09:42:48

器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。基本的電子系統如圖 1所示,一般自己的設計都需要時序分析,如圖 1所示的Design,上部分為時序組合邏輯,下部分只有組合

2018-04-03 11:19:08

模擬時序控制器IC。它能控制和監視四個電壓域。電壓的上電和關斷是通過控制相應電壓轉換器上的使能(開/關)引腳進行的。電壓轉換器的開啟時間可以利用小電容產生的時間延遲來調整。各輸出電壓通過相應的監控引腳

2021-04-12 07:00:00

有一個項目中用到OPA192這個放大器,有兩個問題:

1.V+是+12V供電的,V-是-12V供電的,想問下+12V和-12V這兩個電有沒有什么必須的上電時序需要控制?

2.還有就是我的項目

2024-07-29 08:30:16

:最終,混合信號分析儀會將分析結果以頻譜圖、波形圖等形式顯示在屏幕上,供用戶觀察和分析。

二、應用場景混合信號分析儀具有廣泛的應用場景,包括但不限于以下幾個方面:

嵌入式系統及外圍電路測試:混合信號

2025-01-21 16:45:44

現在的FPGA還嚴格要求上電時序嗎?想請教一下大家

2017-09-26 15:39:07

上電過程 上電過程電源不是線性增加,而會出現電壓降低的現象,如圖所示,稱為上電回溝。 這個問題覺得應該分兩種情況分析: 1. 高速電路上信號線的回鉤:反射,串擾,負載瞬變... 2. 電源電路上的回

2021-12-31 06:59:38

目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行

2019-07-18 08:10:11

FPGA外部的芯片,可能是FPGA內部的硬核。對于FPGA design來說,必須要關注在指定要求下,它能否正常工作。這個正常工作包括同步時序電路的工作頻率,以及輸入輸出設備的時序要求。在FPGA

2019-07-09 09:14:48

請問ADSP-BF522是不是外圍VDDEXT,VDDMEM先上電,然后VDDINT內核再上電。目前設計是5V外部供電經過BUCK電路形成3.3V給ADSP-BF522的外圍VDDEXT

2019-03-08 15:29:33

而又美好,那么我們這么多學費就沒白交哈~ 下面我們進入正題,今天我們講時序一、從靜態時序分析說起 我理解的靜態時序分析,就是我們在不加激勵的情況下,通過對電路進行時序的延遲計算,預計電路的工作流

2015-03-31 10:20:00

同步時序數字電路的分析二進制同步計數器 分析步驟: 1.確定電路是否是同步時序數字電路 2.確定觸發器的驅動方程 3.做出狀態轉換表 4.做出分析結論 BC

2008-10-20 10:10:43 30

30 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 在討論時序邏輯電路的分析與設計之前,讓我們先回顧一下在第四章中介紹過的時序電路結構框圖和一些相關術語。時序電路的結構框圖如圖5.1所示.。

2010-08-13 15:24:35 69

69 時序邏輯電路的分析方法

1. 時序邏輯電路的特點 在時序邏輯電路中,任意時刻的輸出信號不僅取決于當時的輸入信

2009-04-07 23:18:11 9154

9154

時序邏輯電路分析實例

例1 分析圖所示電路的邏輯功能。設起始狀態是

2009-04-07 23:20:25 4935

4935

介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對時序不滿足的情況,提出了幾種常用的促進 時序收斂的方

2011-05-27 08:58:50 70

70 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1476

1476 Power on Sequence:主板上的供電,從最開始的電壓適配器電壓輸入,到最后CPU供電的產生,都有嚴格的開啟順序控制,這個先后順序,就是上電時序。

2016-09-01 15:44:10 0

0 電子專業單片機相關知識學習教材資料之時序邏輯電路的分析與設計

2016-09-02 14:30:26 0

0 主板開機原理與上電時序圖

2016-12-17 21:30:39 0

0 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 為什么電源紋波不能直接一鍵捕獲呢?為什么多路上電時序前后分析對比這么麻煩呢?為什么分析調制信號時波形對比度這么差呢?事實上,用戶的每一次體驗感,都是產品隱形的提升空間。以上這三個麻煩,現在也許有了新的解決方式。

2017-04-18 14:03:16 12

12 FPGA,即現場可編程門陣列,它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。對于時序如何用FPGA來分析與設計,本文將詳細介紹。

2017-06-30 15:09:36 28

28 基于Xilinx芯片的FPGA集成了越來越多的可配置邏輯資源、各種各樣的外部總線接口以及豐富的內部RAM 資源。在FPGA的電路設計中,上電配置電路至關重要。其中,DONE信號上拉電阻阻值的選擇很

2017-11-15 14:41:01 9169

9169

一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

控制器,在介紹控制器的邏輯結構的基礎上,對FPGA與SDRAM間數據通信進行了時序分析,實現SDRAM 帶有自動預充電突發讀寫和非自動預充電整頁讀寫。

2017-11-18 12:42:03 2520

2520

在進行FPGA硬件設計時,引腳分配是非常重要的一個環節,特別是在硬件電路上需要與其他芯片通行的引腳。Xilinx FPGA從上電之后到正常工作整個過程中各個階段引腳的狀態,會對硬件設計、引腳分配產生非常重要的影響。這篇專題就針對FPGA從上電開始 ,配置程序,到正常工作整個過程中所有IO的狀態進行分析。

2017-11-28 14:41:06 16918

16918

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 128321

128321

由上電時序可知,VDD_SOC_IN上電時序要遲于VDD_HIGH_IN,因此在電路設計中,可使用VDD_HIGH_IN電源芯片的控制信號使能VDD_SOC_IN的電源,如下圖所示為使用VDD_HIGH_IN供電芯片的PG信號使能VDD_SOC_IN供電芯片的使能管腳。

2018-04-28 09:57:02 22709

22709

搞定時序分析和約束– 看懂RTL視圖和Technology視圖第三階段:從業 -> 專業從產品需求出發認識你的芯片– 芯片之內深刻理解FPGA底層結構與應用場合的對應關系– 芯片之外FPGA外圍支持電路以及高速接口FPGA與軟件接口的設計和調試做出你的產品– 公司業務– 項目流程– 領域知識

2018-06-09 09:05:35 8498

8498 現今,電子系統往往具有許多不同的電源軌。在采用模擬電路和微處理器、DSP、ASIC、FPGA的系統中,尤其如此。為實現可靠、可重復的操作,必須監控各電源電壓的開關時序、上升和下降速率、加電順序以及

2019-04-09 08:14:00 4459

4459

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 3476

3476

FPGA中的時序問題是一個比較重要的問題,時序違例,尤其喜歡在資源利用率較高、時鐘頻率較高或者是位寬較寬的情況下出現。建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2019-12-23 07:01:00 2671

2671

時序電路,是由最基本的邏輯門電路加上反饋邏輯回路(輸出到輸入)或器件組合而成的電路,與組合電路最本質的區別在于時序電路具有記憶功能。

2019-12-13 07:07:00 2425

2425

靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。

2019-09-01 10:45:27 3732

3732

Air機器的適配器電壓為14.5V,經過一個電源小板到底主板的電源接口J7000,雖然電源小板集合了很多功能,但是買一個沒多少錢,我再次就不熬贅了,只會分析主板的上電時序。

2019-11-15 08:00:00 92

92 一:供電電源時序 EMMC 的供電有兩種模式,且分兩路工作,有 VCC 和 VccQ。在規范上,上電時序是有要求的,如下圖所示。 EMMC 上電時序 開始上電時,VCC 或 VccQ 可以第一個傾斜

2020-10-30 21:29:17 3909

3909 時序分析結果,并根據設計者的修復使設計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態時序分析簡介 1.2 FPGA 設計流程 1.3 TimeQuest 的使用 1.4 常用時序約束 1.5 時序分析的基本概念

2020-11-11 08:00:00 67

67 EMMC 的供電有兩種模式,且分兩路工作,有 VCC 和 VccQ。在規范上,上電時序是有要求的,如下圖所示。

2020-12-02 23:13:00 23

23 本文檔的主要內容詳細介紹的是英業達上電時序的詳細資料說明。

2020-12-04 08:00:00 63

63 本文檔的主要內容詳細介紹的是華為FPGA硬件的靜態時序分析與邏輯設計包括了:靜態時序分析一概念與流程,靜態時序分析一時序路徑,靜態時序分析一分析工具

2020-12-21 17:10:54 22

22 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質,而且不需要再記復雜的公式了。

2021-01-12 17:48:08 19

19 在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束利序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是重點。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 AN-1080: 利用簡單時序控制器ADM108x進行上電和關斷時序控制

2021-03-21 00:41:43 6

6 電子發燒友網為你提供時序分析是FPGA如何設計?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-15 08:51:20 14

14 上電過程 上電過程電源不是線性增加,而會出現電壓降低的現象,如圖所示,稱為上電回溝。 這個問題覺得應該分兩種情況分析: 1. 高速電路上信號線的回鉤:反射,串擾,負載瞬變... 2. 電源電路上的回

2022-01-11 12:02:39 13

13 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 目前,大多數FPGA芯片是基于 SRAM 的結構的, 而 SRAM 單元中的數據掉電就會丟失,因此系統上電后,必須要由配置電路將正確的配置數據加載到 SRAM 中,此后 FPGA 才能夠正常的運行。

2022-08-15 09:13:31 2967

2967 靜態時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設計的要求,根據電路網表的拓撲結構,計算并檢查電路中每一個DFF(觸發器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為

2022-09-27 14:45:13 4033

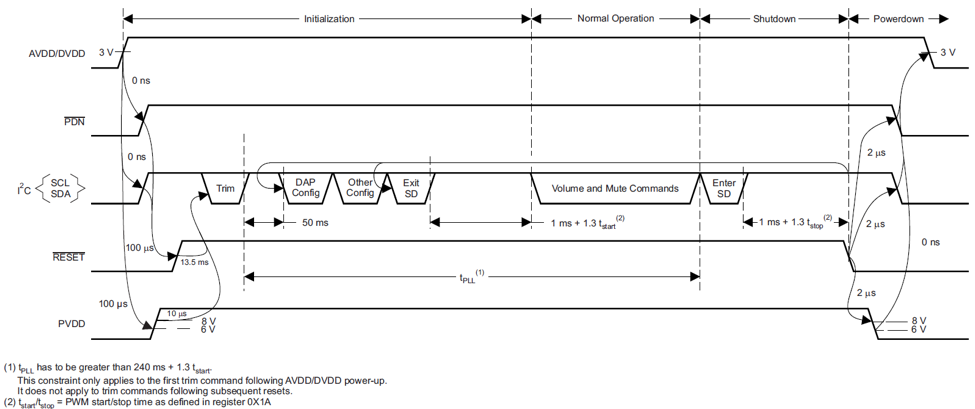

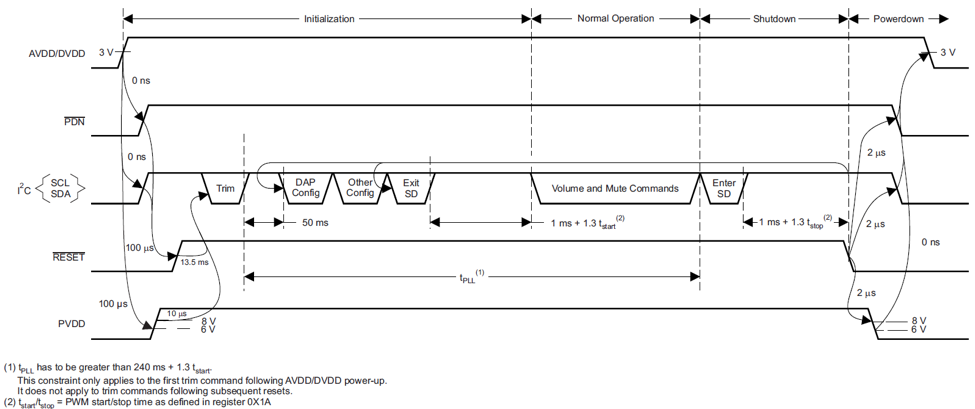

4033 Class-D 功放TAS5731M 上電時序分析

2022-10-31 08:24:00 1

1 任何學FPGA的人都跑不掉的一個問題就是進行靜態時序分析。靜態時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內容又不那么一致,為了徹底解決這個問題,終于找到了一種很簡單的解讀辦法,可以看透它

2023-03-14 19:10:03 1476

1476 master?的I2S數據。CS5343是一款音頻DAC,其通過I2S信號中的SDOUT的電平狀態來確定主從模式。在CS5343和TAS5731M結合使用時,兩顆芯片精確的上電時序控制是至關重要的,否則會出現偶爾沒有聲音的問題。具體分析如下。

2023-03-29 09:41:26 4152

4152

FPGA/CPLD的綜合、實現過程中指導邏輯的映射和布局布線。下面主要總結一下Xilinx FPGA時序約束設計和分析。

2023-04-27 10:08:22 2404

2404 時序邏輯電路會復雜很多,強烈推薦mooc上華中科技大學的數字電路與邏輯設計,是我看過講得最清楚的數電課。

2023-05-14 15:11:33 3385

3385

FPGA和外圍接口-基礎版

2023-05-22 10:57:24 1541

1541

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 5502

5502

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間。

2023-06-26 14:42:10 1252

1252

電子發燒友網站提供《嵌入式系統外圍接口的時序分析與電路設計.pdf》資料免費下載

2023-10-09 16:50:13 1

1 筆記本上電時序

2024-01-09 10:26:36 1

1 建立時間和保持時間是FPGA時序約束中兩個最基本的概念,同樣在芯片電路時序分析中也存在。

2024-08-06 11:40:18 2368

2368

本文介紹了集成電路設計中靜態時序分析(Static Timing Analysis,STA)的基本原理、概念和作用,并分析了其優勢和局限性。 ? 靜態時序分析(Static Timing

2025-02-19 09:46:35 1484

1484

電子發燒友App

電子發燒友App

評論