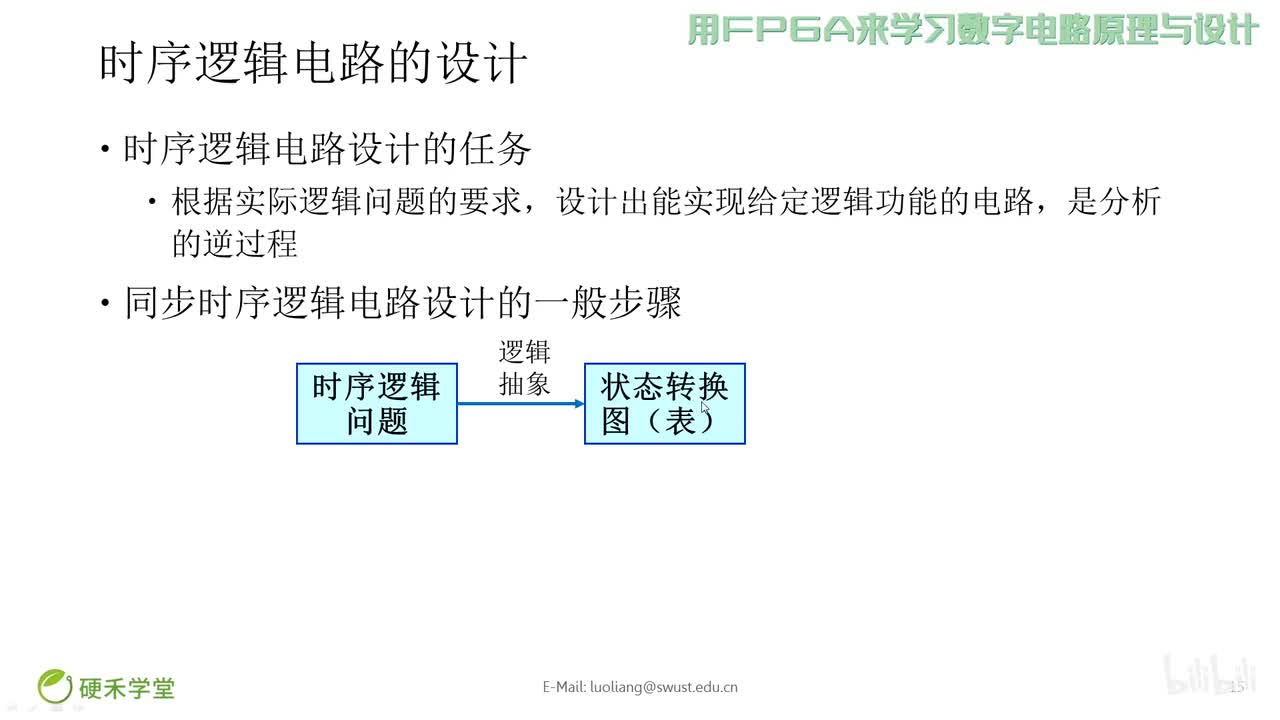

本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時(shí)序邏輯來(lái)詳細(xì)的分析。

2018-04-18 09:06:24 18789

18789

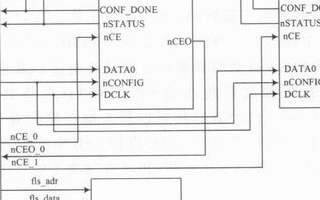

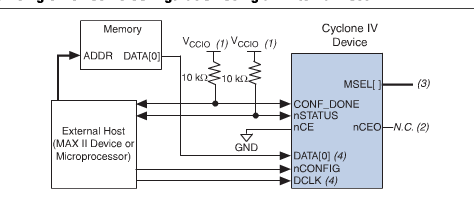

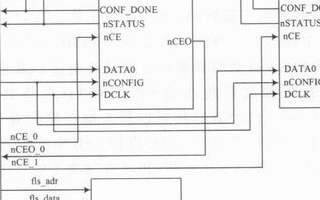

在需要多個(gè)FPGA芯片的應(yīng)用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過(guò)“成組”加載方式同時(shí)加載;

2023-02-20 10:18:27 8049

8049

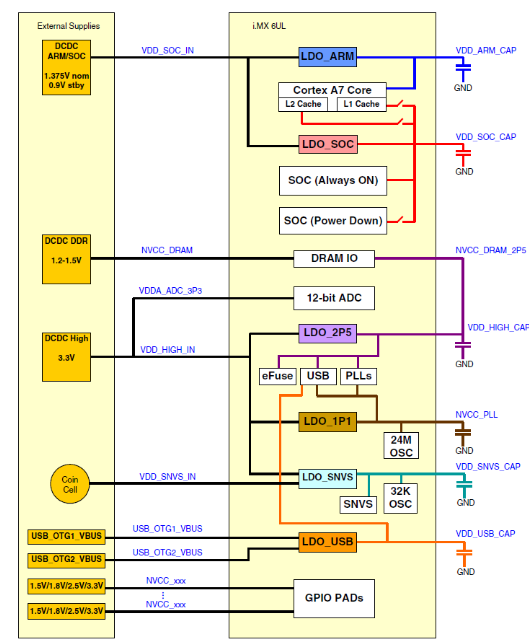

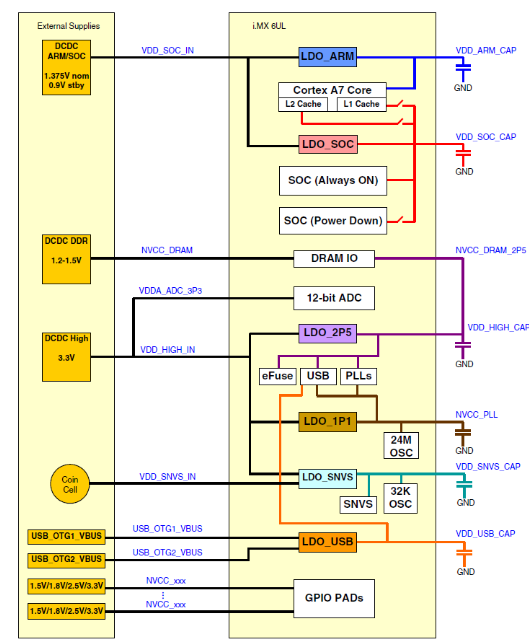

對(duì)于 DSP、CPU、GPU、FPGA等高性能處理器而言,確保其各模塊所需電源的上電順序?qū)?shí)現(xiàn)其可靠運(yùn)行、提高效率并保障整體系統(tǒng)健康至關(guān)重要。

2025-07-16 13:49:20 3076

3076

為什么電源紋波不能直接一鍵捕獲呢?為什么多路上電時(shí)序前后分析對(duì)比這么麻煩呢?

2017-04-19 10:42:54 8098

8098

為確保芯片能可靠的工作,應(yīng)用處理器的上下電通常都要遵循一定時(shí)序, 本文以i.MX6UL應(yīng)用處理器為例,設(shè)計(jì)中就必須要滿(mǎn)足芯片手冊(cè)的上電時(shí)序、掉電時(shí)序,否則在產(chǎn)品使用時(shí)可能會(huì)出現(xiàn)以下情況,第一,上電

2018-05-16 18:03:32 8364

8364

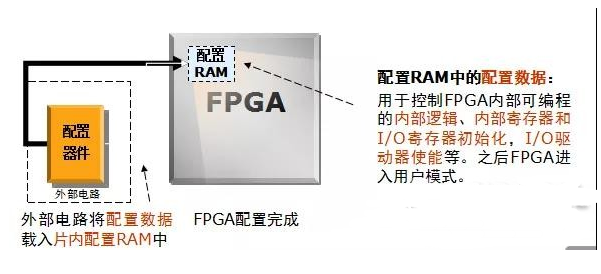

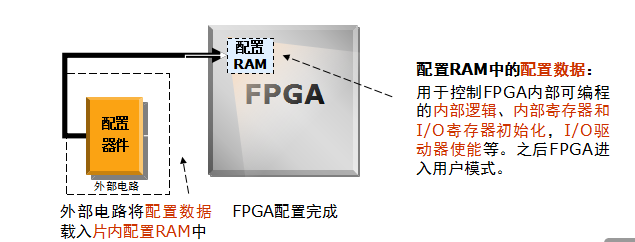

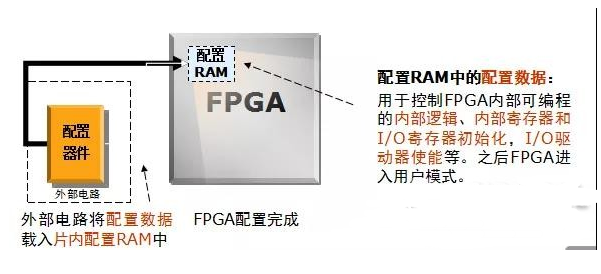

大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行。

2019-07-01 17:16:45 17573

17573 表。 這4類(lèi)路徑中,我們最為關(guān)心是②的同步時(shí)序路徑,也就是FPGA內(nèi)部的時(shí)序邏輯。 時(shí)序模型 典型的時(shí)序模型如下圖所示,一個(gè)完整的時(shí)序路徑包括源時(shí)鐘路徑、數(shù)據(jù)路徑和目的時(shí)鐘路徑,也可以表示為觸發(fā)器+組合邏輯+觸發(fā)器的模型。 該

2020-11-17 16:41:52 3687

3687

在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是一個(gè)重點(diǎn)。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 目前,大多數(shù) FPGA 芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常

2022-12-26 18:10:00 3584

3584 FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿(mǎn)足建立和保持時(shí)間。

2023-06-06 17:53:07 1938

1938

在FPGA設(shè)計(jì)中,時(shí)序約束的設(shè)置對(duì)于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的基礎(chǔ)知識(shí)。

2023-06-06 18:27:13 12757

12757

在FPGA設(shè)計(jì)中,時(shí)序約束對(duì)于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細(xì)介紹了FPGA時(shí)序約束的主時(shí)鐘約束。

2023-06-12 17:29:21 4234

4234 前面講解了時(shí)序約束的理論知識(shí)FPGA時(shí)序約束理論篇,本章講解時(shí)序約束實(shí)際使用。

2023-08-14 18:22:14 3030

3030

`FPGA 上電配置時(shí)候IO口會(huì)有一個(gè)短暫的3.3V 10ms 的電平,導(dǎo)致我控制端出現(xiàn)問(wèn)題,我想問(wèn)下如何可以避免這個(gè)電平`

2020-11-23 10:31:40

是 FPGA/ASIC 時(shí)序定義的基礎(chǔ)概念。后面要講到的其它時(shí)序約束都是建立在周期約束的基礎(chǔ)上的,很多其它時(shí)序公式,可以用周期公式推導(dǎo)。周期約束是一個(gè)基本時(shí)序和綜合約束,它附加在時(shí)鐘網(wǎng)線(xiàn)上,時(shí)序分析工具根據(jù)

2024-06-17 17:07:28

FPGA時(shí)序分析系統(tǒng)時(shí)序基礎(chǔ)理論對(duì)于系統(tǒng)設(shè)計(jì)工程師來(lái)說(shuō),時(shí)序問(wèn)題在設(shè)計(jì)中是至關(guān)重要的,尤其是隨著時(shí)鐘頻率的提高,留給數(shù)據(jù)傳輸?shù)挠行ёx寫(xiě)窗口越來(lái)越小,要想在很短的時(shí)間限制里,讓數(shù)據(jù)信號(hào)從驅(qū)動(dòng)端完整

2012-08-11 17:55:55

FPGA中幾個(gè)基本的重要的時(shí)序分析參數(shù)介紹(fmax\tsu\th\tco\tpd)今天無(wú)聊,翻開(kāi)書(shū)偶看到介紹時(shí)序部分的東西,覺(jué)得其中幾個(gè)參數(shù)縮寫(xiě)所代表的含義應(yīng)該記住,故寫(xiě)如下文章……FPGA中

2012-04-09 09:41:41

FPGA中的I_O時(shí)序優(yōu)化設(shè)計(jì)在數(shù)字系統(tǒng)的同步接口設(shè)計(jì)中, 可編程邏輯器件的輸入輸出往往需要和周?chē)缕瑢?duì)接,此時(shí)IPO接口的時(shí)序問(wèn)題顯得尤為重要。介紹了幾種FPGA中的IPO時(shí)序優(yōu)化設(shè)計(jì)的方案, 切實(shí)有效的解決了IPO接口中的時(shí)序同步問(wèn)題。

2012-08-12 11:57:59

是基于靜態(tài)隨機(jī)存儲(chǔ)器(SRAM) 結(jié)構(gòu)的,斷電后程序丟失后的每次上電都需要重新加載程序。且隨著FPGA 規(guī)模的升級(jí),加載程序的容量也越來(lái)越大,如Xilinx 公司的Spartan - 6 系列中的6SLX150T,其

2019-06-14 06:00:00

FPGA程序?qū)懲昃幾g已用94%的資源。下載沒(méi)有問(wèn)題,上電后,有時(shí)正常運(yùn)行,有時(shí)一上電沒(méi)有現(xiàn)象,示波器看管腿的波形也沒(méi)有,懷疑FPGA沒(méi)有工作,有時(shí)epcs4的程序沒(méi)有正確下載。量了FPGA的供電也都正常。到底是什么問(wèn)題呢?

2015-01-08 15:18:37

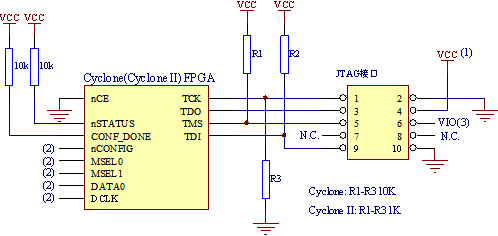

前言操作環(huán)境:Windows 7 64bitISE 14.7 FPGA程序加載與固化將開(kāi)發(fā)板通過(guò)Xilinx FPGA JTAG下載器連接到PC機(jī),打開(kāi)Windows的設(shè)備管理器查看下載器是否已正常

2020-09-25 09:57:45

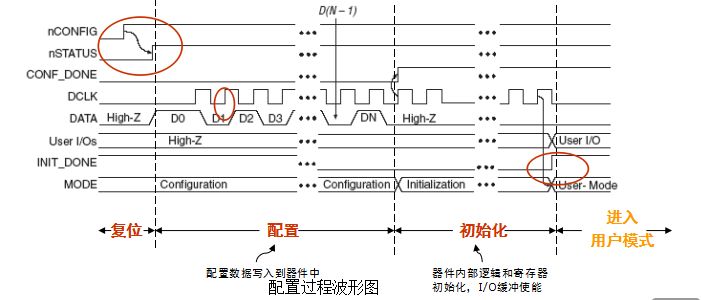

。使用BITSTREAM.CONFIG.EXTMASTERCCLK_EN屬性在Vivado中設(shè)置ExMasterCclk_en選項(xiàng) 三、FPGA加載時(shí)序 上電時(shí)序圖 上電時(shí)序圖 上電配置流程 其配置過(guò)程分解為8個(gè)步驟。 1、上電 7

2021-01-15 16:43:43

cyclone fpga jtag突然不能下載程序,測(cè)量了一下電壓,發(fā)現(xiàn)上電后 ,nstatus管教一直是低電平,其他供電正常 ,這是為什么呢?求幫忙解答,謝謝了

2016-09-27 20:40:03

學(xué)習(xí)的時(shí)候了解到FPGA的多路供電要求一定的上電斷電順序,目前在搞Altera的Cyclone IV系列的FPGA,主要有內(nèi)部邏輯供電VCCINT,PLL供電VCCD_PLL,IO口供電VCCIO等

2017-05-18 22:36:29

為什么有不同的上電時(shí)序

2023-11-02 08:13:09

如果要求輸出是vdd=3.3v,我是不是可以這樣設(shè)計(jì)上電順序:首先設(shè)置Vgg=-2V,再VCtrl=1V,再Vdd=3.3V,然后調(diào)節(jié)Vgg,使Igg=140mA,那么它們之間的上電時(shí)序是如何控制的。

2023-11-22 07:14:57

1.同樣的板子,用過(guò)好多塊,都沒(méi)有問(wèn)題,就這塊無(wú)法加載,應(yīng)該不是PCB設(shè)計(jì)問(wèn)題。2.我設(shè)計(jì)的是主串加載模式(Master Serial)。硬件上將FPGA的M2~M0直接接到GND上。3.上電以后

2015-08-15 09:20:26

次的加載失敗。為定位此問(wèn)題,花費(fèi)了一個(gè)多月,先后投入多位專(zhuān)家,最終確定問(wèn)題的根源是“上電的時(shí)序問(wèn)題”,特為此給大家分享。二、XILINX的上電啟動(dòng)流程 FPGA上電啟動(dòng)包含三大流程,分別是Setup

2022-02-24 09:37:51

1.問(wèn)下aurix的TC397的上電時(shí)序要求是怎樣的呢?

2.有看視頻說(shuō)TC3XX系列沒(méi)有上電時(shí)序的要求,但是在Errata手冊(cè)里看到,又有VDDM和VDD上電時(shí)間要求,否則會(huì)導(dǎo)致lock,能幫忙確認(rèn)下AURIX TC397系列的上電時(shí)序要求嗎?

2024-06-04 09:39:55

為確保芯片能可靠的工作,應(yīng)用處理器的上下電通常都要遵循一定時(shí)序, 本文以i.MX6UL應(yīng)用處理器為例,設(shè)計(jì)中就必須要滿(mǎn)足芯片手冊(cè)的上電時(shí)序、掉電時(shí)序,否則在產(chǎn)品使用時(shí)可能會(huì)出現(xiàn)以下情況,第一,上電

2019-10-18 07:53:02

需要將FPGA程序通過(guò)I2C或者RS232加載到FPGA內(nèi)部,然后通過(guò)FPGA存儲(chǔ)到SPI FLASH中,再次上電后從SPI FLASH加載。 這個(gè)過(guò)程中,有以下幾個(gè)問(wèn)題:1.怎樣將.v文件轉(zhuǎn)換成

2016-04-29 14:46:21

按照TAS5711的datasheet中的上電時(shí)序進(jìn)行上電,芯片正常工作,但是無(wú)法編輯寄存器,是時(shí)序有問(wèn)題嗎?

我是按照這個(gè)上電時(shí)序來(lái)上電的:AVDD/DVDD上電(3.3V),上電之前A_SEL

2024-10-22 06:58:25

如何用EEPROM對(duì)大容量FPGA芯片數(shù)據(jù)實(shí)現(xiàn)串行加載?如何設(shè)計(jì)并-串轉(zhuǎn)換時(shí)序?

2021-04-29 07:13:12

各位前輩,FPGA采用并行加載方式,現(xiàn)CPLD外掛一片F(xiàn)LASH,要求用CPLD控制加載時(shí)序,從FLASH讀取代碼,送入FPGA,應(yīng)該怎么用CPLD控制加載時(shí)序,程序應(yīng)該怎么寫(xiě),有可以參考的資料嗎,謝謝各位了!

2013-02-21 12:07:34

模擬時(shí)序控制器IC。它能控制和監(jiān)視四個(gè)電壓域。電壓的上電和關(guān)斷是通過(guò)控制相應(yīng)電壓轉(zhuǎn)換器上的使能(開(kāi)/關(guān))引腳進(jìn)行的。電壓轉(zhuǎn)換器的開(kāi)啟時(shí)間可以利用小電容產(chǎn)生的時(shí)間延遲來(lái)調(diào)整。各輸出電壓通過(guò)相應(yīng)的監(jiān)控引腳

2021-04-12 07:00:00

有一個(gè)項(xiàng)目中用到OPA192這個(gè)放大器,有兩個(gè)問(wèn)題:

1.V+是+12V供電的,V-是-12V供電的,想問(wèn)下+12V和-12V這兩個(gè)電有沒(méi)有什么必須的上電時(shí)序需要控制?

2.還有就是我的項(xiàng)目

2024-07-29 08:30:16

現(xiàn)在的FPGA還嚴(yán)格要求上電時(shí)序嗎?想請(qǐng)教一下大家

2017-09-26 15:39:07

引言 電源時(shí)序控制是微控制器、FPGA、DSP、 ADC和其他需要多個(gè)電壓軌供電的器件所必需的一項(xiàng)功能。這些應(yīng)用通常需要在數(shù)字I/O軌上電前對(duì)內(nèi)核和模擬模塊上電,但有些設(shè)計(jì)可能需要采用其他序列

2019-07-03 08:15:19

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行

2019-07-18 08:10:11

請(qǐng)問(wèn)fx3有上電時(shí)序要求嗎

2025-05-09 07:29:38

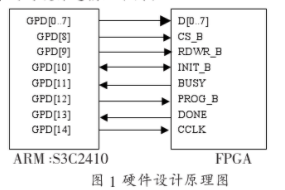

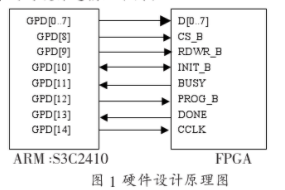

基于ARM+FPGA的可重構(gòu)控制器設(shè)計(jì)及其在加載系統(tǒng)中的應(yīng)用:文章提出了一種基于ARM+FPGA結(jié)構(gòu)的可重構(gòu)控制囂的設(shè)計(jì)方法.并采用此方法開(kāi)發(fā)了用于加載系統(tǒng)的2通道電液伺服控制器

2010-03-02 12:03:21 29

29 如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

當(dāng)FPGA設(shè)計(jì)面臨到高級(jí)接口的設(shè)計(jì)問(wèn)題時(shí),EMA的TimingDesigner可以簡(jiǎn)化這些設(shè)計(jì)問(wèn)題,并提供對(duì)幾乎所有接口的預(yù)先精確控制。從簡(jiǎn)單

2009-04-15 14:19:31 947

947

介紹了一種基于SRAM技術(shù)的FPGA可編程邏輯器件的編程方法,能在系統(tǒng)復(fù)位或上電時(shí)自動(dòng)對(duì)器件編程。有效地解決了基于SRAM的FPGA器件掉電易失性問(wèn)題,針對(duì)當(dāng)前系統(tǒng)規(guī)模的日益增大,本文提出了一種用單片機(jī)對(duì)多片FPGA自動(dòng)加載配置的解決方案.

2011-03-15 16:41:22 21

21 介紹了采用STA (靜態(tài)時(shí)序分析)對(duì)FPGA (現(xiàn)場(chǎng)可編程門(mén)陣列)設(shè)計(jì)進(jìn)行時(shí)序驗(yàn)證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時(shí)序約束。針對(duì)時(shí)序不滿(mǎn)足的情況,提出了幾種常用的促進(jìn) 時(shí)序收斂的方

2011-05-27 08:58:50 70

70 根據(jù)FPGA芯片加載時(shí)序分析,本文提出了采用通過(guò)市面上常見(jiàn)的Flash ROM芯片替代專(zhuān)用PROM的方式,通過(guò)DSP的外部高速總線(xiàn)進(jìn)行FPGA加載;既節(jié)約了系統(tǒng)成本,也能達(dá)到FPGA上電迅速加載的目的

2011-08-16 16:26:14 2130

2130

3 FPGA設(shè)計(jì)流程 完整的FPGA 設(shè)計(jì)流程包括邏輯電路設(shè)計(jì)輸入、功能仿真、綜合及時(shí)序分析、實(shí)現(xiàn)、加載配置、調(diào)試。FPGA 配置就是將特定的應(yīng)用程序設(shè)計(jì)按FPGA設(shè)計(jì)流程轉(zhuǎn)化為數(shù)據(jù)位流加載

2013-01-16 11:52:22 16

16 當(dāng)你的FPGA設(shè)計(jì)不能滿(mǎn)足時(shí)序要求時(shí),原因也許并不明顯。解決方案不僅僅依賴(lài)于使用FPGA的實(shí)現(xiàn)工具來(lái)優(yōu)化設(shè)計(jì)從而滿(mǎn)足時(shí)序要求,也需要設(shè)計(jì)者具有明確目標(biāo)和診斷/隔離時(shí)序問(wèn)題的能力。

2014-08-15 14:22:10 1476

1476 FPGA時(shí)序約束方法很好地資料,兩大主流的時(shí)序約束都講了!

2015-12-14 14:21:25 19

19 Power on Sequence:主板上的供電,從最開(kāi)始的電壓適配器電壓輸入,到最后CPU供電的產(chǎn)生,都有嚴(yán)格的開(kāi)啟順序控制,這個(gè)先后順序,就是上電時(shí)序。

2016-09-01 15:44:10 0

0 主板開(kāi)機(jī)原理與上電時(shí)序圖

2016-12-17 21:30:39 0

0 基于時(shí)序路徑的FPGA時(shí)序分析技術(shù)研究_周珊

2017-01-03 17:41:58 2

2 如何有效地管理FPGA設(shè)計(jì)中的時(shí)序問(wèn)題

2017-01-14 12:49:02 14

14 Xilinx FPGA編程技巧常用時(shí)序約束介紹,具體的跟隨小編一起來(lái)了解一下。

2018-07-14 07:18:00 5223

5223

fpga時(shí)序收斂

2017-03-01 13:13:34 23

23 一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來(lái)越重要的作用。毋庸置疑,時(shí)序約束的最終目的是實(shí)現(xiàn)時(shí)序收斂。時(shí)序收斂作為

2017-11-17 07:54:36 2967

2967

現(xiàn)有的工具和技術(shù)可幫助您有效地實(shí)現(xiàn)時(shí)序性能目標(biāo)。當(dāng)您的FPGA 設(shè)計(jì)無(wú)法滿(mǎn)足時(shí)序性能目標(biāo)時(shí),其原因可能并不明顯。解決方案不僅取決于FPGA 實(shí)現(xiàn)工具為滿(mǎn)足時(shí)序要求而優(yōu)化設(shè)計(jì)的能力,還取決于設(shè)計(jì)人員指定前方目標(biāo),診斷并隔離下游時(shí)序問(wèn)題的能力。

2017-11-18 04:32:34 3842

3842 時(shí)序以及各階段I/O 管腳狀態(tài),說(shuō)明了FPGA上電配置對(duì)電路功能的嚴(yán)重影響,最后針對(duì)不同功能需求的FPGA外圍電路提出了有效的設(shè)計(jì)建議。

2017-11-22 07:18:34 8500

8500

由上電時(shí)序可知,VDD_SOC_IN上電時(shí)序要遲于VDD_HIGH_IN,因此在電路設(shè)計(jì)中,可使用VDD_HIGH_IN電源芯片的控制信號(hào)使能VDD_SOC_IN的電源,如下圖所示為使用VDD_HIGH_IN供電芯片的PG信號(hào)使能VDD_SOC_IN供電芯片的使能管腳。

2018-04-28 09:57:02 22709

22709

FPGA設(shè)計(jì)一個(gè)很重要的設(shè)計(jì)是時(shí)序設(shè)計(jì),而時(shí)序設(shè)計(jì)的實(shí)質(zhì)就是滿(mǎn)足每一個(gè)觸發(fā)器的建立(Setup)/保持(Hold)時(shí)間的要求。

2018-06-05 01:43:00 4865

4865

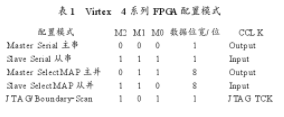

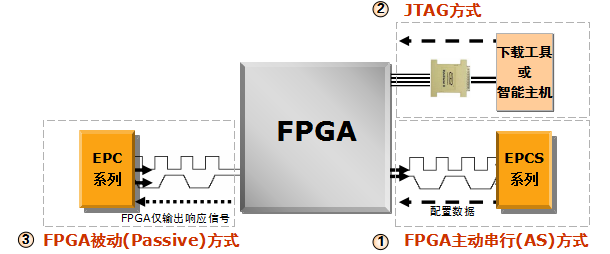

FPGA 的配置數(shù)據(jù)通常存放在系統(tǒng)中的存儲(chǔ)器件中,上電后控制器讀取存儲(chǔ)器中的bit 文件并加載到FPGA 中,配置方式有JTAG、從并、從串、主從4 種,不同廠家叫法不同,但實(shí)現(xiàn)方式基本都是一樣的。

2018-10-30 08:58:00 9336

9336

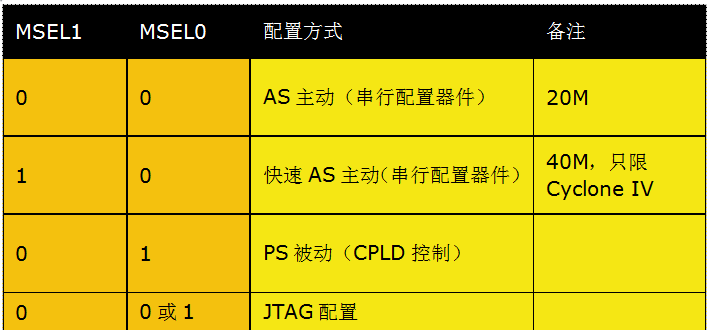

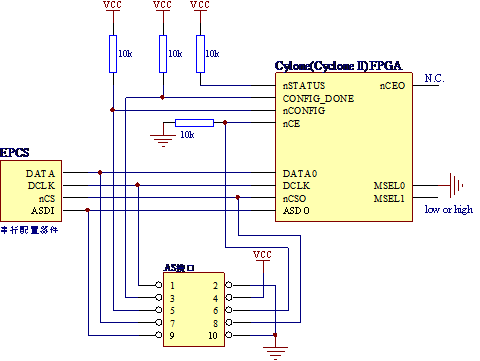

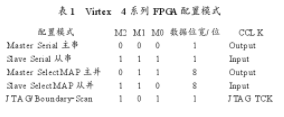

FPGA有多種配置/加載方式。粗略可以分為主動(dòng)和被動(dòng)兩種。主動(dòng)加載是指由FPGA控制配置流程,被動(dòng)加載是指FPGA僅僅被動(dòng)接收配置數(shù)據(jù)。

2018-10-05 10:12:00 19146

19146 可編程的雙重優(yōu)點(diǎn),被廣泛應(yīng)用于通信領(lǐng)域中。FPGA在上電后,需要加載配置文件對(duì)內(nèi)部各功能模塊進(jìn)行初始化,而配置文件加載的效率直接影響系統(tǒng)的初始化時(shí)間。因此如何設(shè)計(jì)一種高效的FPGA加載方案,是通信系統(tǒng)設(shè)計(jì)中的一個(gè)重要環(huán)節(jié)。

2019-02-19 14:49:08 2849

2849

加載系統(tǒng)。該系統(tǒng)通過(guò)USB芯片將PC中的配置文件傳送給CPLD,CPLD再將其寫(xiě)入FLASH芯片,F(xiàn)LASH芯片可以長(zhǎng)久地存儲(chǔ)配置文件。這樣FPGA每次上電后CPLD將FLASH中的配置文件讀出來(lái)配置

2019-02-20 15:36:23 3797

3797

在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過(guò)程被稱(chēng)為程序加載。多數(shù)情況下,從外部專(zhuān)用的 讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且 FPGA要加載的程序可以

2019-03-22 16:20:14 1470

1470 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之FPGA設(shè)計(jì)中時(shí)序邏輯設(shè)計(jì)要點(diǎn)的詳細(xì)資料說(shuō)明免費(fèi)下載。

2019-03-27 10:56:04 20

20 小梅哥FPGAA進(jìn)階教程

2019-08-30 06:04:00 2357

2357

常見(jiàn)的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),還有通用的串行 SPI FLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

2020-04-06 10:33:00 5132

5132

FPGA是基于SRAM編程的,編程信息在系統(tǒng)掉電時(shí)會(huì)丟失,每次上電時(shí),都需要從器件外部的FLASH或EEPROM中存儲(chǔ)的編程數(shù)據(jù)重現(xiàn)寫(xiě)入內(nèi)部的SRAM中。FPGA在線(xiàn)加載需要有CPU的幫助,并且在加載前CPU已經(jīng)啟動(dòng)并工作。FPGA的加載模式主要有以下幾種:

2020-04-07 08:00:00 16

16 FPGA在系統(tǒng)上電時(shí),需要從外部載入所要運(yùn)行的程序,此過(guò)程被稱(chēng)為程序加載。多數(shù)情況下,FPGA從外部專(zhuān)用的 EPROM讀入程序。這種方式速度慢,而且只能加載固定的程序。顯然,當(dāng)系統(tǒng)需要容量大而且

2020-08-13 17:16:46 2922

2922

一:供電電源時(shí)序 EMMC 的供電有兩種模式,且分兩路工作,有 VCC 和 VccQ。在規(guī)范上,上電時(shí)序是有要求的,如下圖所示。 EMMC 上電時(shí)序 開(kāi)始上電時(shí),VCC 或 VccQ 可以第一個(gè)傾斜

2020-10-30 21:29:17 3909

3909 時(shí)序分析結(jié)果,并根據(jù)設(shè)計(jì)者的修復(fù)使設(shè)計(jì)完全滿(mǎn)足時(shí)序約束的要求。本章包括以下幾個(gè)部分: 1.1 靜態(tài)時(shí)序分析簡(jiǎn)介 1.2 FPGA 設(shè)計(jì)流程 1.3 TimeQuest 的使用 1.4 常用時(shí)序約束 1.5 時(shí)序分析的基本概念

2020-11-11 08:00:00 67

67 EMMC 的供電有兩種模式,且分兩路工作,有 VCC 和 VccQ。在規(guī)范上,上電時(shí)序是有要求的,如下圖所示。

2020-12-02 23:13:00 23

23 本文檔的主要內(nèi)容詳細(xì)介紹的是英業(yè)達(dá)上電時(shí)序的詳細(xì)資料說(shuō)明。

2020-12-04 08:00:00 63

63 本文檔的主要內(nèi)容詳細(xì)介紹的是電源模塊的上下電時(shí)序介紹免費(fèi)下載。

2020-12-10 08:00:00 12

12 本文檔的主要內(nèi)容詳細(xì)介紹的是華為FPGA硬件的靜態(tài)時(shí)序分析與邏輯設(shè)計(jì)包括了:靜態(tài)時(shí)序分析一概念與流程,靜態(tài)時(shí)序分析一時(shí)序路徑,靜態(tài)時(shí)序分析一分析工具

2020-12-21 17:10:54 22

22 在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束利序例外約束才能實(shí)現(xiàn)PCB板級(jí)的時(shí)序收斂。因此,FPGA時(shí)序約束中IO口時(shí)序約束也是重點(diǎn)。只有約東正確才能在高速情況下保證FPGA和外部器件通信正確

2021-01-13 17:13:00 11

11 AN-1080: 利用簡(jiǎn)單時(shí)序控制器ADM108x進(jìn)行上電和關(guān)斷時(shí)序控制

2021-03-21 00:41:43 6

6 基于SRAM結(jié)構(gòu)的FPGA容量大,可重復(fù)操作,應(yīng)用相當(dāng)廣泛;但其結(jié)構(gòu)類(lèi)似于SRAM,掉電后數(shù)據(jù)丟失,因此每次上電時(shí)都需重新加載。

2021-03-26 13:52:58 6318

6318

典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性存儲(chǔ)器中的配置比特流,配置所需的時(shí)鐘信號(hào)( 稱(chēng)為CCLK) 由FPGA內(nèi)部產(chǎn)生,且FPGA控制整個(gè)配置過(guò)程。

2022-03-14 14:02:50 2381

2381 上一篇《FPGA時(shí)序約束分享01_約束四大步驟》一文中,介紹了時(shí)序約束的四大步驟。

2022-03-18 10:29:28 2166

2166

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話(huà)題,也是FPGA開(kāi)發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來(lái),先介紹時(shí)序分析中的一些基本概念。

2022-03-18 11:07:13 3922

3922 本文章探討一下FPGA的時(shí)序input delay約束,本文章內(nèi)容,來(lái)源于明德?lián)P時(shí)序約束專(zhuān)題課視頻。

2022-07-25 15:37:07 3757

3757

目前,大多數(shù)FPGA芯片是基于 SRAM 的結(jié)構(gòu)的, 而 SRAM 單元中的數(shù)據(jù)掉電就會(huì)丟失,因此系統(tǒng)上電后,必須要由配置電路將正確的配置數(shù)據(jù)加載到 SRAM 中,此后 FPGA 才能夠正常的運(yùn)行。

2022-08-15 09:13:31 2967

2967 Class-D 功放TAS5731M 上電時(shí)序分析

2022-10-31 08:24:00 1

1 時(shí)序約束是我們對(duì)FPGA設(shè)計(jì)的要求和期望,例如,我們希望FPGA設(shè)計(jì)可以工作在多快的時(shí)鐘頻率下等等。因此,在時(shí)序分析工具開(kāi)始對(duì)我們的FPGA設(shè)計(jì)進(jìn)行時(shí)序分析前,我們必須為其提供相關(guān)的時(shí)序約束信息。在

2022-12-28 15:18:38 5209

5209 總結(jié)Xilinx? FPGA 的上電模式可以分為以下4類(lèi)型: 主模式 從模式 JTAG模式(調(diào)試模式) 系統(tǒng)模式(多片配置模式) 1、主模式 典型的主模式都是加載片外非易失( 斷電不丟數(shù)據(jù)) 性

2023-03-29 14:50:06 2111

2111 FPGA開(kāi)發(fā)過(guò)程中,離不開(kāi)時(shí)序約束,那么時(shí)序約束是什么?簡(jiǎn)單點(diǎn)說(shuō),FPGA芯片中的邏輯電路,從輸入到輸出所需要的時(shí)間,這個(gè)時(shí)間必須在設(shè)定的時(shí)鐘周期內(nèi)完成,更詳細(xì)一點(diǎn),即需要滿(mǎn)足建立和保持時(shí)間。

2023-06-26 14:42:10 1252

1252

在不帶內(nèi)置ARM核的AMD FPGA產(chǎn)品系列中,FPGA的程序加載方式并沒(méi)有發(fā)生大的變化

2023-07-07 14:14:58 4513

4513

FPGA高級(jí)時(shí)序綜合教程

2023-08-07 16:07:55 9

9 筆記本上電時(shí)序

2024-01-09 10:26:36 1

1 AMD FPGA在配置了適當(dāng)?shù)膯?dòng)模式后,上電即會(huì)按該模式去加載配置文件。以7系列FPGA為例,假設(shè)設(shè)置模式引腳M[2:0]=3’b001,上電后FPGA會(huì)以Master SPI方式嘗試從FLASH加載配置文件,其與工程是否含有MicroBlaze IP無(wú)關(guān)。

2024-04-25 12:49:14 1406

1406

電子發(fā)燒友網(wǎng)站提供《FPGA電源時(shí)序控制.pdf》資料免費(fèi)下載

2024-08-26 09:25:41 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論