扇出型晶圓級封裝(FOWLP)的概念最早由德國英飛凌提出,自2016 年以來,業(yè)界一直致力于FOWLP 技術(shù)的發(fā)展。

2026-01-04 14:40:30 188

188

在半導(dǎo)體制造的精密流程中,晶圓清洗機(jī)濕法制程設(shè)備扮演著至關(guān)重要的角色。以下是關(guān)于晶圓清洗機(jī)濕法制程設(shè)備的介紹:分類單片清洗機(jī):采用兆聲波、高壓噴淋或旋轉(zhuǎn)刷洗技術(shù),針對納米級顆粒物進(jìn)行去除。批量式清洗

2025-12-29 13:27:19 204

204

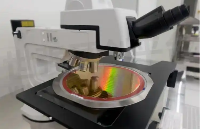

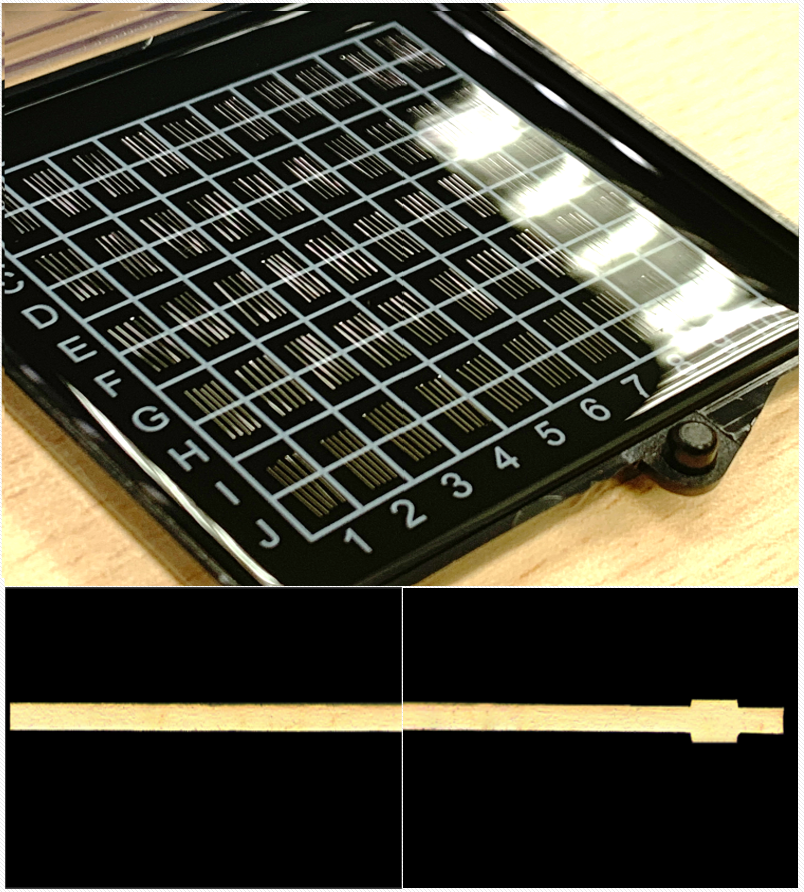

在集成電路檢測中,高光學(xué)對比度的晶圓級階高標(biāo)準(zhǔn)對提升自動圖像識別的精度至關(guān)重要。傳統(tǒng)基于單層Si-SiO?薄膜的階高標(biāo)準(zhǔn)在低臺階高度下對比度不足,通常需借助金屬鍍層增強(qiáng)信號,但這會引入污染風(fēng)險

2025-12-24 18:04:07 102

102

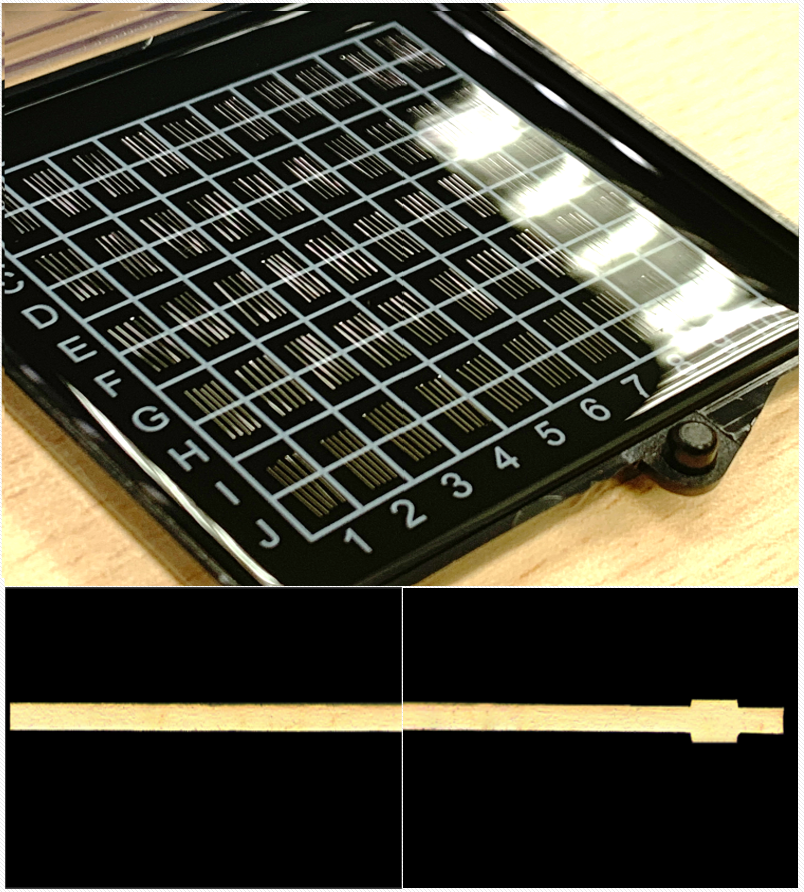

GT-BGA-2002高性能BGA測試插座GT-BGA-2002是Ironwood Electronics 的GT Elastomer系列的高性能BGA測試插座,專為高頻高速信號測試設(shè)計,兼容多數(shù)

2025-12-18 10:00:10

追蹤芯片一致性與可靠性,為后續(xù)迭代提供數(shù)據(jù)支撐。

其性能直接影響三大核心指標(biāo):芯片測試的精準(zhǔn)度(決定良率篩選有效性)、測試效率(影響量產(chǎn)周期與成本)、信號保真度(保障高算力芯片的性能還原度)。

沒有

2025-12-15 15:09:09

ATE的探針卡,在晶圓測試中被稱為定海神針,有著不可替代價值,那么在設(shè)計和生產(chǎn)階段有哪些注意事項,點開今天的文章,有你需要的答案。

2025-12-15 15:07:36 228

228

體檢",確保每一片晶圓在出廠前都能達(dá)到嚴(yán)苛的性能標(biāo)準(zhǔn)。無論是普通消費者還是行業(yè)從業(yè)者,了解WAT的運作原理和意義,都能幫助我們更深入地認(rèn)識半導(dǎo)體技術(shù)的精密與復(fù)雜。

2025-12-10 15:08:43 433

433

太陽能IV曲線測試儀:光伏檢測的“性能探針”柏峰【BF-CV1500】太陽能IV曲線測試儀是專為光伏組件及系統(tǒng)性能檢測設(shè)計的專業(yè)設(shè)備,以“精準(zhǔn)采集+深度分析”為核心優(yōu)勢,

2025-11-06 13:29:03 255

255

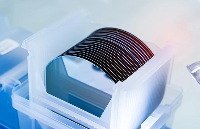

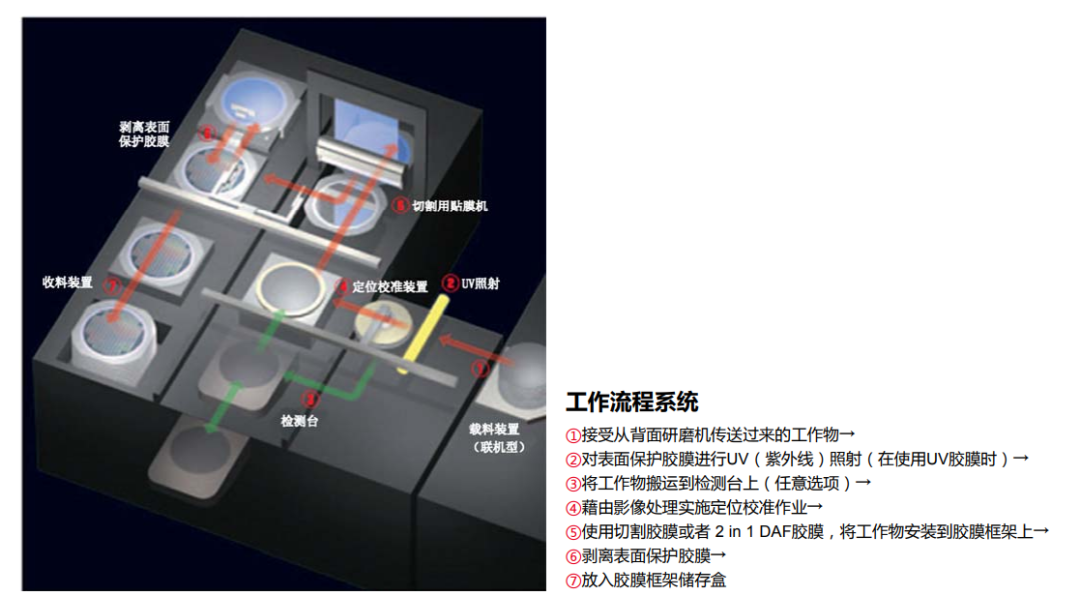

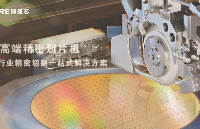

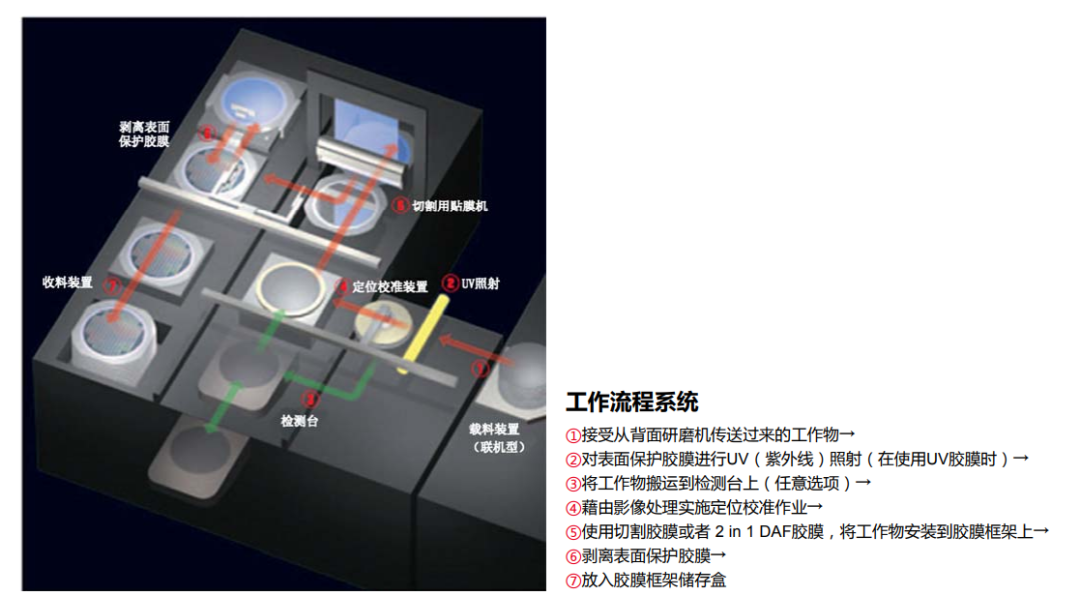

在半導(dǎo)體制造的精密工藝鏈條中,芯片切割作為晶圓級封裝的關(guān)鍵環(huán)節(jié),其技術(shù)演進(jìn)與設(shè)備精度直接關(guān)系到芯片良率與性能表現(xiàn);框架內(nèi)貼片作為連接芯片與封裝體的核心環(huán)節(jié),其技術(shù)實施直接影響器件的電性能、熱管理及可靠性表現(xiàn)。

2025-11-05 17:06:29 1725

1725

在功率半導(dǎo)體封裝領(lǐng)域,晶圓級芯片規(guī)模封裝技術(shù)正引領(lǐng)著分立功率器件向更高集成度、更低損耗及更優(yōu)熱性能方向演進(jìn)。

2025-10-21 17:24:13 3874

3874

晶圓清洗設(shè)備作為半導(dǎo)體制造的核心工藝裝備,其技術(shù)特點融合了精密控制、高效清潔與智能化管理,具體體現(xiàn)在以下幾個方面: 多模式復(fù)合清洗技術(shù) 物理與化學(xué)協(xié)同作用:結(jié)合超聲波空化效應(yīng)(剝離微小顆粒和有機(jī)物

2025-10-14 11:50:19 230

230 晶圓級封裝(WLP)與多芯片組件(MCM)作為先進(jìn)封裝的“雙引擎”,前者在晶圓未切割時即完成再布線與凸點制作,以“封裝即制造”實現(xiàn)芯片級尺寸、70 μm以下超細(xì)間距與電熱性能躍升;后者把多顆已驗證

2025-10-13 10:36:41 2090

2090

一、引言

在高端半導(dǎo)體測試設(shè)備領(lǐng)域,東京精密 TOKYO SEIMITSU Vega 系列的 Vega Planet 探針臺以其全方位的性能表現(xiàn),成為復(fù)雜測試場景的核心設(shè)備。海翔科技提供的二手

2025-10-11 11:50:25 328

328

中,高精度的 CP 測試設(shè)備能夠確保每一片晶圓上合格芯片的比例最大化。

2.**成品測試(FT 測試)**

芯片封裝完成后,需要對成品芯片進(jìn)行全面的功能和性能測試。半導(dǎo)體測試設(shè)備可以模擬芯片在實際

2025-10-10 10:35:17

WD4000晶圓三維顯微形貌測量設(shè)備通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷。自動測量

2025-09-17 16:05:18

近日,廣立微自主研發(fā)的首臺專為碳化硅(SiC)和氮化鎵(GaN)功率器件設(shè)計的晶圓級老化測試系統(tǒng)——WLBI B5260M正式出廠。該設(shè)備的成功推出,將為產(chǎn)業(yè)鏈提供了高效、精準(zhǔn)的晶圓級可靠性篩選解決方案,助推化合物半導(dǎo)體產(chǎn)業(yè)的成熟與發(fā)展。

2025-09-17 11:51:44 747

747

UF2000 探針臺,依托品牌的技術(shù)積淀,通過專業(yè)的現(xiàn)場驗機(jī)測試服務(wù),為客戶提供設(shè)備性能的全面評估,助力客戶在成本與可靠性之間找到平衡,滿足多樣化的半導(dǎo)體測試需求。 二、UF2000 探針臺性能特征 UF2000 探針臺主要面向 Φ200mm 及以下規(guī)格晶圓的測試需求,在消費電子芯片、功率器

2025-09-13 11:05:32 1130

1130 在半導(dǎo)體產(chǎn)業(yè)飛速發(fā)展的今天,芯片質(zhì)量的把控至關(guān)重要。浙江季豐電子科技有限公司嘉善晶圓測試廠(以下簡稱嘉善晶圓測試廠)憑借在 CP(Chip Probing,晶圓測試)測試領(lǐng)域的深厚技術(shù)積累與創(chuàng)新突破,持續(xù)為全球芯片產(chǎn)業(yè)鏈提供堅實可靠的品質(zhì)保障,深受客戶的信任與好評。

2025-09-05 11:15:03 1032

1032 本文主要講述什么是晶圓級芯粒封裝中的分立式功率器件。 分立式功率器件作為電源管理系統(tǒng)的核心單元,涵蓋二極管、MOSFET、IGBT等關(guān)鍵產(chǎn)品,在個人計算機(jī)、服務(wù)器等終端設(shè)備功率密度需求攀升的當(dāng)下,其封裝技術(shù)正加速向晶圓級芯片級封裝演進(jìn)——通過縮小體積、提升集成效率,滿足設(shè)備小型化與高性能的雙重需求。

2025-09-05 09:45:40 3096

3096

MEMS晶圓級電鍍是一種在微機(jī)電系統(tǒng)制造過程中,整個硅晶圓表面通過電化學(xué)方法選擇性沉積金屬微結(jié)構(gòu)的關(guān)鍵工藝。該技術(shù)的核心在于其晶圓級和圖形化特性:它能在同一時間對晶圓上的成千上萬個器件結(jié)構(gòu)進(jìn)行批量加工,極大地提高了生產(chǎn)效率和一致性,是實現(xiàn)MEMS器件低成本、批量化制造的核心技術(shù)之一。

2025-09-01 16:07:28 2075

2075

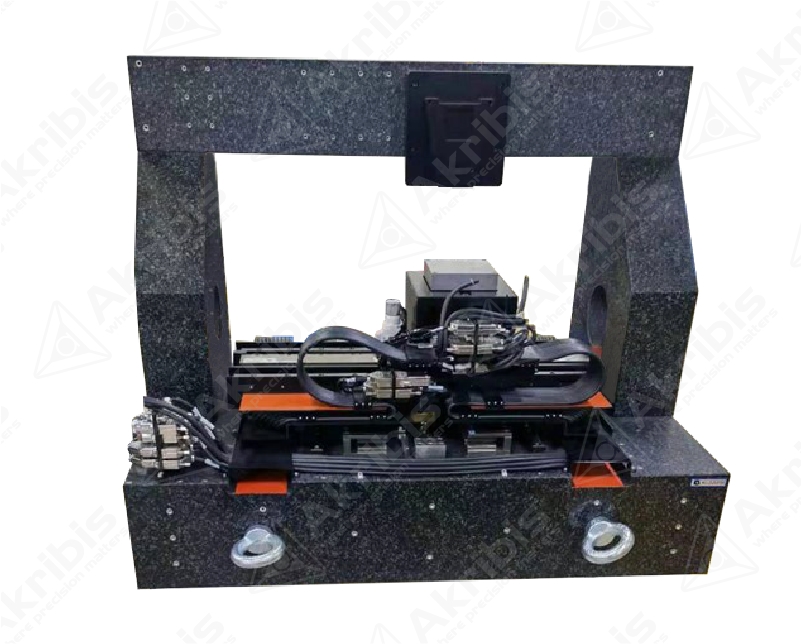

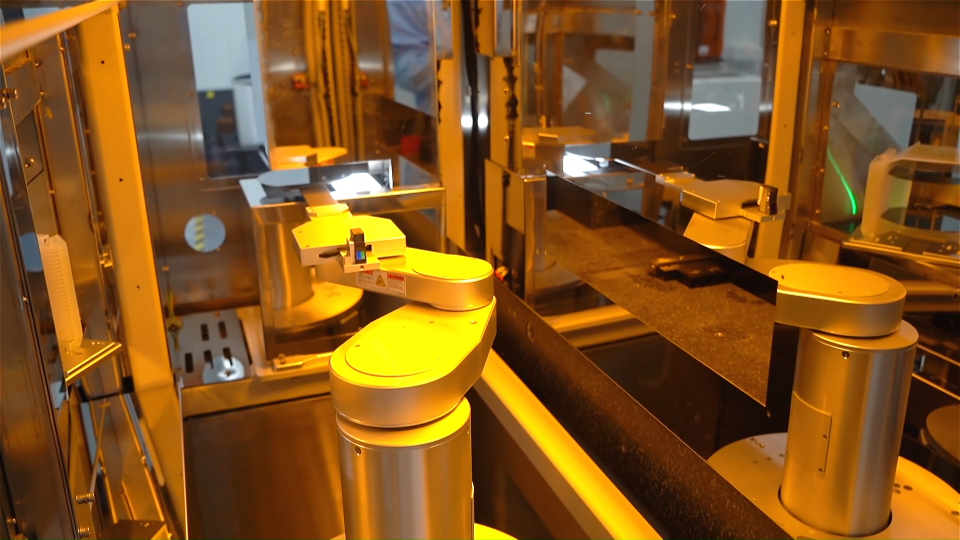

效率的雙重要求。通過持續(xù)的技術(shù)研發(fā),為行業(yè)提供了性能穩(wěn)定的晶圓處理前端模塊解決方案。 在直線電機(jī)平臺領(lǐng)域已經(jīng)擁有十三年的專業(yè)經(jīng)驗,在晶圓處理前端模塊方面積累了豐富的技術(shù)知識。公司服務(wù)過的客戶超過五百家,這些

2025-08-26 09:57:53 391

391 晶棒需要經(jīng)過一系列加工,才能形成符合半導(dǎo)體制造要求的硅襯底,即晶圓。加工的基本流程為:滾磨、切斷、切片、硅片退火、倒角、研磨、拋光,以及清洗與包裝等。

2025-08-12 10:43:43 4164

4164

我將從超薄晶圓研磨面臨的挑戰(zhàn)出發(fā),點明聚氨酯墊性能對晶圓 TTV 的關(guān)鍵影響,引出研究意義。接著分析聚氨酯墊性能與 TTV 的關(guān)聯(lián),闡述性能優(yōu)化方向及 TTV 保障技術(shù),最后通過實驗初步驗證效果。

超薄晶圓(

2025-08-06 11:32:54 585

585

摘要

本論文圍繞超薄晶圓切割工藝,探討切割液性能智能調(diào)控系統(tǒng)與晶圓 TTV 預(yù)測模型的協(xié)同構(gòu)建,闡述兩者協(xié)同在保障晶圓切割質(zhì)量、提升 TTV 均勻性方面的重要意義,為半導(dǎo)體制造領(lǐng)域的工藝優(yōu)化提供理論

2025-07-31 10:27:48 372

372

軟件于一體,為功率半導(dǎo)體行業(yè)提供全方位的測試解決方案。 核心優(yōu)勢與設(shè)計亮點多場景廣泛適配:探針臺支持主流6英寸、8英寸、12英寸晶圓滿足不同研發(fā)與生產(chǎn)階段需求。 高溫卡盤兼容Banana、BNC

2025-07-29 16:21:17

WD4000晶圓THK測量設(shè)備兼容不同材質(zhì)不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數(shù)據(jù)更準(zhǔn)確。它通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW

2025-07-28 15:38:44

場景:分析連接到PCIe總線的NVMe存儲設(shè)備的性能,評估高速數(shù)據(jù)讀寫時的表現(xiàn)。

應(yīng)用價值:優(yōu)化存儲子系統(tǒng),確保其滿足大規(guī)模數(shù)據(jù)集訓(xùn)練任務(wù)的需求。

企業(yè)級存儲陣列

測試場景:測試多盤位NVMe SSD

2025-07-25 14:09:01

切割工藝參數(shù)以實現(xiàn)晶圓 TTV 均勻性有效控制,為晶圓切割工藝改進(jìn)提供新的思路與方法。

一、引言

在半導(dǎo)體晶圓切割工藝中,晶圓 TTV 均勻性是影響芯片制造質(zhì)量與良

2025-07-25 10:12:24 420

420

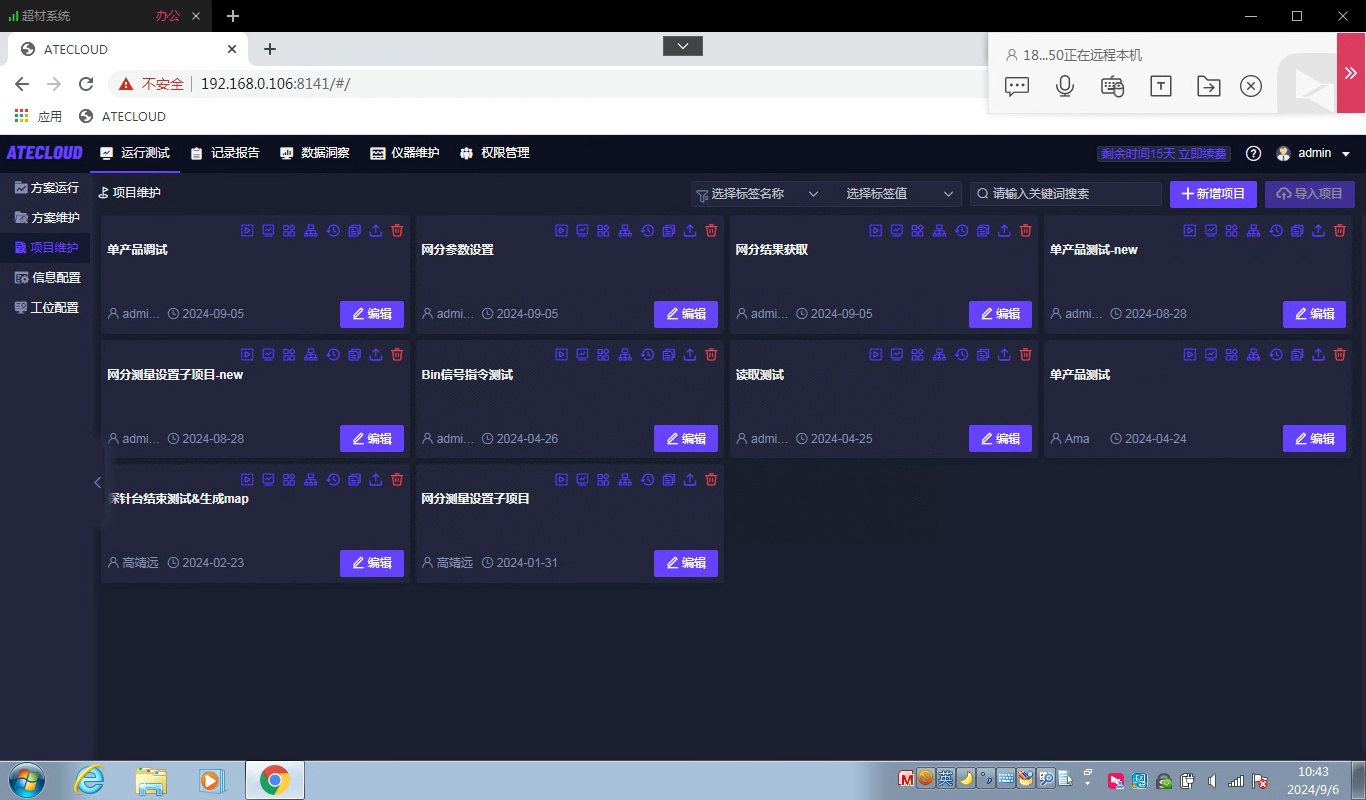

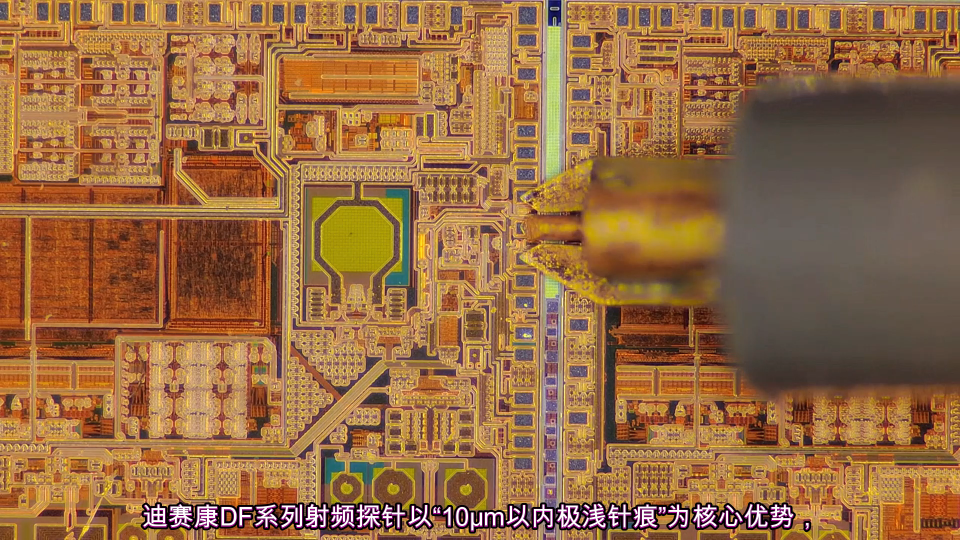

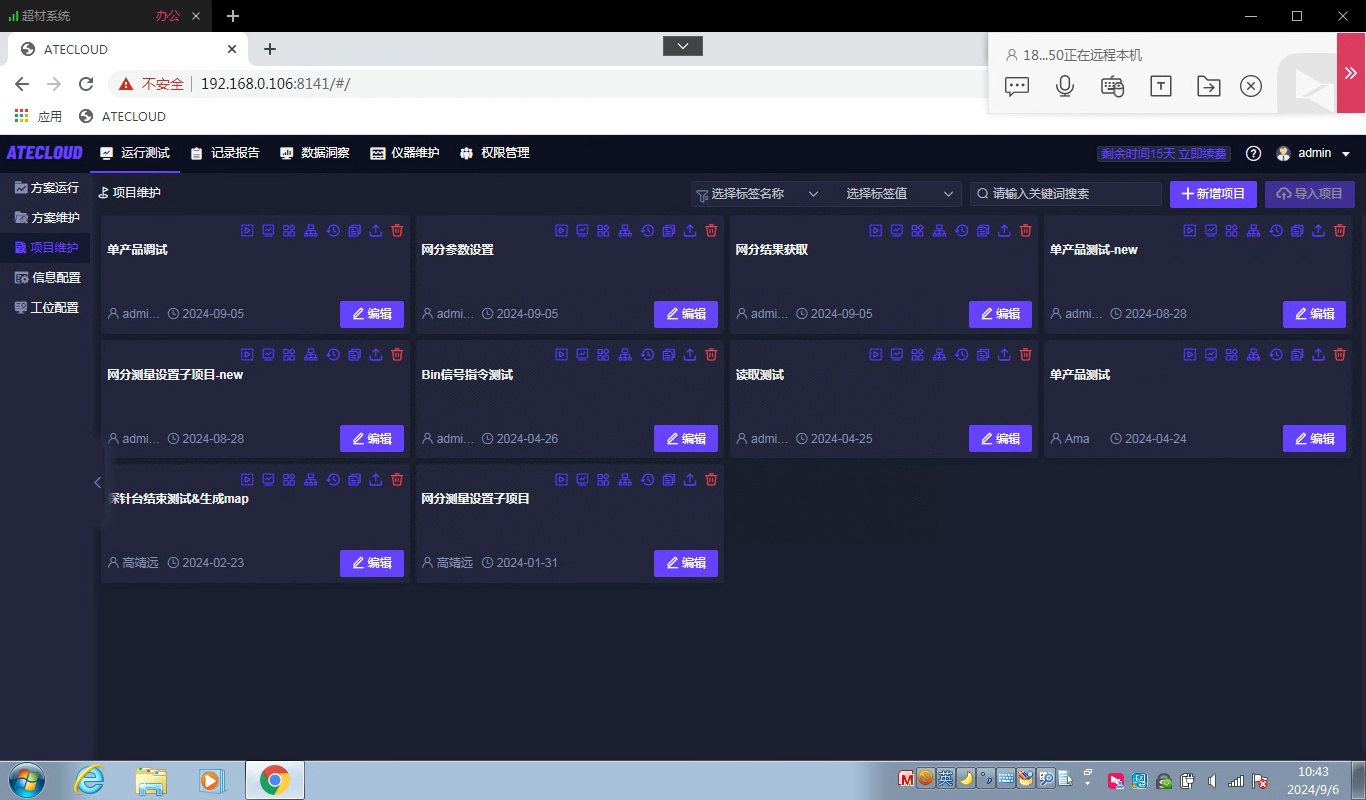

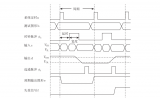

要求也逐漸提升,如何準(zhǔn)確快速的完成射頻芯片的批量測試則成了眾多射頻芯片企業(yè)面臨的難題。 ? 射頻晶圓芯片測試 為了滿足射頻芯片的大批量快速測試,采用自動化平臺配合矢量網(wǎng)絡(luò)分析和探針臺是大多數(shù)射頻芯片企業(yè)的選擇

2025-07-24 11:24:54 542

542

TTV 均勻性提供理論依據(jù)與技術(shù)指導(dǎo)。

一、引言

在晶圓切割工藝中,TTV 厚度均勻性是衡量晶圓質(zhì)量的關(guān)鍵指標(biāo),直接影響芯片制造的良率與性能。切割液作為切割過程中

2025-07-24 10:23:09 500

500

背景介紹: 北京某公司是一家專注于高性能SAW濾波器和雙工器等系列射頻前端芯片的研發(fā)設(shè)計、生產(chǎn)和銷售的企業(yè)。企業(yè)在測試其晶圓芯片產(chǎn)品時,由于原有測試系統(tǒng)無法控制探針臺,導(dǎo)致測試工作難以完成,因此急需

2025-07-23 15:55:14 590

590

晶圓清洗工藝是半導(dǎo)體制造中的關(guān)鍵步驟,用于去除晶圓表面的污染物(如顆粒、有機(jī)物、金屬離子和氧化物),確保后續(xù)工藝(如光刻、沉積、刻蝕)的良率和器件性能。根據(jù)清洗介質(zhì)、工藝原理和設(shè)備類型的不同,晶圓

2025-07-23 14:32:16 1368

1368

晶圓清洗機(jī)中的晶圓夾持是確保晶圓在清洗過程中保持穩(wěn)定、避免污染或損傷的關(guān)鍵環(huán)節(jié)。以下是晶圓夾持的設(shè)計原理、技術(shù)要點及實現(xiàn)方式: 1. 夾持方式分類 根據(jù)晶圓尺寸(如2英寸到12英寸)和工藝需求,夾持

2025-07-23 14:25:43 929

929 半導(dǎo)體器件向更小、更強(qiáng)大且多功能的方向快速演進(jìn),對晶圓測試流程提出了前所未有的要求。隨著先進(jìn)架構(gòu)和新材料重新定義芯片布局與功能,傳統(tǒng)晶圓測試方法已難以跟上發(fā)展步伐。飛針測試技術(shù)的發(fā)展為晶圓探針測試

2025-07-17 17:36:53 705

705

Wafer Acceptance Test (WAT) 是晶圓制造中確保產(chǎn)品質(zhì)量和可靠性的關(guān)鍵步驟。它通過對晶圓上關(guān)鍵參數(shù)的測量和分析,幫助識別工藝中的問題,并為良率提升提供數(shù)據(jù)支持。在芯片項目的量產(chǎn)管理中,WAT是您保持產(chǎn)線穩(wěn)定性和產(chǎn)品質(zhì)量的重要工具。

2025-07-17 11:43:31 2777

2777 錫膏在晶圓級封裝中易遇印刷橋連 空洞、回流焊焊點失控、氧化、設(shè)備精度不足等問題。解決問題需平衡工藝參數(shù),同時設(shè)備也需要做精細(xì)調(diào)準(zhǔn)。

2025-07-03 09:35:00 833

833

晶圓級封裝含扇入型、扇出型、倒裝芯片、TSV 等工藝。錫膏在植球、凸點制作、芯片互連等環(huán)節(jié)關(guān)鍵:扇入 / 扇出型植球用錫膏固定錫球;倒裝芯片用其制作凸點;TSV 堆疊靠其實現(xiàn)垂直連接。應(yīng)用依賴鋼網(wǎng)

2025-07-02 11:53:58 946

946

了解晶圓級封裝如何進(jìn)一步提高芯片的連接密度,為后續(xù)技術(shù)發(fā)展奠定基礎(chǔ)。

2025-06-27 16:51:51 614

614 WD4000全自動晶圓厚度測量設(shè)備兼容不同材質(zhì)不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數(shù)據(jù)更準(zhǔn)確。它采用白光光譜共焦多傳感器和白光干涉顯微測量雙向掃描技術(shù),完成非接觸式掃描并建立表面3D

2025-06-27 11:43:16

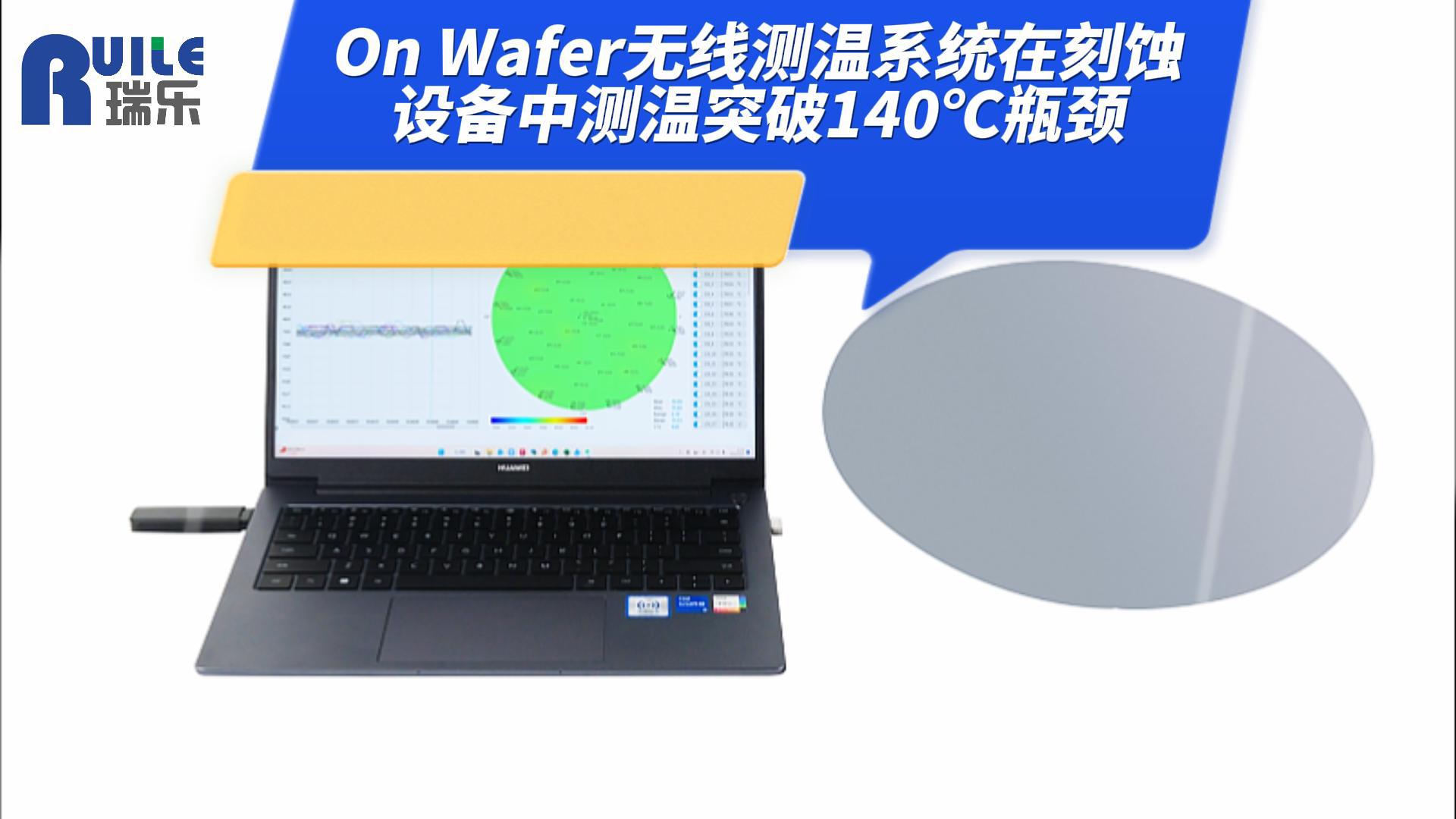

On Wafer WLS無線晶圓測溫系統(tǒng)通過自主研發(fā)的核心技術(shù)將傳感器嵌入晶圓集成,實時監(jiān)控和記錄晶圓在制程過程中的溫度變化數(shù)據(jù),為半導(dǎo)體制造過程提供一種高效可靠的方式來監(jiān)測和優(yōu)化關(guān)鍵

2025-06-27 10:37:30

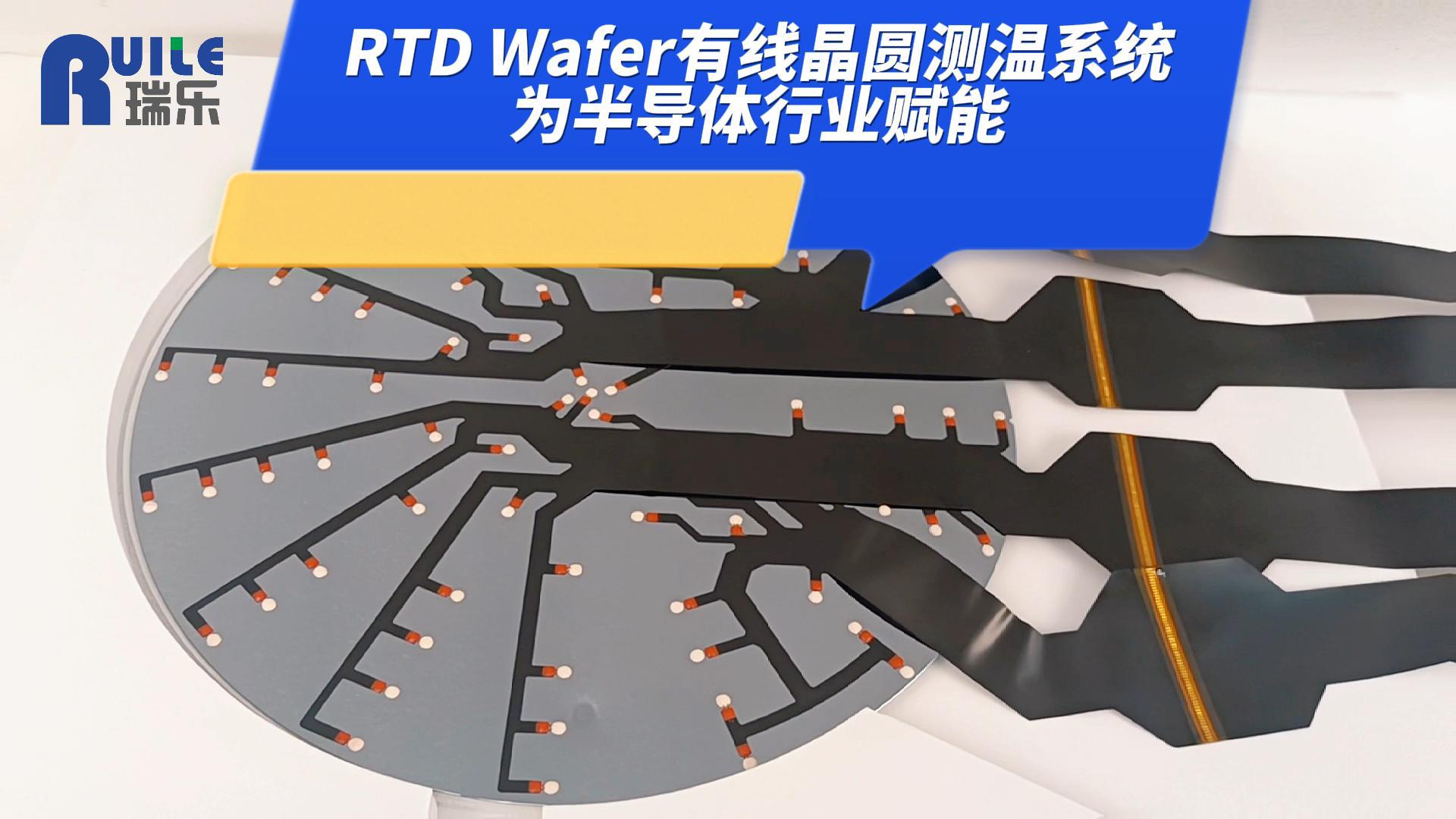

RTD Wafer 晶圓測溫系統(tǒng)利用自主研發(fā)的核心技術(shù)將 RTD 傳感器集成到 晶圓表面,實時監(jiān)控和記錄晶圓在制程過程中的溫度變化數(shù)據(jù),為半導(dǎo)體 制造過程提供一種高效可靠的方式來監(jiān)測和優(yōu)化關(guān)鍵的工藝

2025-06-27 10:12:00

探針卡, WAT,PCM測試

2025-06-26 19:23:17 673

673 在半導(dǎo)體制造的精密流程中,晶圓載具清洗機(jī)是確保芯片良率與性能的關(guān)鍵設(shè)備。它專門用于清潔承載晶圓的載具(如載具、花籃、托盤等),避免污染物通過載具轉(zhuǎn)移至晶圓表面,從而保障芯片制造的潔凈度與穩(wěn)定性。本文

2025-06-25 10:47:33

在半導(dǎo)體制造的精密流程中,晶圓濕法清洗設(shè)備扮演著至關(guān)重要的角色。它不僅是芯片生產(chǎn)的基礎(chǔ)工序,更是決定良率、效率和成本的核心環(huán)節(jié)。本文將從技術(shù)原理、設(shè)備分類、行業(yè)應(yīng)用到未來趨勢,全面解析這一關(guān)鍵設(shè)備

2025-06-25 10:26:37

WD4000晶圓厚度測量設(shè)備兼容不同材質(zhì)不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數(shù)據(jù)更準(zhǔn)確。它通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW

2025-06-18 15:40:06

摘要:本文探討晶圓邊緣 TTV 測量在半導(dǎo)體制造中的重要意義,分析其對芯片制造工藝、器件性能和生產(chǎn)良品率的影響,同時研究測量方法、測量設(shè)備精度等因素對測量結(jié)果的作用,為提升半導(dǎo)體制造質(zhì)量提供理論依據(jù)

2025-06-14 09:42:58 552

552

晶圓經(jīng)切割后,表面常附著大量由聚合物、光致抗蝕劑及蝕刻雜質(zhì)等組成的顆粒物,這些物質(zhì)會對后續(xù)工序中芯片的幾何特征與電性能產(chǎn)生不良影響。顆粒物與晶圓表面的粘附力主要來自范德華力的物理吸附作用,因此業(yè)界主要采用物理或化學(xué)方法對顆粒物進(jìn)行底切處理,通過逐步減小其與晶圓表面的接觸面積,最終實現(xiàn)脫附。

2025-06-13 09:57:01 865

865 硅晶圓揀選測試作為半導(dǎo)體制造流程中的關(guān)鍵質(zhì)量控制環(huán)節(jié),旨在通過系統(tǒng)性電氣檢測篩選出功能異常的芯片。該測試體系主要包含直流特性分析、輸出驅(qū)動能力驗證和功能邏輯驗證三大核心模塊,各模塊依據(jù)器件物理特性與功能需求設(shè)計了差異化的檢測方法與技術(shù)路徑。

2025-06-11 09:49:44 1214

1214

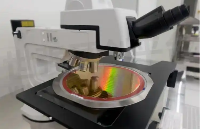

晶圓檢測是指在晶圓制造完成后,對晶圓進(jìn)行的一系列物理和電學(xué)性能的測試與分析,以確保其質(zhì)量和性能符合設(shè)計要求。這一過程是半導(dǎo)體制造中的關(guān)鍵環(huán)節(jié),直接影響后續(xù)封裝和芯片的良品率。 隨著圖形化和幾何結(jié)構(gòu)

2025-06-06 17:15:28 718

718

晶圓級扇出封裝(FO-WLP)通過環(huán)氧樹脂模塑料(EMC)擴(kuò)展芯片有效面積,突破了扇入型封裝的I/O密度限制,但其技術(shù)復(fù)雜度呈指數(shù)級增長。

2025-06-05 16:25:57 2146

2146

在微電子行業(yè)飛速發(fā)展的背景下,封裝技術(shù)已成為連接芯片創(chuàng)新與系統(tǒng)應(yīng)用的核心紐帶。其核心價值不僅體現(xiàn)于物理防護(hù)與電氣/光學(xué)互聯(lián)等基礎(chǔ)功能,更在于應(yīng)對多元化市場需求的適應(yīng)性突破,本文著力介紹晶圓級扇入封裝,分述如下。

2025-06-03 18:22:20 1055

1055

貼膜是指將一片經(jīng)過減薄處理的晶圓(Wafer)固定在一層特殊的膠膜上,這層膜通常為藍(lán)色,業(yè)內(nèi)常稱為“ 藍(lán)膜 ”。貼膜的目的是為后續(xù)的晶圓切割(劃片)工藝做準(zhǔn)備。

2025-06-03 18:20:59 1180

1180

WD4000無圖晶圓粗糙度測量設(shè)備通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷。自動測量Wafer

2025-06-03 15:52:50

體現(xiàn)在技術(shù)壁壘和產(chǎn)業(yè)核心地位,更在于推動全球電子設(shè)備小型化、智能化及新興領(lǐng)域(如AI、自動駕駛)的發(fā)展。晶圓技術(shù)的持續(xù)創(chuàng)新,是半導(dǎo)體行業(yè)進(jìn)步的核心驅(qū)動力之一。

2025-05-28 16:12:46

摘要:本文針對激光退火后晶圓總厚度偏差(TTV)變化的問題,深入探討從工藝參數(shù)優(yōu)化、設(shè)備改進(jìn)、晶圓預(yù)處理以及檢測反饋機(jī)制等方面,提出一系列有效管控 TTV 變化的方法,為提升激光退火后晶圓質(zhì)量提供

2025-05-23 09:42:45 583

583

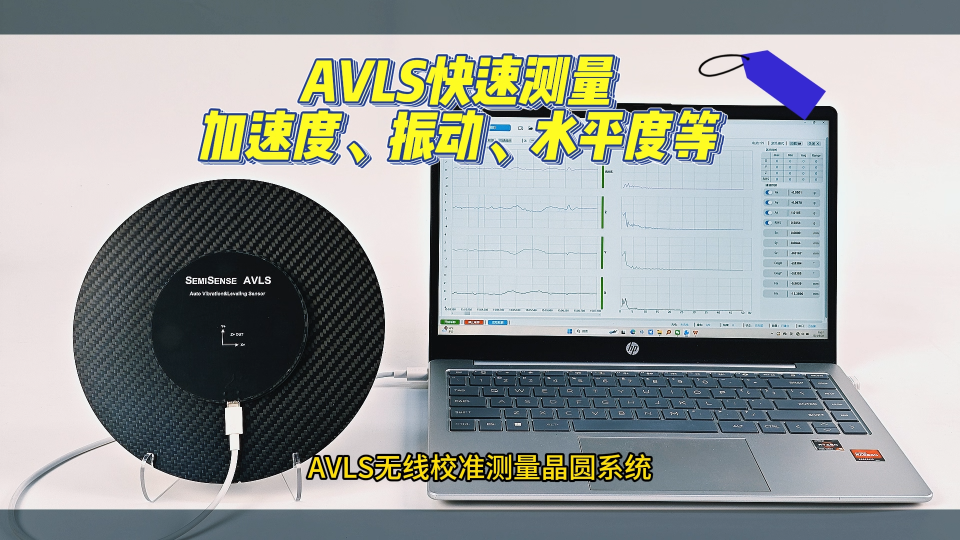

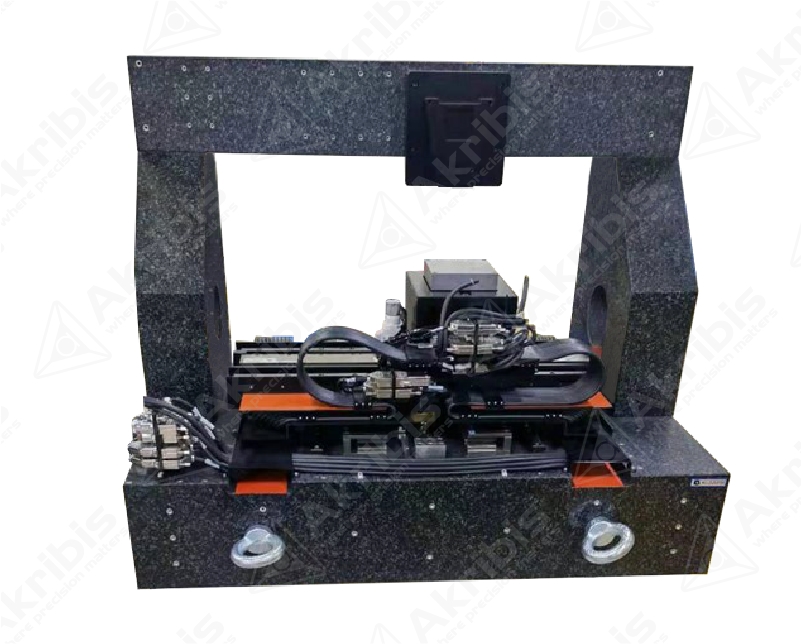

在半導(dǎo)體制造領(lǐng)域,晶圓拋光作為關(guān)鍵工序,對設(shè)備穩(wěn)定性要求近乎苛刻。哪怕極其細(xì)微的振動,都可能對晶圓表面質(zhì)量產(chǎn)生嚴(yán)重影響,進(jìn)而左右芯片制造的成敗。以下為您呈現(xiàn)一個防震基座在半導(dǎo)體晶圓制造設(shè)備拋光機(jī)上的經(jīng)典應(yīng)用案例。

2025-05-22 14:58:29 554

554

摘要:本文聚焦于降低晶圓 TTV(總厚度偏差)的磨片加工方法,通過對磨片設(shè)備、工藝參數(shù)的優(yōu)化以及研磨拋光流程的改進(jìn),有效控制晶圓 TTV 值,提升晶圓質(zhì)量,為半導(dǎo)體制造提供實用技術(shù)參考。 關(guān)鍵詞:晶

2025-05-20 17:51:39 1028

1028

前言在半導(dǎo)體制造的前段制程中,晶圓需要具備足夠的厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性。盡管芯片功能層的制備僅涉及晶圓表面幾微米范圍,但完整厚度的晶圓更有利于保障復(fù)雜工藝的順利進(jìn)行,直至芯片前制程

2025-05-16 16:58:44 1110

1110

我們看下一個先進(jìn)封裝的關(guān)鍵概念——晶圓級封裝(Wafer Level Package,WLP)。

2025-05-14 10:32:30 1533

1533

WD4000晶圓制造翹曲度厚度測量設(shè)備通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷。自動測量

2025-05-13 16:05:20

在半導(dǎo)體制造流程中,晶圓在前端工藝階段需保持一定厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性,避免彎曲變形,并為芯片制造工藝提供操作便利。不同規(guī)格晶圓的原始厚度存在差異:4英寸晶圓厚度約為520微米,6

2025-05-09 13:55:51 1976

1976 探針和探針卡是半導(dǎo)體制造中晶圓測試環(huán)節(jié)的關(guān)鍵組件,可以篩選不良芯片,避免無效封裝、降低成本,是半導(dǎo)體測試的“質(zhì)量守門員”,技術(shù)壁壘高且國產(chǎn)化空間大。國內(nèi)企業(yè)在中低端市場已實現(xiàn)突破,但高端領(lǐng)域仍需攻克

2025-05-08 18:14:21 1309

1309

圓片級封裝(WLP),也稱為晶圓級封裝,是一種直接在晶圓上完成大部分或全部封裝測試程序,再進(jìn)行切割制成單顆組件的先進(jìn)封裝技術(shù) 。WLP自2000年左右問世以來,已逐漸成為半導(dǎo)體封裝領(lǐng)域的主流技術(shù),深刻改變了傳統(tǒng)封裝的流程與模式。

2025-05-08 15:09:36 2068

2068

在電子設(shè)備領(lǐng)域,晶振如同精密儀器的“心臟起搏器”,其性能直接決定設(shè)備運行的穩(wěn)定性與可靠性。由于不同應(yīng)用場景對晶振的性能要求差異巨大,行業(yè)內(nèi)將晶振劃分為民用級、工業(yè)級、車規(guī)級和軍工級,各等級有著嚴(yán)格

2025-05-08 11:08:40 832

832 隨著半導(dǎo)體工藝復(fù)雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術(shù)通過直接在未封裝晶圓上施加加速應(yīng)力,實現(xiàn)快速

2025-05-07 20:34:21

在半導(dǎo)體制造流程中,晶圓揀選測試(Wafer Sort)堪稱芯片從“原材料”到“成品”的關(guān)鍵質(zhì)控節(jié)點。作為集成電路制造中承上啟下的核心環(huán)節(jié),其通過精密的電學(xué)測試,為每一顆芯片頒發(fā)“質(zhì)量合格證”,同時為工藝優(yōu)化提供數(shù)據(jù)支撐。

2025-04-30 15:48:27 5746

5746

中圖儀器WD4000系列半導(dǎo)體晶圓表面形貌量測設(shè)備通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度,TTV,BOW、WARP、在高效測量測同時有效防止晶圓產(chǎn)生劃痕缺陷

2025-04-21 10:49:55

本文介紹了半導(dǎo)體集成電路制造中的晶圓制備、晶圓制造和晶圓測試三個關(guān)鍵環(huán)節(jié)。

2025-04-15 17:14:37 2159

2159

(ESD)和電氣特性的測量能力,為提高晶圓良品率提供了強(qiáng)大的支持。本文將探討如何通過使用Keithley 6485靜電計的技術(shù)和方法來提升晶圓良品率。 1. 靜電計的應(yīng)用背景 靜電計是用于測量微弱電流、靜電和電壓的儀器,廣泛應(yīng)用于晶圓制造和測試過程中

2025-04-15 14:49:13 516

516

晶圓芯片存放于氮氣柜時需遵循嚴(yán)格標(biāo)準(zhǔn),涵蓋氮氣純度、露點溫度、柜體潔凈度、溫濕度控制及氣流均勻性等方面。那么下面就來具體給大家揭曉一個行業(yè)內(nèi)默認(rèn)的標(biāo)準(zhǔn)吧! 晶圓芯片存放氮氣柜標(biāo)準(zhǔn)一覽 氮氣純度 常規(guī)

2025-04-07 14:01:47 1551

1551 隨著半導(dǎo)體工藝復(fù)雜度提升,可靠性要求與測試成本及時間之間的矛盾日益凸顯。晶圓級可靠性(Wafer Level Reliability, WLR)技術(shù)通過直接在未封裝晶圓上施加加速應(yīng)力,實現(xiàn)快速、低成本的可靠性評估,成為工藝開發(fā)的關(guān)鍵工具。

2025-03-26 09:50:16 1548

1548

BW-4022A

晶體管直流參數(shù)測試系統(tǒng)

一、產(chǎn)品介紹:

BW-4022A 晶體管直流參數(shù)測試機(jī)是新一代針對半導(dǎo)體器件測試系統(tǒng),經(jīng)過我公司多次升級與產(chǎn)品迭代,目前測試性能、精度、測試范圍及產(chǎn)品穩(wěn)定度

2025-03-20 11:30:20

方案提供服務(wù)的領(lǐng)導(dǎo)者EV集團(tuán)(EV Group,簡稱EVG)今日發(fā)布下一代GEMINI?自動化晶圓鍵合系統(tǒng),專為300毫米(12英寸)晶圓量產(chǎn)設(shè)計。該系統(tǒng)的核心升級為全新開發(fā)的高精度強(qiáng)力鍵合模塊,在滿足全球

2025-03-20 09:07:58 889

889

高精度晶圓劃片機(jī)切割解決方案為實現(xiàn)高精度晶圓切割,需從設(shè)備精度、工藝穩(wěn)定性、智能化控制等多維度優(yōu)化,以下為關(guān)鍵實現(xiàn)路徑及技術(shù)支撐:一、核心精度控制技術(shù)?雙軸協(xié)同與高精度運動系統(tǒng)?雙工位同步切割技術(shù)

2025-03-11 17:27:52 797

797

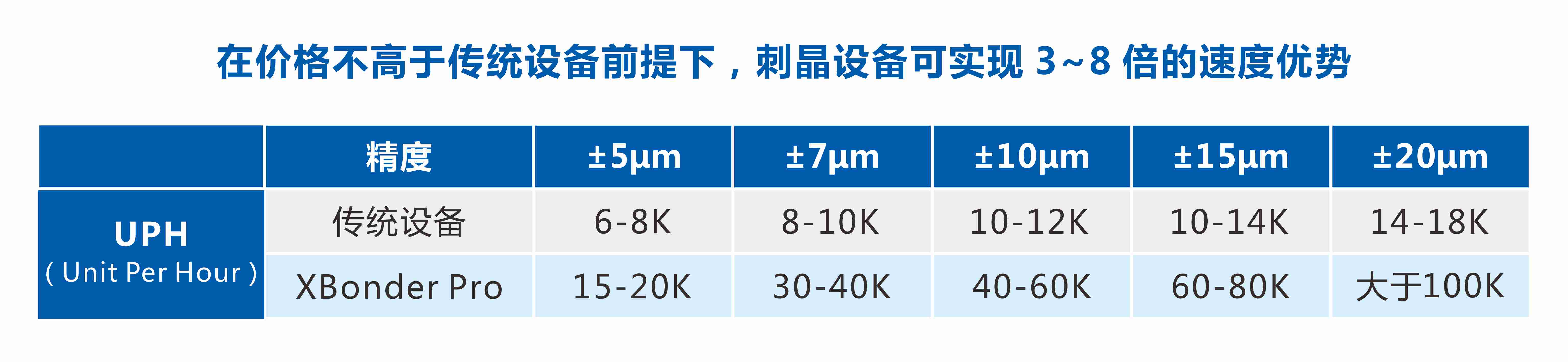

經(jīng)過半年的測試,普萊信智能和某頂級封裝廠就其巨量轉(zhuǎn)移式板級封裝設(shè)備(FOPLP)設(shè)備XBonder Pro達(dá)成戰(zhàn)略合作協(xié)議,這將是巨量轉(zhuǎn)移技術(shù)在IC封裝領(lǐng)域第一次規(guī)模化的應(yīng)用,將掀起晶圓級封裝和板級

2025-03-04 11:28:05 1186

1186

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,晶圓級封裝(WLP)作為先進(jìn)封裝技術(shù)的重要組成部分,正逐漸成為集成電路封裝的主流趨勢。在晶圓級封裝過程中,Bump工藝扮演著至關(guān)重要的角色。Bump,即凸塊,是晶圓級封裝中

2025-03-04 10:52:57 4980

4980

近期,小編接到一位來自半導(dǎo)體行業(yè)的咨詢,對方正在尋找一款適合晶圓焊點推力測試的推拉力測試機(jī)。在半導(dǎo)體制造中,晶圓焊點的可靠性是保障電子設(shè)備性能和使用壽命的核心要素。通過晶圓焊點推力測試,可以精準(zhǔn)評估

2025-02-28 10:32:47 805

805

隨著半導(dǎo)體器件的復(fù)雜性不斷提高,對精確可靠的晶圓測試解決方案的需求也從未像現(xiàn)在這樣高。從5G、物聯(lián)網(wǎng)和人工智能應(yīng)用,到先進(jìn)封裝和高帶寬存儲器(HBM),在晶圓級確保設(shè)備性能和產(chǎn)量是半導(dǎo)體制造過程中的關(guān)鍵步驟。

2025-02-17 13:51:16 1331

1331 1 應(yīng)用 最終用戶是一家為半導(dǎo)體行業(yè)提供創(chuàng)新晶圓制造設(shè)備和服務(wù)的全球供應(yīng)商。設(shè)計團(tuán)隊在設(shè)計一種可應(yīng)用于一系列設(shè)備的新型控制系統(tǒng)時,傾向于使用成熟部件構(gòu)建基于PXI平臺的系統(tǒng)。要求該部件具有卓越的性能

2025-02-17 10:15:09 709

709 Dicing 是指將制造完成的晶圓(Wafer)切割成單個 Die 的工藝步驟,是從晶圓到獨立芯片生產(chǎn)的重要環(huán)節(jié)之一。每個 Die 都是一個功能單元,Dicing 的精準(zhǔn)性直接影響芯片的良率和性能。

2025-02-11 14:28:49 2946

2946 電子發(fā)燒友網(wǎng)站提供《SOT1381-2晶圓級芯片尺寸封裝.pdf》資料免費下載

2025-02-08 17:30:43 0

0 設(shè)計標(biāo)準(zhǔn),從而提升產(chǎn)品的良率和可靠性。作為制造流程中的關(guān)鍵檢測環(huán)節(jié),WAT測試不僅是保障產(chǎn)品質(zhì)量的關(guān)鍵手段,也為提升生產(chǎn)效率提供了重要支撐。此外,WAT測試幫助企業(yè)快速識別工藝缺陷,優(yōu)化制造流程,從而降低生產(chǎn)成本、提高市場競爭力,并帶來顯著的經(jīng)濟(jì)效益

2025-01-23 14:11:44 9862

9862

扇出型晶圓級中介層封裝( FOWLP)以及封裝堆疊(Package-on-Package, PoP)設(shè)計在移動應(yīng)用中具有許多優(yōu)勢,例如低功耗、短信號路徑、小外形尺寸以及多功能的異構(gòu)集成。此外,它還

2025-01-22 14:57:52 4507

4507

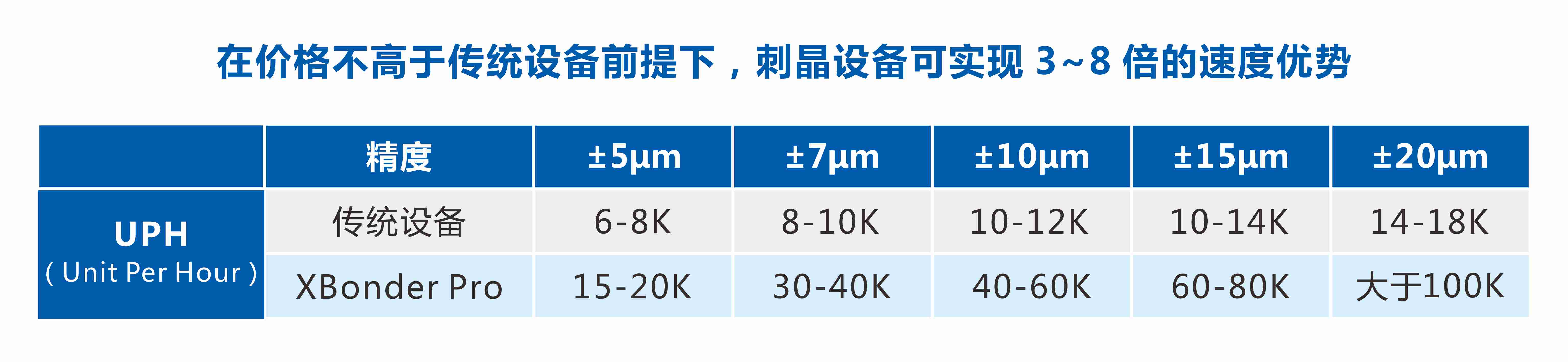

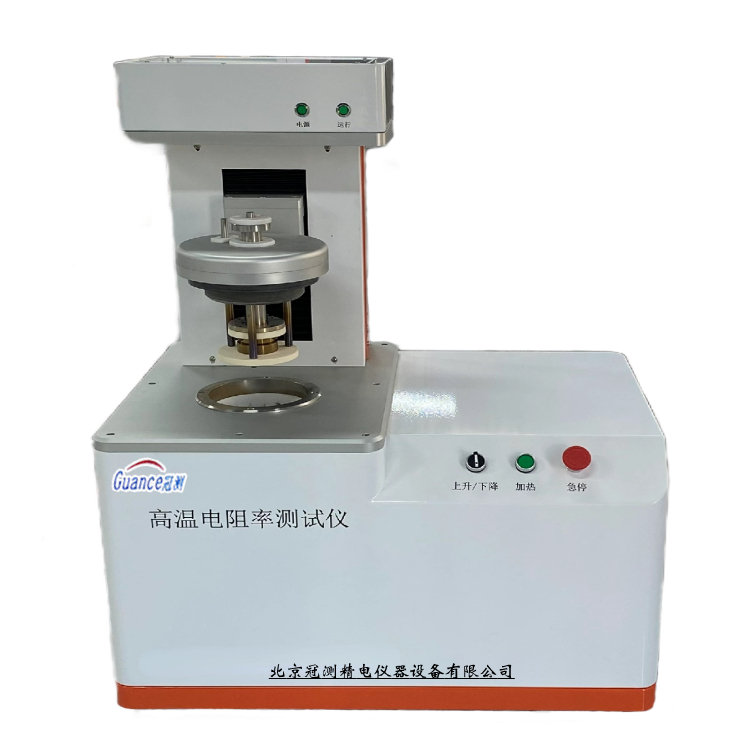

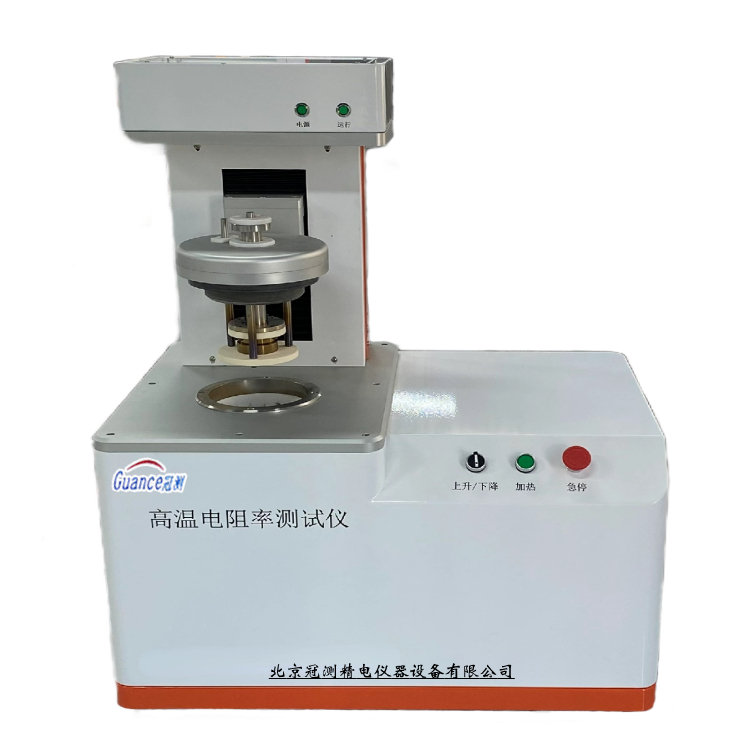

在高溫電阻測試儀的四探針法中,探針的間距對測量結(jié)果確實存在影響,但這一影響可以通過特定的測試方法和儀器設(shè)計來最小化或消除。 探針間距對測量結(jié)果的影響 在經(jīng)典直排四探針法中,要求使用等間距的探針進(jìn)行

2025-01-21 09:16:11 1238

1238

AP-200,中間為晶體管檢測儀IWATSU CS-10105C,右邊為控制用計算機(jī)。三部分組成了一個測試系統(tǒng)。 下圖所示為探針臺,主要對晶圓進(jìn)行電學(xué)檢測,分為載物臺、探卡、絕緣氣體供應(yīng)設(shè)備這幾部分,載物臺用于晶圓的放置,可以兼容4~8寸的晶圓,上面有

2025-01-14 09:29:13 2359

2359

隨著半導(dǎo)體技術(shù)的飛速發(fā)展,晶圓級封裝(Wafer Level Packaging, WLP)作為一種先進(jìn)的封裝技術(shù),正逐漸在集成電路封裝領(lǐng)域占據(jù)主導(dǎo)地位。晶圓級封裝技術(shù)以其高密度、高可靠性、小尺寸

2025-01-07 11:21:59 3190

3190

WD4000半導(dǎo)體晶圓幾何表面形貌檢測設(shè)備兼容不同材質(zhì)不同粗糙度、可測量大翹曲wafer、測量晶圓雙面數(shù)據(jù)更準(zhǔn)確。它通過非接觸測量,將晶圓的三維形貌進(jìn)行重建,強(qiáng)大的測量分析軟件穩(wěn)定計算晶圓厚度

2025-01-06 14:34:08

電子發(fā)燒友App

電子發(fā)燒友App

評論