前言

在半導(dǎo)體制造的前段制程中,晶圓需要具備足夠的厚度,以確保其在流片過程中的結(jié)構(gòu)穩(wěn)定性。盡管芯片功能層的制備僅涉及晶圓表面幾微米范圍,但完整厚度的晶圓更有利于保障復(fù)雜工藝的順利進行,直至芯片前制程完成后,晶圓才會進入封裝環(huán)節(jié)進行減薄處理。

晶圓為什么要減薄

封裝階段對晶圓進行減薄主要基于多重考量。

從劃片工藝角度,較厚晶圓硬度較高,在傳統(tǒng)機械切割時易出現(xiàn)劃片不均、裂片等問題,顯著提升不良率;而減薄后的晶圓硬度降低,能夠?qū)崿F(xiàn)更精準、高效的分離,大幅提升劃片質(zhì)量與效率。

隨著電子設(shè)備向輕薄化方向發(fā)展,封裝厚度已成為關(guān)鍵指標,尤其在芯片堆疊技術(shù)中,晶圓減薄能夠有效降低整體封裝厚度,滿足可穿戴設(shè)備、移動終端等微型電子產(chǎn)品的需求。

同時,晶圓制造過程中背面形成的氧化層會影響芯片鍵合質(zhì)量,減薄工藝可有效去除氧化層,為鍵合提供潔凈、平整的表面,確保電氣連接的可靠性。

此外,減薄能夠縮短芯片工作時的熱量傳導(dǎo)路徑,加速散熱,避免因高溫導(dǎo)致的性能衰退與壽命縮短,提升芯片長期運行的穩(wěn)定性。

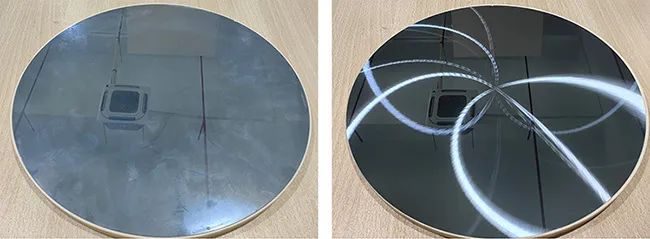

晶圓減薄前后對比

不同封裝對減薄厚度的要求存在差異

引線鍵合(Wire Bond)封裝,典型厚度為100-200微米;

傳統(tǒng)封裝(如QFP、DIP等)對厚度要求相對寬松,通常將晶圓減薄至約300微米;

BGA封裝,減薄范圍在100-200微米,這樣的厚度可以適應(yīng)球柵的布局和高度要求,同時也能保證芯片與基板之間的電氣連接和機械穩(wěn)定性;

CSP封裝,晶圓減薄厚度一般要求在 50 - 100 微米之間。由于 CSP 封裝直接將芯片與基板連接,較薄的晶圓可以減少芯片與基板之間的應(yīng)力,提高封裝的可靠性,同時也有助于降低信號傳輸延遲,滿足小型化和高性能的要求。

先進的疊層封裝中,芯片厚度甚至可薄至30微米以下,以滿足高密度集成需求。

晶圓減薄工藝

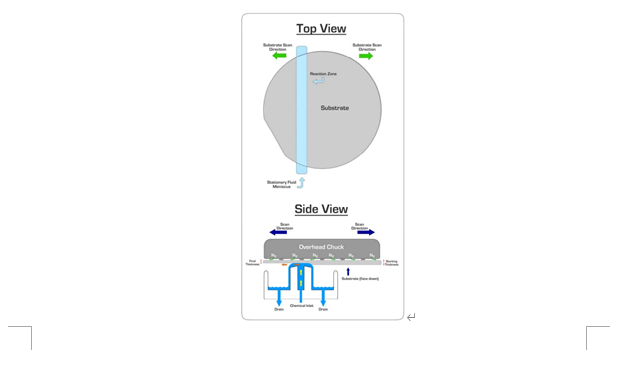

晶圓減薄工藝一般采用機械研磨、化學機械拋光(CMP)等方法。其具體流程涵蓋前期準備、減薄操作(例如粗磨、精磨和拋光)以及后期處理(如清理殘留物、測量平坦度和質(zhì)量檢測)。

減薄砂輪

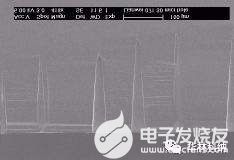

在實際晶圓減薄生產(chǎn)中,多采用組合工藝來確保加工精度與效率。例如,若需將硅片從初始厚度減薄至120μm,可先通過高效的粗磨磨削工藝去除大部分材料,將硅片厚度削減至140μm左右。此時,硅片表面因磨削產(chǎn)生損傷層與殘余應(yīng)力,就需要根據(jù)后續(xù)產(chǎn)品性能要求,選擇一種或多種工藝進行精細處理,實現(xiàn)晶圓減薄的高效化與高質(zhì)量化,并確保后續(xù)劃切工序的順利進行。

晶圓減薄與劃片工藝的融合

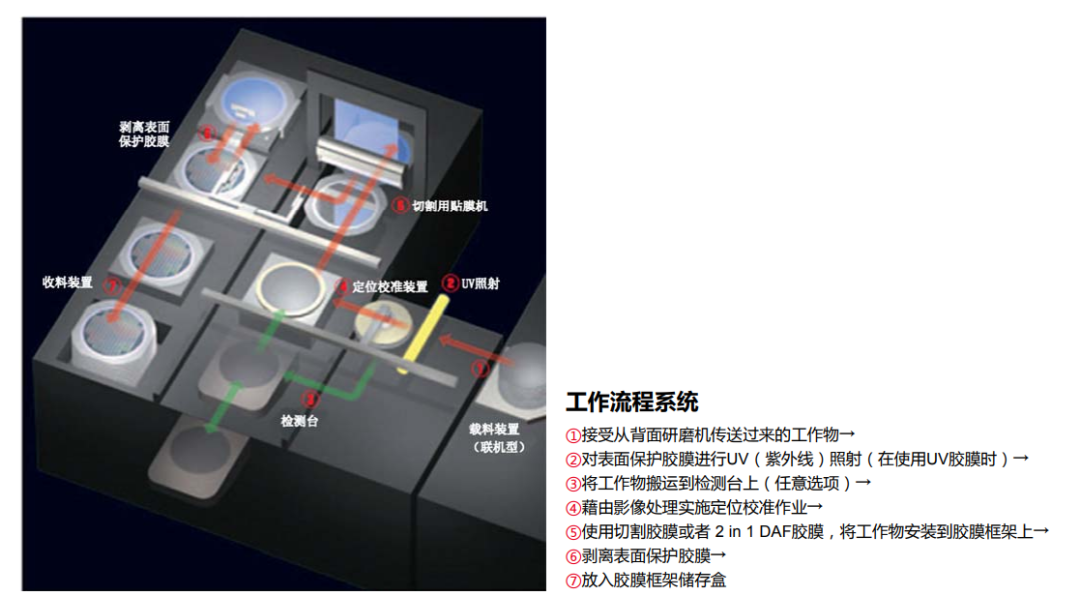

在芯片切割環(huán)節(jié),傳統(tǒng)流程是先在晶圓背面粘貼藍膜并固定于鋼制框架(即晶圓黏片工藝),隨后采用機械切割或激光切割進行分離。

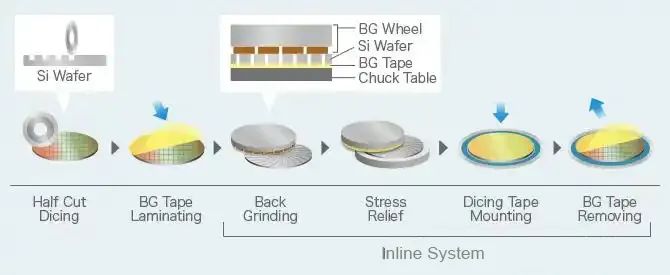

隨著工藝創(chuàng)新,“先劃片后減薄”(DBG)與“減薄劃片”(DBT)技術(shù)應(yīng)運而生。

DBG工藝先在晶圓正面切割出一定深度的切口,再進行背面磨削。

DBG工藝流程

DBT技術(shù)則是預(yù)先形成切割切口,通過磨削減薄后利用ADPE腐蝕去除剩余材料,實現(xiàn)裸芯片自動分離。這兩種方法有效規(guī)避了傳統(tǒng)工藝中減薄導(dǎo)致的硅片翹曲與劃片造成的芯片邊沿損傷問題。

其中,DBT技術(shù)憑借各向同性硅刻蝕劑,既能消除背面研磨損傷,又能修復(fù)芯片微裂與凹槽,大幅提升芯片抗碎裂性能。

關(guān)于粗磨/精磨減薄砂輪以及半切/全切金剛石刀片產(chǎn)品應(yīng)用,歡迎咨詢西斯特科技。

-

晶圓

+關(guān)注

關(guān)注

53文章

5434瀏覽量

132530 -

封裝

+關(guān)注

關(guān)注

128文章

9302瀏覽量

148931 -

半導(dǎo)體制造

+關(guān)注

關(guān)注

8文章

521瀏覽量

26287

發(fā)布評論請先 登錄

宜特晶圓:成功開發(fā)晶圓減薄達1.5mil(38um)技術(shù)

單面晶圓減薄和處理研究報告

用于高密度晶圓互連的微加工晶圓減薄方法

晶圓減薄工藝的主要步驟

晶圓鍵合及后續(xù)工藝流程

減薄對后續(xù)晶圓劃切的影響

減薄對后續(xù)晶圓劃切的影響

評論