?

一、?LMK04821功能介紹

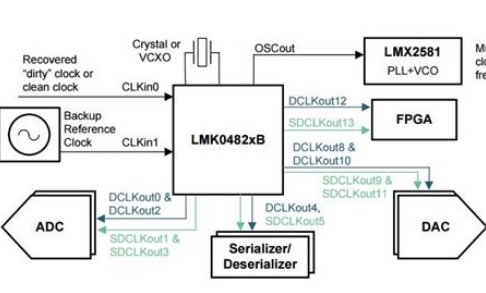

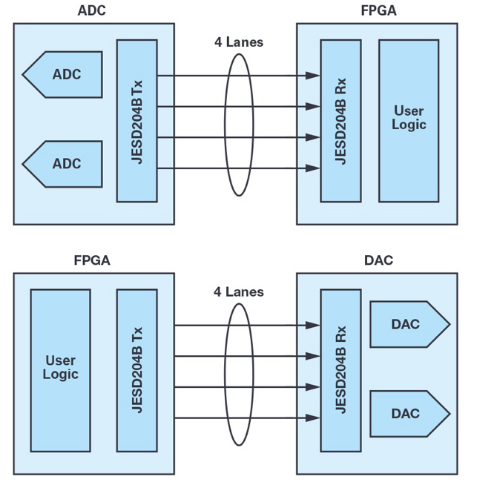

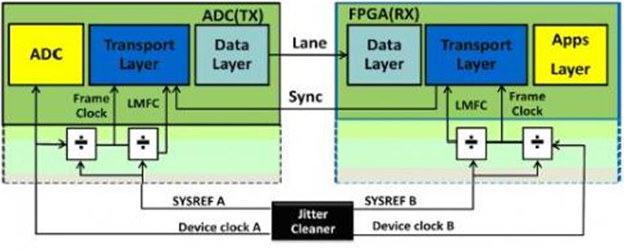

LMK0482X系列是德州儀器推出的高性能時鐘調節芯片系列,該芯片目前有三種,分別為LMK04821、LMK04826以及LMK04828,該系列芯片都支持最新的JESD204B協議。本次調試主要以LMK04821為例,對調試過程中出現的一些問題進行總結說明。

其性能描述如下:

-

支持JESD204B; -

超低的時鐘抖動和噪聲; -

能夠同時輸出14路差分時鐘:

<1>. 7對可作為JESD204B的SYSREF時鐘;

<2>.?最大輸出頻率可以達到3.1GHz;

<3>. 輸出差分時鐘的電平標準可編程選擇:LVPECL、LVDS、HSDS、以及LCPECL;

-

雙PLL結構; -

PLL2的VCO分頻系數為1-32; -

輸出時鐘精確的數字延時、模擬延時、以及動態延時; -

多工作模式:雙PLL、單PLL以及時鐘分發模式;

?

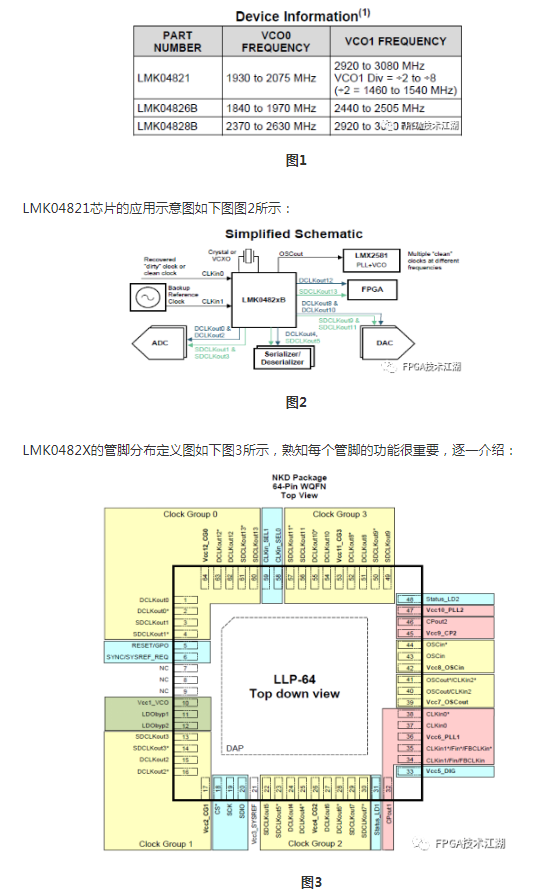

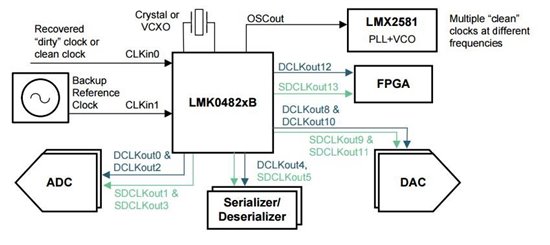

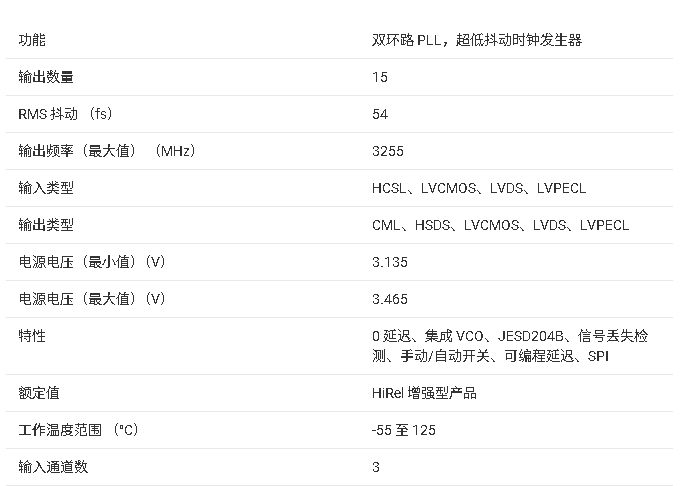

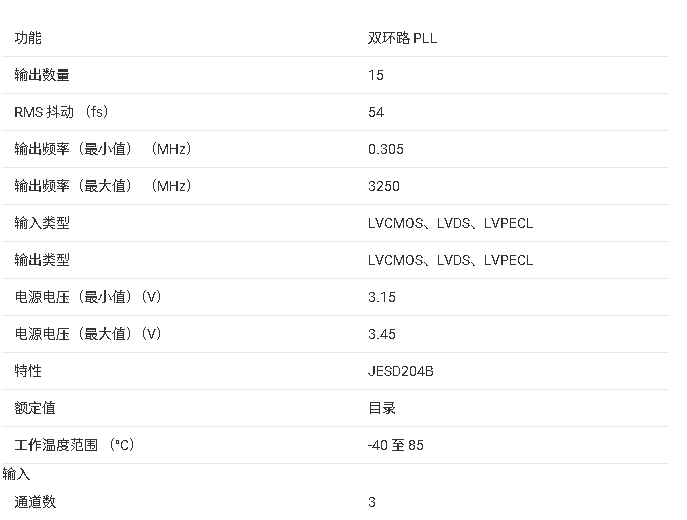

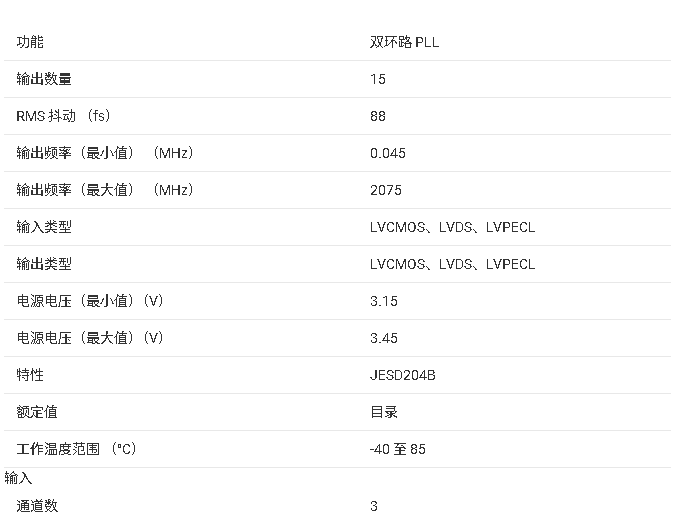

LMK0482X系列的這三款芯片不同之處在于支持不同的VCO,如下圖圖1所示:

?

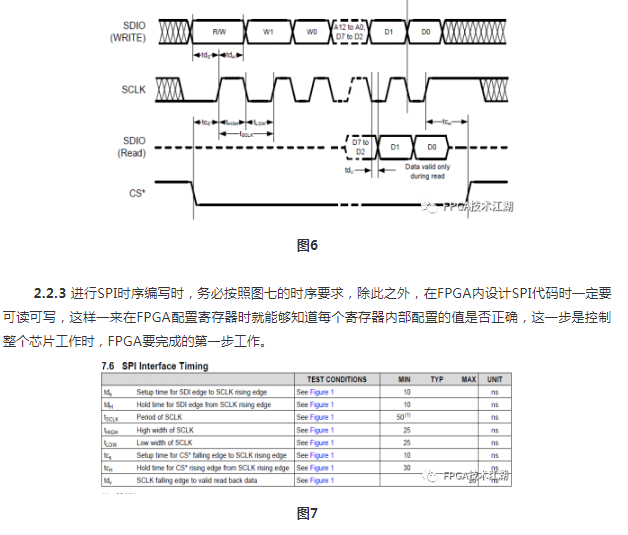

PIN1、2:第0路Device CLK差分輸出;

PIN3、4:第1路SYSREF/Device CLK差分輸出;

PIN5:??該芯片的復位輸入或者是通用GPIO;

PIN6:??該芯片的時鐘同步輸入端口或者是連續SYSREF CLK請求輸入端口;

PIN7、8、9:沒用,懸空即可;

PIN10:??電源輸入;

PIN12:LDO旁路電容,外接0.1uf到地;

PIN13、14:第3路SYSREF/Device CLK差分輸出;

PIN15、16:第2路Device CLK差分輸出;

PIN17:電源輸入;

PIN18:芯片的SPI配置CS信號;

PIN19:芯片的SPI配置SCK信號;

PIN20:芯片的SPI配置SDIO信號;

PIN21:電源輸入;

PIN22、23:第5路SYSREF/Device CLK差分輸出;

PIN24、25:第4路Device CLK差分輸出;

PIN26:電源輸入;

PIN27、28:第6路Device CLK差分輸出;

PIN29、30:第7路SYSREF/Device CLK差分輸出;

PIN31:可編程的狀態監測I/O管腳;

PIN32:PLL1的電荷泵輸出;

PIN33:電源輸入;

PIN34、35:PLL1的參考時鐘輸入1、零延遲模式下的外部反饋時鐘輸入、外部VCO輸入;

PIN36:電源輸入;

PIN37、38:PLL1的參考時鐘輸入0;

PIN39:電源輸入;

PIN40、41:反饋到PLL1,參考輸入到PLL2。AC耦合;

PIN42:電源輸入;

PIN43、44:PLL2的參考時鐘輸入、PLL1的反饋時鐘輸入;

PIN45:電源輸入;

PIN46:PLL2的電荷泵輸出;

PIN47:電源輸入;

PIN48:可編程的狀態監測I/O管腳;

PIN49、50:第9路SYSREF/Device CLK差分輸出;

PIN51、52:第8路Device CLK差分輸出;

PIN53:電源輸入;

PIN54、55:第10路Device CLK差分輸出;

PIN56、57:第11路SYSREF/Device CLK差分輸出;

PIN58:可編程的狀態監測I/O管腳;

PIN59:可編程的狀態監測I/O管腳;

PIN60、61:第13路SYSREF/Device CLK差分輸出;

PIN62、63:第12路Device CLK差分輸出;

PIN64:電源輸入;

DAP :??散熱盤,接地;

?

二、?LMK04821使用步驟

2.1 硬件電路檢查

2.1.1?芯片供電是否正常,是否符合器工作的條件,該步驟直接決定芯片能否正常工作,測試點參考下圖;

?

2.2 寄存器配置

LMK04821的配置采用SPI方式,其配置規則通過閱讀數據手冊提取關鍵的知識點,如下:

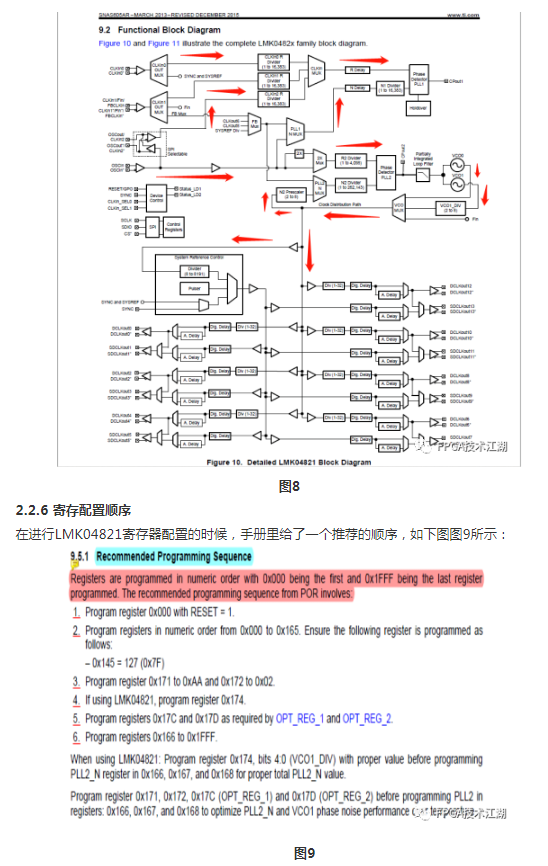

2.2.1?寫操作時,CS信號為低電平時,SDIO的數據在SCK上升沿寫進芯片,寫數據格式為1bit的讀寫控制位+2bit的0+13bit地址+8bit數據。

2.2.2?讀操作時,先寫入1bit的讀寫控制位+2bit的0+13bit地址,然后在接下來SCK的上升沿獲取8bit數據;

時序圖如下圖6所示:

?

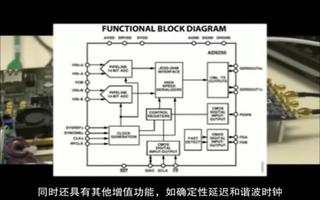

2.2.4 LMK04821的雙PLL級聯系統的介紹:

??該系列芯片功能非常靈活,一般JESD204B系統的雙PLL級聯應用最為經典,但是對于傳統的應用來說,同樣適用。需要注意的是Device CLK不提供單端輸出,只有OSCout管腳可以提供LVCMOS單端輸出。另外,除了雙PLL應用模式,亦可以配置單PLL或者時鐘分發模式。

-

LMK0482X系列芯片的雙PLL結構保證了在很寬的輸出頻率范圍內還可以輸出最低抖動的時鐘。第一級PLL(PLL1)被外部的參考時鐘驅動,第二級PLL(PLL2)由VCXO或者可調晶振提供高精度、低噪聲的二級參考時鐘。經過這兩級PLL,輸出時鐘的精度將會大大提高。 -

LMK0482X系列芯片共輸出7對JESD204B DeviceCLK和7對SYSREF CLK,其中每個Device CLK對應一個SYSREF CLK。對于那些非JESD204B的應用,SYSREF CLK同樣可以編程為Device CLK。 -

PLL1的輸入參考時鐘包括管腳CLKin0,CLKin1以及CLKin2,任選一個作為時鐘輸入即可,選擇的規則由配置寄存器參數決定。 -

VCXO/Crystal 緩存輸出,LMK0482X系列芯片提供OSCout輸出,該輸出其實就是PLL1的反饋輸入,也是PLL2的參考時鐘輸入,芯片的該功能其實就是為了在其編程之前可以提供一個時鐘給控制器工作,控制器編程再配置LMK0482X。OSCout輸出可以為LVDS、LVPECL以及LVMOS電平。 -

LMK0482X具有頻率保持的功能,當外部參考時鐘丟失后,輸出頻率還能保持最小的漂移,直到外部參考時鐘恢復。 -

7路Device CLK都可以分別的分頻,分頻系數為1~32。 -

7路SYSREF CLK統一分頻,分頻系數為8~8191。 -

Device CLK具有延遲的功能,其包括模擬延遲和數字延遲。模擬延遲是以25ps為單位的時鐘延遲模塊,使用該模塊本身也會帶來500ps的延時。數字延時范圍為4~32 VCO時鐘周期,每一個延遲單元的大小為0.5 VCO周期。需要注意的是延遲的功能必須在同步使能后才起作用。 -

SYSREF CLK同樣具有模擬核數字延遲。模擬延遲的最小單位為150ps。數字延遲的范圍為1.5~11VCO,同樣每一個延遲單元的大小為0.5 VCO周期。 -

14路時鐘的輸出不僅在電平標準上可編程,在輸出的幅度方面也可編程。 -

要使時鐘的數字延時起作用,管腳SYNC必須給一個脈沖,在脈沖的上升沿所有的時鐘同步。 -

LMK04821提供了幾個狀態管腳用來供用戶監測芯片內部的狀態或者作為輸入端口來響應用戶的需求,具體的功能在寄存器配置說明里介紹。

2.2.5 功能框圖

在輔助軟件TICS Pro中,生成的寄存器順序也是嚴格按照手冊中進行配置的。

但是在實際運用中,按照該寄存器配置順序,時鐘輸出端并沒有正確的時鐘輸出。實際運用中,將寄存器順序按照如下順序進行配置:

1、0X000配置兩次,先進行復位,然后0X000再配置00,無操作;

2、然后緊接著從0X100~0X145;

3、0X171~0X17D;

4、0X146~0X16E;

5、0X143(90)、0X149(00)、0X143(兩次B0、90)、0X144(FF)、0X143(兩次10、11)、0X139(03)、0X002(00);固定數值;盡量不要改變,具體為什么要這樣進行配置,對應數據手冊進行查閱即可。

注意:在實際應用中,目前為止該寄存器順序是唯一能夠正確產生時鐘的順序,可以參考軟件給的寄存器數據,盡量不要改變配置寄存器的順序。部分寄存器在設計中沒有進行配置,比如一些只讀寄存器,IC信息相關的寄存器,reback相關的寄存器都沒有進行配置,實際操作中無傷大雅,可以不用配置。但是在SPI配置寄存器時,如果要檢驗寄存器讀寫是否成功時,可以將這些寄存器進行讀操作,確保SPI操作正常。

2.2.7?寄存器對應數據

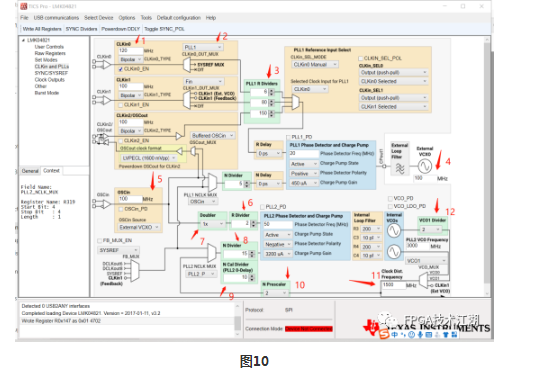

在此之前,確定寄存器配置順序之后,利用輔助軟件TICS Pro軟件產生對應的參數,按照6中所示的寄存器順序進行寫操作。軟件使用中重要參數的產生以及對應在軟件中如何設置見下圖圖10;

?

?

一定要熟練掌握軟件運用,明確在產生想要的時鐘時,如何進行軟件操作,得到相應的系數,軟件中每個點如何進行配合;參數之間是如何對應的,建議配合數據手冊進行對比,能夠事半功倍。

-

標記1選擇CLKin0作為參考時鐘輸入;硬件環境值在CLKin0端有時鐘輸入; -

標記2選擇PLL1,MUX是可以進行選擇的,不同的選擇,對應寄存器要配置的數值不同; -

標記3處選擇相應的DIV數值,得到需要的時鐘100M; -

標記4 CPout1直接連接到外部晶振,目的是,當參考時鐘丟失時,延時功能可以將PLL1的調諧電壓固定在VCXO或者可調諧晶振上,使得在外部參考時鐘丟失時,輸出的時鐘頻率的偏移最小,直到外部時鐘恢復。 -

標記5 OSCin,PLL1的反饋輸入,PLL2的參考時鐘輸入,實際調試中,發現OSCin如果沒有輸入,輸出端就沒有時鐘輸出,沒有CLKin0輸入,輸出時鐘依然正常輸出; -

標記6、7、8、9、10、11、12,這幾處都和PLL2 VCO Frequency有關系,手冊中顯示LMK04821在使用VCO1時,PLL2頻率要求在2920~3080MHz之間。 -

超出范圍,軟件會報紅出錯。這幾處設置其實就是簡單的將OSCin的時鐘進行先倍頻后分頻的一個操作;比如,實際中需要DCLKout輸出150M、75M時鐘,再復合要求范圍的情況下,找到一個合適的公倍數,例子中為1500M,這樣一來,既能得到150M的DCLKoutX的輸出,又能得到75M的時鐘輸出;

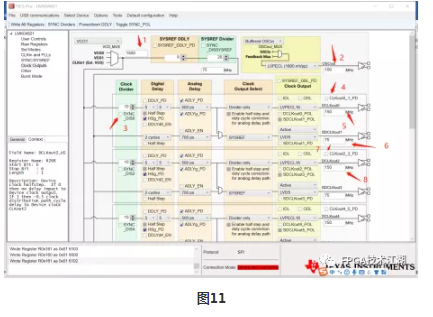

除此之外,時鐘輸出設置如下圖圖11所示:

?

-

標記1,公倍數; -

標記2,PLL1的反饋輸入,PLL2的參考輸入,實際運用中,PLL2的參考輸入為OSCin; -

標記3,分頻系數,1500M十分頻150M; -

標記4,選擇PD,意味著該通道不輸出,處于關閉狀態; -

標記5,DCLK輸出頻率,可在對應位置直接填入想要的數值。注意,最好是公倍數的整數分頻后的值,不然,軟件會自動產生一個和填入值最相近的數值; -

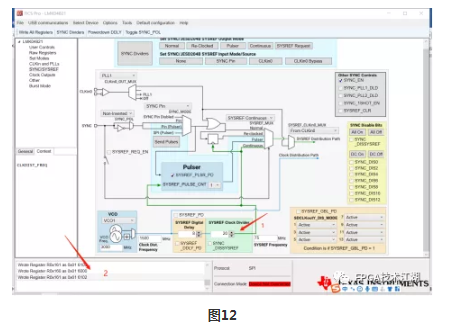

標記6,SCLK輸出端口,SCLK不能單獨分頻,7個通道只能統一進行分頻;具體設置如下圖圖12所示:

?

注意:在設定寄存器參數時,操作軟件時,會在左下方窗口標記2處顯示對應的寄存器以及數值,便于我們很迅速的在數據手冊中查到該數值進行了哪些配置;

軟件配置時,最重要的幾個參數以及對應的寄存器如下:

-

Doubler,對應相關寄存器0X162; -

R Divider,對應寄存器0X160、0X161; -

N?Divider,對應寄存器0X168; -

VCO,對應寄存器0X138; -

DCLKoutX_DIV, 對應寄存器0X100、0X108、0X110、0X1180、0X120、0X128、0X130; -

SYSREF?DIV,對應寄存器0X13A、0X13B;

注意;有些參數需要多個寄存器共同配合使用;另外的寄存器在軟件配置過程中會生成,按照具體的設計要求進行軟件操作配置,導出參數之后,在對應的寄存器中進行更改即可。

三、?運用結果

3.1 時鐘輸出結果

在對LMK04821芯片進行正確配置之后,時鐘能夠正常輸出想要的時鐘頻率,利用示波器進行測量,都能夠直接觀測到時鐘有輸出;程序中更改不同的分頻系數,也能夠在輸出端得到相應的時鐘輸出。

3.2 待解決問題

考慮到系統中要求時鐘同源的問題,在對CLKin0參考輸入時鐘、DCLK、SCLK通過示波器進行起始相位對比觀測,發現通過倍頻分頻后,時鐘起始相位存在大概1/4個周期偏差,多次測試,每次都有細微的偏差。

其中,DCLK與SCLK如果輸出頻率相同時,相位差通過觀察,有細微偏差,考慮到示波器使用過程中,探頭不穩定原因,暫定相位偏差為0;后期有更好的測試方法時,再進行確認。

電子發燒友App

電子發燒友App

評論