明德?lián)P的JESD204B采集卡項目綜合上板后,可以使用上位機通過千兆網來配置AD9144和AD9516板卡,實現高速ad采集。最終可以在示波器和上位機上采集到設定頻率的正弦波。本文重點介紹JESD204B時鐘網絡。

一,JESD204B時鐘網絡原理概述

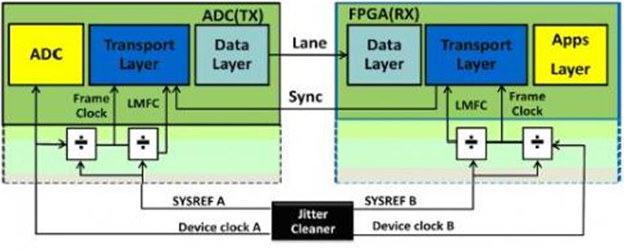

本文以JESD204Bsubclass1來討論時鐘的時序需要以及TI時鐘芯片方案的實現。任何一個串行協(xié)議都離不開幀和同步,JESD204B也不例外,也需要收發(fā)雙方有相同的幀結構,然后以一種方式來同步,即辨別起始。JESD204B是以時鐘信號的沿來辨別同步的開始,以及通過一定的握手信號使得收發(fā)雙方能夠正確識別幀的長度和邊界,因此時鐘信號及其時序關系對于JESD204B就顯得極其重要。下圖是典型的JESD204B系統(tǒng)的系統(tǒng)連接:

Device Clock是器件工作的主時鐘,一般在數模轉換器里為其采樣時鐘或者整數倍頻的時鐘,其協(xié)議本身的幀和多幀的時鐘也是基于Device Clock.SYSREF是用于指示不同轉換器或者邏輯的Device Clock的沿,或者不同器件間Deterministic latency的參考。如下圖所示,Device Clock和SYSREF必須滿足的時序關系。

SYSREF的第一個上升沿要非常容易的能被Device Clock捕捉到,這樣就需要SYSREF和Device Clock滿足上圖的時序關系。通常會因為PCB的線長以及時鐘器件不同通道輸出時的Skew,會帶來一定的誤差,Device Clock的上升沿不一定正好在SYSREF的脈沖的正中間,工程上只要在一定范圍內就能保證JESD204收發(fā)正常工作。

二,明德?lián)PJESD204B項目時鐘網絡介紹

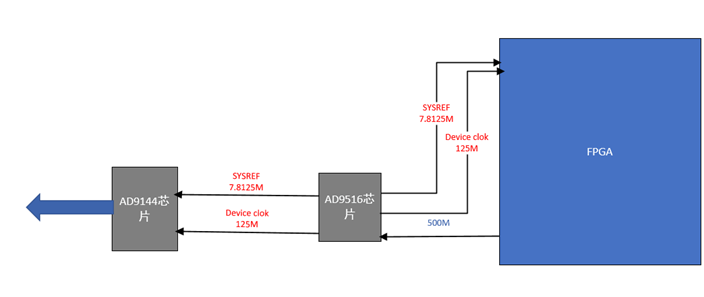

明德?lián)PJESD204B采集卡項目使用Xilinx的KC705開發(fā)板,外接的DA板卡包含ad9144芯片和ad9516時鐘芯片。

該項目由FPGA發(fā)送一個源時鐘到ad9516芯片,接著由ad9516芯片輸出4個時鐘,其中2個時鐘輸送到FPGA,另外2個時鐘輸送到ad9144芯片。具體架構如下圖:

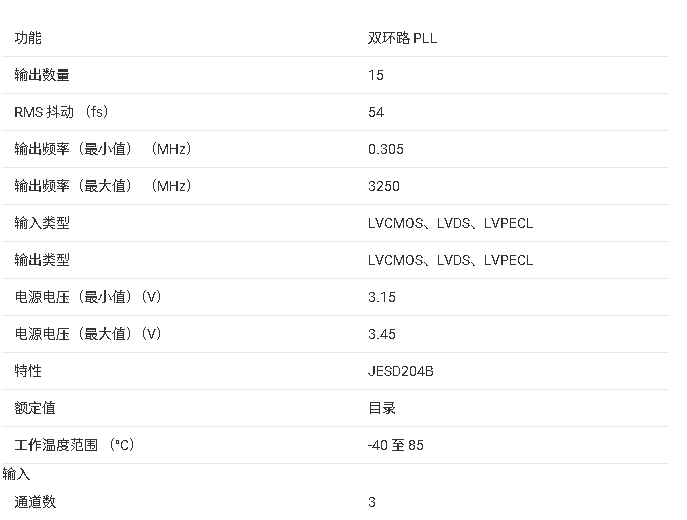

AD9516介紹

AD9516,這是一個由ADI公司設計的14路輸出時鐘發(fā)生器,具有亞皮秒級抖動性能,還配有片內集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)。片內VCO的調諧頻率范圍為2.55 GHz至2.95 GHz。或者,也可以使用最高2.4 GHz的外部VCO/VCXO。

AD9516有6路(3對)LVPECL輸出,4路(2對)LVDS輸出以及8路LVCMOS(每個LVDS可以作為2路LVCMOS)輸出。每對之間共享數值為1-32的分頻數值,因此,每對LVPECL或者LVDS輸出的時鐘頻率是相同的。LVPECL輸出可達1.6GHz,LVDS輸出可達800MHz,LVCMOS可達250MHz。輸入參考時鐘頻率和VCO工作頻率有如關系: Fvco=(Fref/R)*(P*B+A)

每路輸出還有單路的分頻因子(1-32)可以配置,通過參考時鐘的選擇,內部P、B、A寄存器以及每路分頻寄存器的配置,可以得到我們想要的時鐘。

以上就是關于明德?lián)PJESD204B的時鐘網絡的介紹,明德?lián)P可承接基于JESD204B的高速數據傳輸項目,若想了解更多,感興趣的同學可以留言相互討論!

-

時鐘網絡

+關注

關注

0文章

16瀏覽量

6709 -

JESD204B

+關注

關注

6文章

86瀏覽量

19922

發(fā)布評論請先 登錄

AD9528:高性能JESD204B/JESD204C時鐘發(fā)生器的深度解析

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

?LMK04368-EP 超低噪聲JESD204B/C雙環(huán)路時鐘抖動清除器總結

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

LTC6953具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9680 JESD204B接口的不穩(wěn)定會導致較大的電流波動,怎么解決?

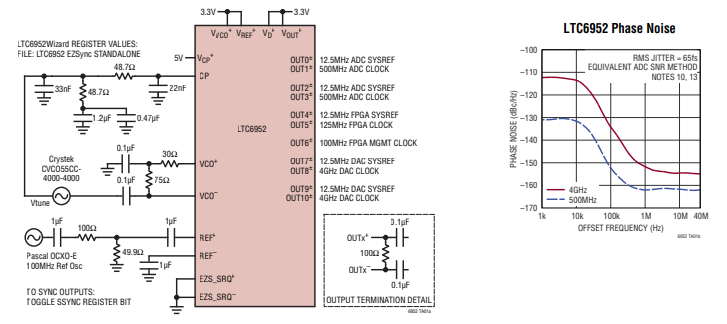

LTC6952具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz PLL技術手冊

JESD204B時鐘網絡原理概述

JESD204B時鐘網絡原理概述

評論