聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636207 -

轉換器

+關注

關注

27文章

9418瀏覽量

156327 -

ADI

+關注

關注

151文章

46104瀏覽量

277155

發布評論請先 登錄

相關推薦

熱點推薦

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

LMK0461x 器件系列是業界性能最高、功耗最低的抖動清除器,支持 JESD204B。16 個時鐘輸出可配置為使用器件和 SYSREF 時鐘驅動 8 個 JESD204B 轉換器或其

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04828-EP 器件是業界性能最高的時鐘調理器,支持 JESD204B。

PLL2的14個時鐘輸出可配置為使用器件和SYSREF時鐘驅動7個JESD204B轉換器或其他邏

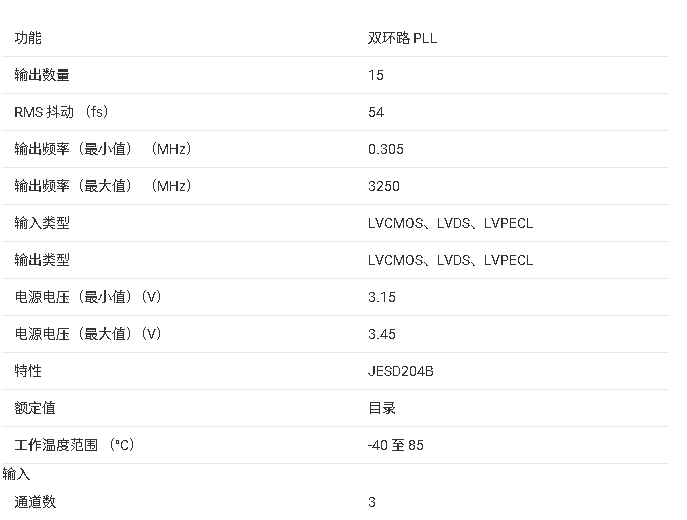

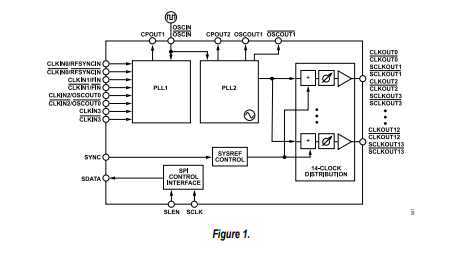

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

JESD204B轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于JESD204B應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

?LMK04368-EP 超低噪聲JESD204B/C雙環路時鐘抖動清除器總結

JESD204B/C 轉換器或其他邏輯器件。SYSREF 可以使用直流和交流耦合提供。不僅限于 JESD204B/C 應用,14 個輸出中的每一個都可以單獨配置為傳統時鐘系統的高性能輸出。

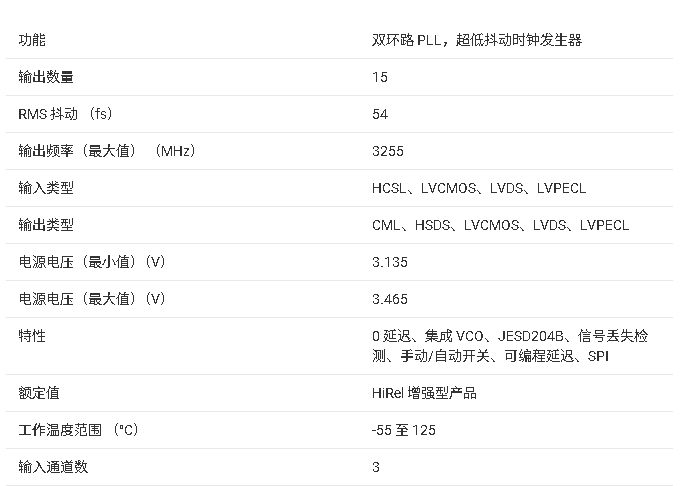

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

1. 概述PC7044是一款高性能雙環路的整數時鐘抖動消除器,可以為具有并行或串(JESD204B型)接口的高速數據轉換器執行參考時鐘選擇和超低噪聲頻率的生成。 PC7044具有兩個整

發表于 05-08 15:57

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

C subclass 1 器件時鐘 / SYSREF 對以及一個通用輸出,或者就是 11 個面向非 JESD204B/JESD204C 應用的通用時鐘輸出。每個輸出都有自己的可個別編程分頻器和輸出驅動

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14輸出抖動衰減器技術手冊

HMC7044B 是 [HMC7044]的修訂版本,是一款高性能、雙環路、整數 N 抖動衰減器,能夠為具有并行或串行(JESD204B 和 JESD204C 類型)接口的高速數據

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

AD采集芯片為AD9680-1000,時鐘芯片為AD9528。當 AD 采樣時鐘為 500MHz 時,jesd204B (串行線速 = 5 Gbps) 穩定。但是,當 AD 采樣時鐘為 800MHz

發表于 04-15 06:43

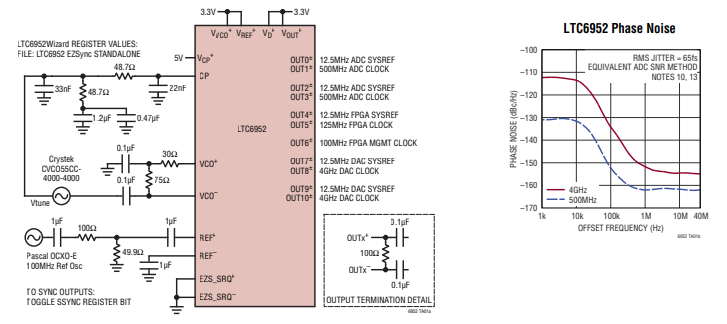

LTC6952具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz PLL技術手冊

JESD204B/C 應用的通用時鐘輸出。每個輸出都有自己的可單獨編程分頻器和輸出驅動器。所有輸出也可以采用單獨的粗略半周期數字延遲和精細模擬時間延遲實現同步,并設定為精確的相位對齊

使用jesd204b IP核時,無法完成綜合,找不到jesd204_0.v

做的,但是去問的時候人家說是根據兩個IP核的示例工程中的某個文件來在jesd204b_base.v中例化,其他的對方不記得了,這里想問下這個問題該怎么解決?

發表于 03-12 22:21

兩種JESD204B A/D轉換器轉FPGA設置與實現技巧

兩種JESD204B A/D轉換器轉FPGA設置與實現技巧

評論