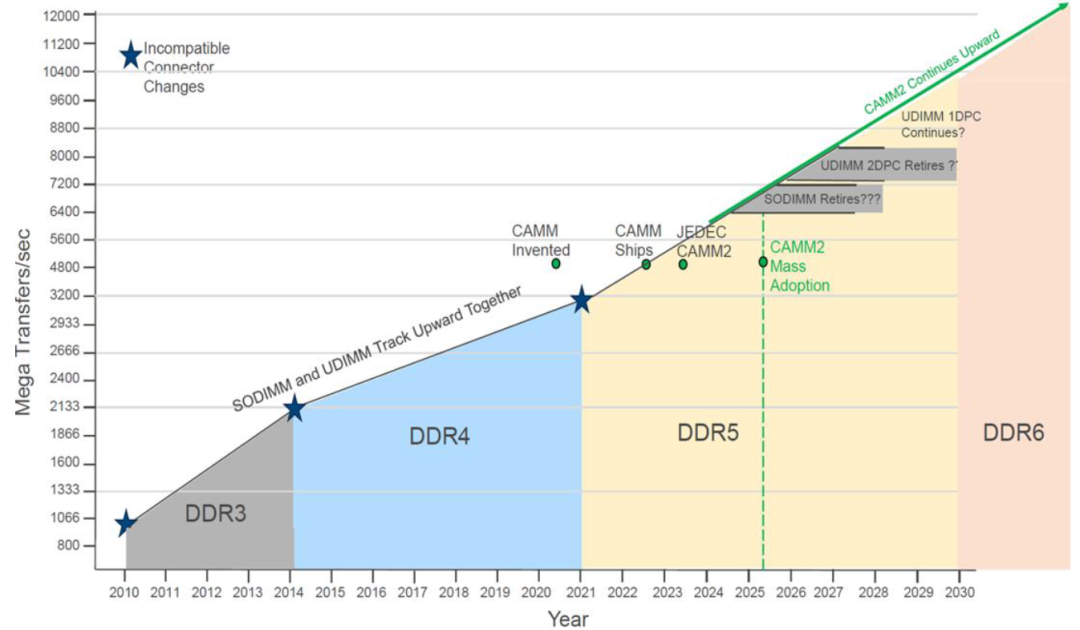

,隨著近期DRAM內(nèi)存的價格普遍開始下降,跟隨這一趨勢的DDR5內(nèi)存似乎終于有了用武之地。那么DDR5內(nèi)存的價格為何一開始那么貴呢,難道真的就是剛推出新技術(shù)帶來的高附加值? ? PMIC的供應(yīng)困難 ? DDR5在DDR4的基礎(chǔ)上做了許多改進,首先是更高的數(shù)據(jù)速率,從

2022-07-12 08:27:00 12762

12762 DDR3 作為第三代雙倍數(shù)據(jù)速率同步動態(tài)隨機存儲器,在內(nèi)存發(fā)展歷程中具有重要地位。它采用了8n預(yù)取架構(gòu),即每個時鐘周期能夠傳輸8倍于數(shù)據(jù)位寬的數(shù)據(jù)量,這使得數(shù)據(jù)傳輸效率大幅提升 。

2025-08-04 13:42:34 2913

2913

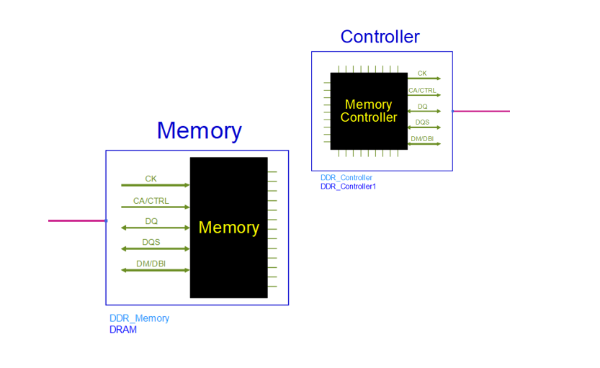

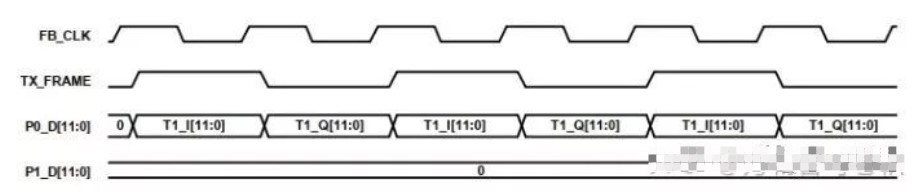

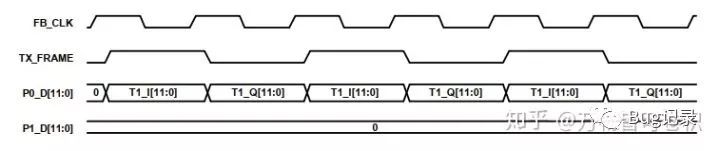

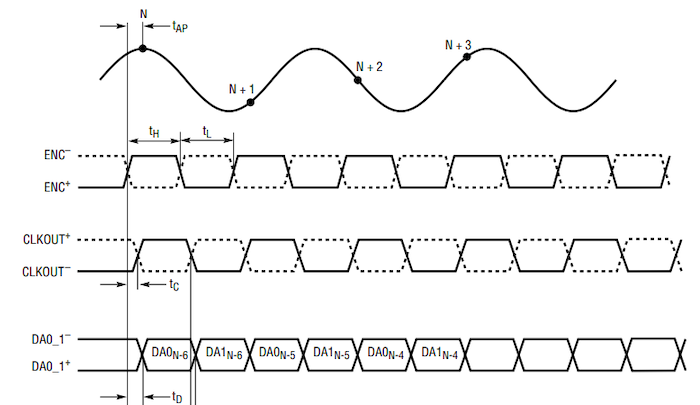

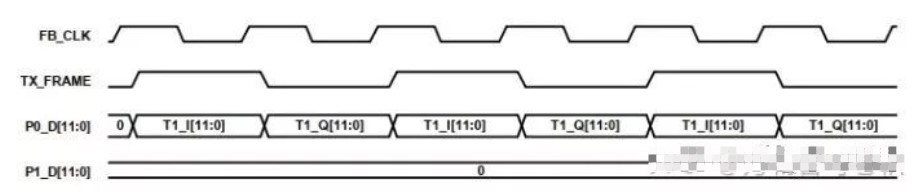

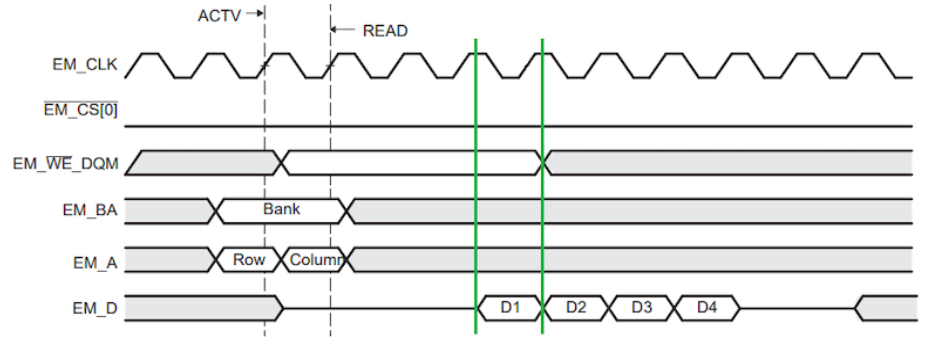

DDR內(nèi)存條是由多顆粒的DDRSDKAM芯片互連組成,DDRSDRAM是雙數(shù)據(jù)率同步動態(tài)隨機存儲器的縮寫。DDRSDRAM采用雙數(shù)據(jù)速率接口,也就是在時鐘的正沿或負沿都需要對數(shù)據(jù)進行采樣。在本設(shè)計中采用的內(nèi)存是hynix公司的lGB的HYMD564M646CP6-J。

2011-01-21 13:37:02 4624

4624

廉價的雙倍數(shù)據(jù)速率(DDR)內(nèi)存(以及DDR2和DDR3等后來的版本)為臺式機和筆記本電腦的工作內(nèi)存提供了支柱。通過在脈沖序列的前沿和后沿上為存儲器提供時鐘,存儲器吞吐量加倍,而功耗僅略微增加。

2019-03-25 08:48:00 5374

5374

傳統(tǒng)上,雙倍數(shù)據(jù)速率(DDR)技術(shù)依賴于時序測量,例如建立和保持時間。隨著標(biāo)準(zhǔn)的發(fā)展和傳輸速率的提高,信號完整性變得更具挑戰(zhàn)性。 對于DDR5,定時測量已被數(shù)據(jù)和命令地址信號的眼圖模板測量所取

2022-12-07 14:34:27 4209

4209

DDR是運行內(nèi)存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內(nèi)存具有雙倍速率傳輸數(shù)據(jù)的特性,因此在DDR內(nèi)存的標(biāo)識上采用了工作頻率×2的方法。 ? DDR芯片

2023-07-28 13:12:06 6090

6090

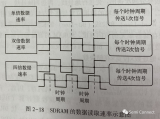

在同步動態(tài)隨機存取存儲器(SDRAM)的工作模式中,以數(shù)據(jù)讀取速率來分類,有單倍數(shù)據(jù)速率 (Single Data Rate, SDR) SDRAM、雙倍數(shù)據(jù)速率(Double Data Rate

2023-11-20 10:58:25 2072

2072

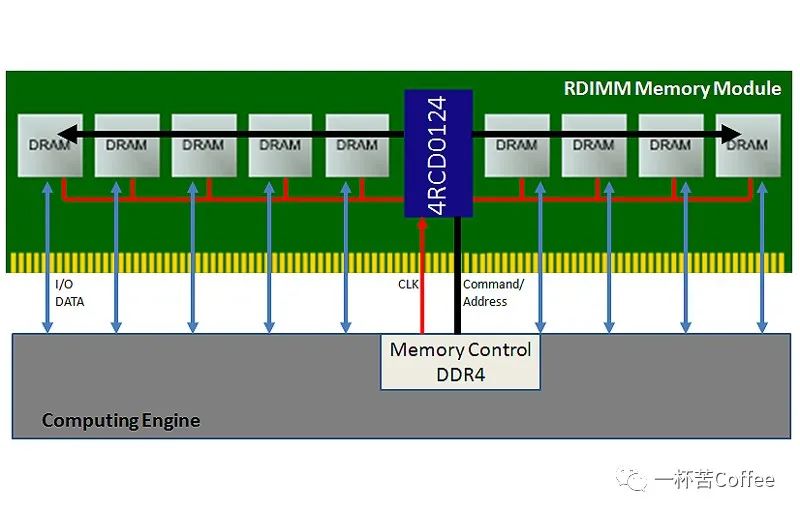

DDR4(第四代雙倍數(shù)據(jù)速率同步動態(tài)隨機存取存儲器)是一種高帶寬的存儲器,今天主要講述一下DDR4在Layout過程中的一些細節(jié)。在DDR的設(shè)計過程中,DDR的Layout是十分重要的環(huán)節(jié)。

2023-11-29 15:39:10 18207

18207

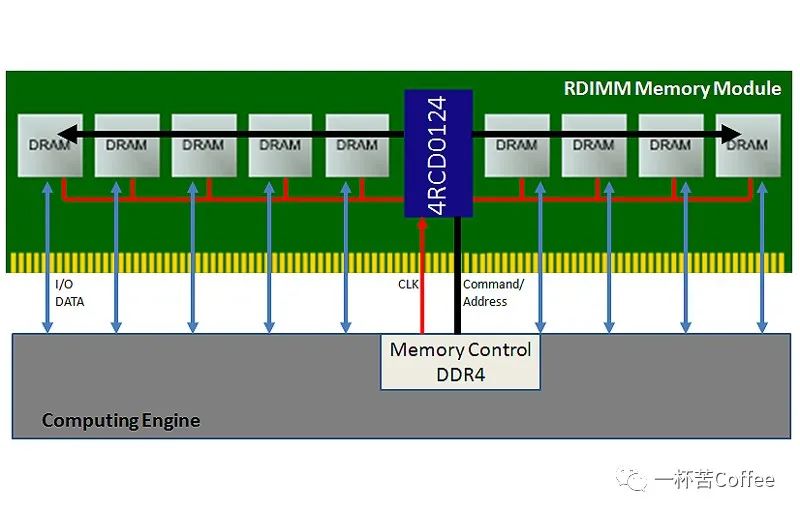

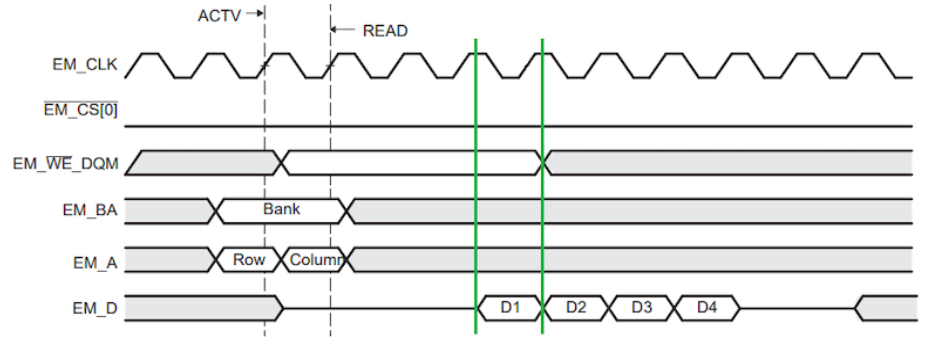

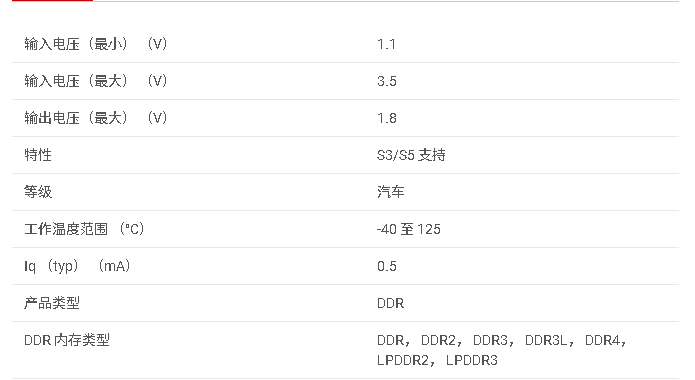

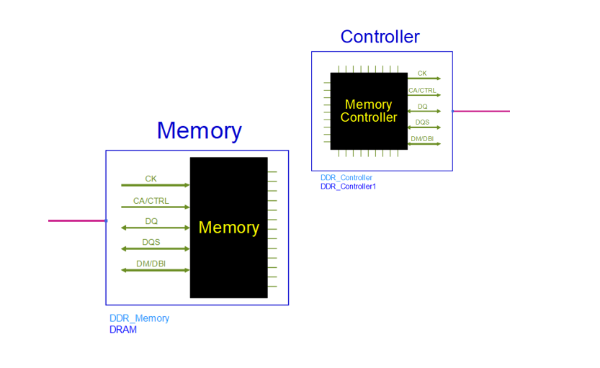

DDR內(nèi)存控制器是一個高度集成的組件,支持多種DDR內(nèi)存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設(shè)計的架構(gòu)來優(yōu)化內(nèi)存訪問效率。

2025-03-05 13:47:40 3578

3578

(Synchronous Dynamic Random Access Memory)的一種。 DDR 的主要特點是數(shù)據(jù)傳輸速率更高。DDR 內(nèi)存采用了一種稱為“雙倍數(shù)據(jù)速率”的技術(shù),它可以在一個時鐘周期內(nèi)傳輸兩次數(shù)據(jù),即在時鐘信

2025-10-27 19:28:16 7378

7378

DDR內(nèi)存條經(jīng)歷了DDR內(nèi)存條、DDR2內(nèi)存條、DDR3內(nèi)存條三個時代。這里給出了DDR內(nèi)存條、DDR2內(nèi)存條、DDR3內(nèi)存條的對比分析。

2011-12-29 14:21:56 4586

4586 日本著名存儲設(shè)備制造商Century Micro近日宣布即將推出新的DDR4內(nèi)存模塊,具有3,200 MHz的原生速率。

2019-07-07 10:37:45 3924

3924 傳輸;而DDR內(nèi)存則是一個時鐘周期內(nèi)傳輸兩次次數(shù)據(jù),它能夠在時鐘的上升期和下降期各傳輸一次數(shù)據(jù),因此稱為雙倍速率同步動態(tài)隨機存儲器。DDR內(nèi)存可以在與SDRAM相同的總線頻率下達到更高的數(shù)據(jù)

2011-02-27 16:47:17

800Mbps。但是DDR的數(shù)據(jù)信號卻是雙倍速率的,如果DQS頻率為800MHz,那么數(shù)據(jù)信號的速率就應(yīng)該為1600Mbps。下面將通過具體的仿真實例來看一下。有興趣的朋友可戳附件下載。

2016-11-08 16:59:51

內(nèi)存設(shè)備:

?雙倍數(shù)據(jù)速率3(DDR3)SDRAM。

?低壓DDR3 SDRAM。

?雙倍數(shù)據(jù)速率4(DDR4)SDRAM

2023-08-02 08:30:00

這是DMC-500的高級概述。

DMC-500是由ARM開發(fā)、測試和許可的ARM AMBA?SoC外圍設(shè)備。

它是一款高性能、面積優(yōu)化的內(nèi)存控制器,與AMBA 4 AXI協(xié)議兼容。

它支持以下存儲設(shè)備:

·低功耗雙倍數(shù)據(jù)速率3(LPDDR3)SDRAM。

·LPDDR4 SDRAM。

2023-09-04 07:05:12

以下內(nèi)存設(shè)備:

?雙倍數(shù)據(jù)速率3(DDR3)SDRAM。

?低壓DDR3 SDRAM。

?雙倍數(shù)據(jù)速率4(DDR4)SDRAM。

2023-08-02 11:55:49

功能是將內(nèi)存系統(tǒng)變成雙倍數(shù)據(jù)速率 (DDR) 內(nèi)存系統(tǒng)的原因。“單泵”存儲系統(tǒng)采用歷史悠久的策略將數(shù)據(jù)從一個 IC 同步移動到另一個 IC。基本上,邏輯信號每個時鐘周期改變一次,并在時鐘的上升沿或下降沿

2023-02-23 16:57:31

,內(nèi)部命令的發(fā)送與數(shù)據(jù)的傳輸都以時鐘為基準(zhǔn)。DDR SDRAM (Double Data Rate SDRAM,雙倍速率SDRAM ) 的不同之處在于它可以在一個時鐘讀寫兩次數(shù)據(jù),這樣就使得數(shù)據(jù)

2022-10-26 16:37:40

,它是在時鐘的上升期進行數(shù)據(jù)傳輸;而DDR內(nèi)存則是一個時鐘周期內(nèi)傳輸兩次次數(shù)據(jù),它能夠在時鐘的上升期和下降期各傳輸一次數(shù)據(jù),因此稱為雙倍速率同步動態(tài)隨機存儲器。DDR內(nèi)存可以在與SDRAM 相同的總線

2019-08-01 10:17:46

我的設(shè)計輸入時輸入時鐘頻率為150Mhz,用于視頻輸入接口的雙倍數(shù)據(jù)速率。但是,我發(fā)現(xiàn)保持時間錯誤如下所示:// HOLD時間ERROR名稱松弛水平高扇出從至總延遲邏輯延遲凈延遲需求源時鐘目的地時鐘

2020-05-01 14:42:58

DDR是運行內(nèi)存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內(nèi)存具有雙倍速率傳輸數(shù)據(jù)的特性,因此在DDR內(nèi)存的標(biāo)識上采用了工作頻率×2的方法。

DDR芯片的工作原理

2023-12-25 14:02:58

DDR是運行內(nèi)存芯片,其運行頻率主要有100MHz、133MHz、166MHz三種,由于DDR內(nèi)存具有雙倍速率傳輸數(shù)據(jù)的特性,因此在DDR內(nèi)存的標(biāo)識上采用了工作頻率×2的方法。

DDR芯片的工作原理

2023-12-25 13:58:55

描述此參考設(shè)計介紹高可靠性應(yīng)用(基于 66AK2Gx 多內(nèi)核 DSP + ARM 處理器片上系統(tǒng) (SoC))中具有糾錯碼 (ECC) 支持的雙倍數(shù)據(jù)速率 (DDR) 存儲器接口的系統(tǒng)注意事項。其中

2022-09-15 06:26:24

,也就是說數(shù)據(jù)速率是時鐘頻率的兩倍,可以達到很高的數(shù)據(jù)讀寫速度。此外它通過對地址線的分時復(fù)用,可以做到很大的容量。比如我們設(shè)計實現(xiàn)的DDR內(nèi)存時鐘頻率可達到150MHz,數(shù)據(jù)速率為300MHz,容量

2019-04-12 07:00:09

DDR內(nèi)存條是由多顆粒的DDR SDKAM芯片互連組成,DDR SDRAM是雙數(shù)據(jù)率同步動態(tài)隨機存儲器的縮寫。DDR SDRAM采用雙數(shù)據(jù)速率接口,也就是在時鐘的正沿或負沿都需要對數(shù)據(jù)進行采樣。

2019-08-15 07:32:03

描述此參考設(shè)計介紹高可靠性應(yīng)用(基于 66AK2Gx 多內(nèi)核 DSP + ARM 處理器片上系統(tǒng) (SoC))中具有糾錯碼 (ECC) 支持的雙倍數(shù)據(jù)速率 (DDR) 存儲器接口的系統(tǒng)注意事項。其中

2018-10-22 10:20:57

內(nèi)存控制器/ ddr(1 2或3)連續(xù)帶寬有多大。我看到每秒大約800兆比特的音符,這是真的嗎? 對于運行在120加MHz時鐘,雙倍數(shù)據(jù)速率和32位寬的DDRx來說,它似乎很低?就像12中的一個時鐘

2019-06-21 07:35:14

如何有效地在ATE上提高DDR存儲器接口測試覆蓋率葉慶, 郭錚, 楚中曙, 粟涯上海交通大學(xué)微電子學(xué)院,上海,中國,200122摘要:雙倍數(shù)據(jù)速率( DDR, Double Data Rate)DRAM由于其速

2009-12-15 14:58:22 34

34 什么是DDR SDRAM內(nèi)存

DDR是一種繼SDRAM后產(chǎn)生的內(nèi)存技術(shù),DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數(shù)據(jù)傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 2129

2129 DDR SDRAM內(nèi)存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 954

954 DDR4,什么是DDR4

DDR 又稱雙倍速率SDRAM Dual Date Rate SDRSM DDR SDRAM 是一種高速CMOS動態(tài)隨即訪問的內(nèi)存美國JEDEC 的固態(tài)技術(shù)協(xié)會于2000 年6 月公

2010-03-24 16:08:39 3959

3959 泰科電子(TE)按照J(rèn)EDEC工業(yè)標(biāo)準(zhǔn)推出了新型超低型VLP (very low-profile)第三代雙倍數(shù)據(jù)速率(DDR3)雙列直插式內(nèi)存模組(DIMM)插槽。

該產(chǎn)品最高卡扣高度為16毫米,進而減小

2010-12-11 09:18:45 1991

1991 摘要:介紹了一種基于現(xiàn)場可編程門陣列(FPGA) 和第二代雙倍數(shù)據(jù)率同步動態(tài)隨機存取記憶體(DDR2) 的高速模 數(shù)轉(zhuǎn)換(ADC) 采樣數(shù)據(jù)緩沖器設(shè)計方法,論述了在Xilinx V5 FPGA 中如何實現(xiàn)高速同步

2011-03-31 16:38:08 140

140 DDR是雙倍數(shù)據(jù)速率的SDRAM內(nèi)存,如今大多數(shù)計算機系統(tǒng)、服務(wù)器產(chǎn)品的主流存儲器技術(shù),并且不斷向嵌入式系統(tǒng)應(yīng)用領(lǐng)域滲透

2011-04-11 11:16:41 7104

7104

DDR2 SDRAM (雙倍數(shù)據(jù)速率2同步DRAM)存儲器是當(dāng)前流行的動態(tài)隨機訪問存儲器(DRAM)技術(shù)。SDRAM 已經(jīng)從DDR 演進到DDR2 和DDR3,實現(xiàn)了容量更大、速度更快的存儲器。其當(dāng)前的性能水平是DDR2/800

2011-05-14 15:26:19 21

21 Cyclone 系列芯片是美國A ltera 公司推出的低價格、高容量現(xiàn)場可編程門陣列器件(FPGA ) , 本文概述了他的主要特點, 給出了其在與外部存儲器接口時用到的雙倍數(shù)據(jù)率輸入輸出接口的設(shè)計方

2011-06-27 16:27:41 45

45 DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流 SDRAM 。DDRSDRAM 在原有的SDRAM 的基礎(chǔ)上改進而來。也正因為如此,DDR 能夠憑借著轉(zhuǎn)產(chǎn)成本 優(yōu)勢來打敗昔日的對手RDRAM,成為當(dāng)今的主

2011-07-12 09:48:02 718

718 JEDEC 固態(tài)技術(shù)協(xié)會,全球微電子產(chǎn)業(yè)標(biāo)準(zhǔn)領(lǐng)導(dǎo)制定機構(gòu)日前公布了廣為業(yè)界期待的DDR4(雙倍數(shù)據(jù)速率4)內(nèi)存標(biāo)準(zhǔn)的關(guān)鍵屬性。 預(yù)計將于2012年中期發(fā)布的JEDEC DDR4內(nèi)存標(biāo)準(zhǔn)與之前幾代的技術(shù)

2011-08-24 08:57:46 2350

2350 CMOS 邏輯系統(tǒng)的功耗主要與時鐘頻率、系統(tǒng)內(nèi)各柵極的輸入電容以及電源電壓有關(guān),傳統(tǒng)上,邏輯系統(tǒng)僅對一個時鐘沿的數(shù)據(jù)計時,而雙倍數(shù)據(jù)速率 (DDR) 內(nèi)存同時對時鐘的前沿和下降沿計

2011-12-16 17:56:32 4126

4126

DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流SDRAM。DDRSDRAM 在原有的SDRAM 的基礎(chǔ)上改進而來。也正因為如此,DDR 能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢來打敗昔日的對手RDRAM,成為當(dāng)今的主流

2013-09-13 15:17:30 213

213 雖然新一代電腦/智能手機用上了DDR4內(nèi)存,但以往的產(chǎn)品大多還是用的DDR3內(nèi)存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內(nèi)存都有哪些區(qū)別。相比上一代DDR3,新一代DDR4內(nèi)存主要有以下幾項核心改變:

2017-11-08 15:42:23 32470

32470 5的規(guī)范制定已經(jīng)到0.5版本,會在DDR4的基礎(chǔ)上數(shù)據(jù)速率和密度再翻一倍,單顆粒容量可達32Gb,并預(yù)計會在2020年開始商用。 很多人會把DDR5和顯卡上使用的GDDR5技術(shù)混淆,實際上兩者應(yīng)用場合不一樣。下面這張圖展示了目前三種主流內(nèi)存技術(shù)(DDR、GDDR、LPDDR)的速度對比和應(yīng)用場合。

2017-11-15 16:36:03 48251

48251

DDR SDRAM全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流SDRAM。DDR SDRAM在原有的SDRAM的基礎(chǔ)上改進而來。也正因為如此,DDR能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢來

2018-03-16 14:24:01 32

32 DDR 同步動態(tài)隨機存取存儲器 (Synchronous Dynamic Random Access Memory, SDRAM)控制器使用雙倍數(shù)據(jù)速率(Dual Data Rate,DDR)版本

2018-05-30 09:29:00 8

8 大家好,我叫Paul Evans,是Stratix III產(chǎn)品營銷經(jīng)理。到目前為止,我已經(jīng)從事了6年的雙倍數(shù)據(jù)速率存儲器工作,今天和大家一起討論一下DDR3。DDR3的主要難題之一是它引入了數(shù)據(jù)交錯

2018-06-22 05:00:00 9489

9489 DDR=Double Data Rate雙倍速率同步動態(tài)隨機存儲器。嚴(yán)格的說DDR應(yīng)該叫DDR SDRAM,人們習(xí)慣稱為DDR,其中,SDRAM 是Synchronous Dynamic

2019-02-04 11:40:00 9513

9513 TPS51200器件是專為低輸入電壓,低成本,低噪聲系統(tǒng)而設(shè)計的接收器和源雙倍數(shù)據(jù)速率(DDR)終端穩(wěn)壓器,空間是關(guān)鍵考慮因素。

2019-08-26 17:30:00 5

5 FCI開發(fā)了一系列垂直內(nèi)存插槽,可接受標(biāo)準(zhǔn)DDR2(雙倍數(shù)據(jù)速率)內(nèi)存模塊組件,以便在臺式機和服務(wù)器中實現(xiàn)內(nèi)存擴展。 240位DDR2垂直連接器提供用于焊接端接的直通式引線或用于壓配端接的“針眼”引線。

2019-10-06 15:56:00 3665

3665 DDR:Double Date Rate 雙倍速率同步動態(tài)隨機存儲器。

2019-08-19 09:30:34 4349

4349 當(dāng)今電子產(chǎn)品一個很重要的區(qū)分元素是其所用的存儲器。服務(wù)器、計算機、智能手機、游戲機、GPS 以及幾乎所有類似產(chǎn)品使用的都是現(xiàn)代處理器和 FPGA。這些設(shè)備需要高速、高帶寬、雙倍數(shù)據(jù)速率 (DDR) 存儲器才能運行。

2019-12-11 13:52:13 5443

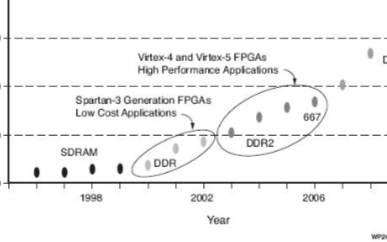

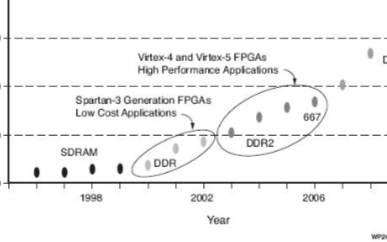

5443 20 世紀(jì) 90 年代后期,存儲器接口從單倍數(shù)據(jù)速率 (SDR) SDRAM 發(fā)展到了雙倍數(shù)據(jù)速率 (DDR) SDRAM,而今天的 DDR2 SDRAM 運行速率已經(jīng)達到每引腳 667 Mb/s或

2020-04-12 10:57:53 1552

1552

傳輸。SDRAM在一個時鐘周期內(nèi)只傳輸一次數(shù)據(jù),它是在時鐘上升期進行數(shù)據(jù)傳輸;而DDR則是一個時鐘周期內(nèi)可傳輸兩次數(shù)據(jù),也就是在時鐘的上升期和下降期各傳輸一次數(shù)據(jù)。下面英尚微電子介紹DDR SDRAM內(nèi)存發(fā)展歷程。 (1)DDR SDRAM DDR SDRAM雙倍數(shù)據(jù)率同步動態(tài)隨機存取存儲器,它是

2020-07-16 15:44:10 2742

2742 的數(shù)據(jù)傳輸量,這也是 DDR 的意義——Double Data Rate,雙倍數(shù)據(jù)速率。舉例來說,DDR266 標(biāo)準(zhǔn)的 DDR SDRAM 能提供 2.1GB/s 的內(nèi)存帶寬,而傳統(tǒng)的 PC133 SDRAM

2020-10-30 10:51:48 2634

2634 的數(shù)據(jù)傳輸量,這也是 DDR 的意義——Double Data Rate,雙倍數(shù)據(jù)速率。舉例來說,DDR266 標(biāo)準(zhǔn)的 DDR SDRAM 能提供 2.1GB/s 的內(nèi)存帶寬,而傳統(tǒng)的 PC133 SDRAM 卻只能提供 1.06GB/s 的內(nèi)存帶寬。

2020-12-23 11:38:00 11

11 DDR4內(nèi)存條的價格已經(jīng)很便宜了,2021年就會有DDR5內(nèi)存上市了,雖然初期主要面向數(shù)據(jù)中心市場,但是新一代平臺值得期待,DDR5內(nèi)存頻率相比現(xiàn)在可以翻倍。

2020-12-12 10:01:51 3254

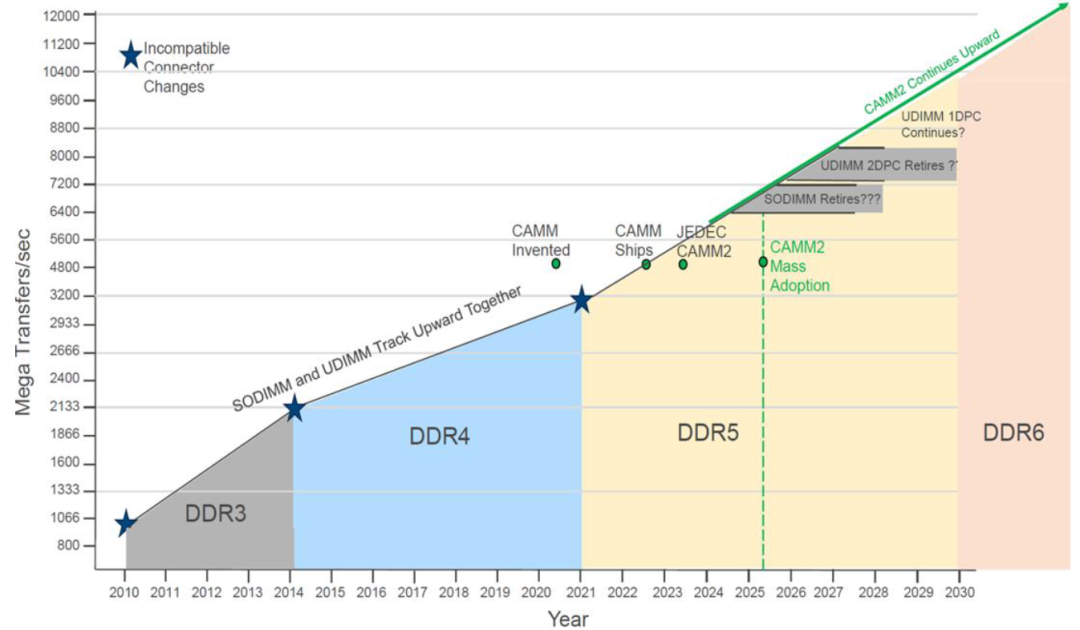

3254 DDR5在DDR4的基礎(chǔ)上做了許多改進,首先是更高的數(shù)據(jù)速率,從DDR4最高的3200MT/s,到了DDR5最高的6400MT/s;其次是提高內(nèi)存穩(wěn)定性的片上ECC糾錯機制,以及降低功耗的1.1V電壓,而內(nèi)存模組硬件上最大的改變之一莫過于新加入的電源管理芯片(PMIC)。

2022-07-12 09:58:50 6180

6180 注意,這里的DDR指的是Double Data Rate,雙倍數(shù)據(jù)速率。這篇文章并不是講DDR存儲器系列的東西。

2022-08-20 10:29:28 3782

3782

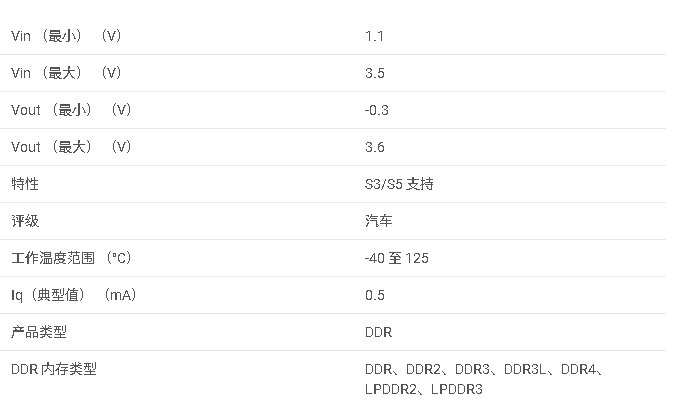

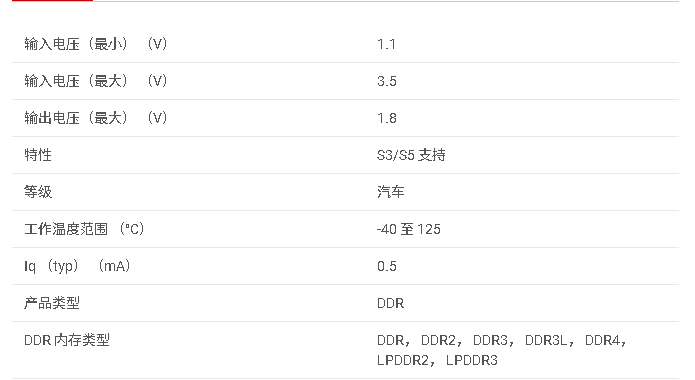

TPS51200A-Q1 器件是一款灌電流和拉電流雙倍數(shù)據(jù)速率 (DDR) 終端穩(wěn)壓器,專門針對低輸入電壓、低成本、低噪聲的空間受限型系統(tǒng)而設(shè)計。

2022-09-30 09:47:35 1439

1439 瑞薩為雙倍數(shù)據(jù)速率 5 (DDR5) 應(yīng)用提供 SPD 集線器、電源管理 IC (PMIC)、溫度傳感器和控制 MCU。該解決方案允許自定義可尋址 RGB (ARGB) 照明,具有多達數(shù)百萬種顏色可供選擇,從而可以輕松地為 PC 添加個人風(fēng)格。

2022-12-09 14:55:59 1

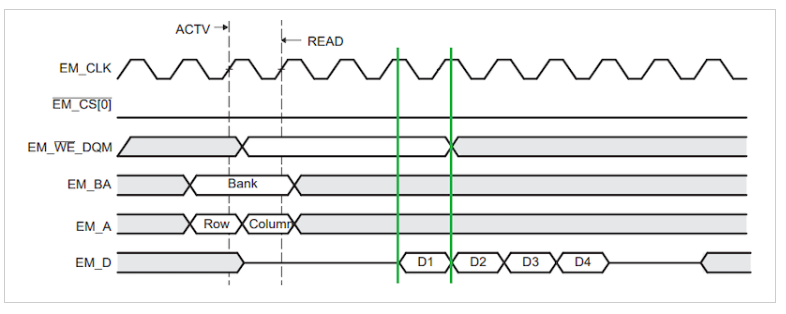

1 DDR3 SDRAM使用

雙倍數(shù)據(jù)速率架構(gòu)來實現(xiàn)高速操作。

雙倍數(shù)據(jù)速率結(jié)構(gòu)是一種8n預(yù)取架構(gòu),其接口經(jīng)過設(shè)計,可在I/O引腳上每個時鐘周期傳輸兩個

數(shù)據(jù)字。

DDR3 SDRAM的單個讀或?qū)懖僮饔行У匕?/div>

2023-02-06 10:12:00 14

14 DDR的拓撲結(jié)構(gòu)有哪些 DDR簡介 (1)DDR=Double Data Rate雙倍速率同步動態(tài)隨機存儲器。嚴(yán)格的說DDR應(yīng)該叫DDR SDRAM,人們習(xí)慣稱為DDR,其中,SDRAM

2023-03-07 13:49:18 2061

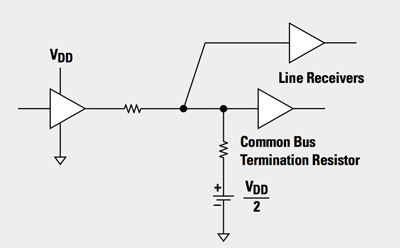

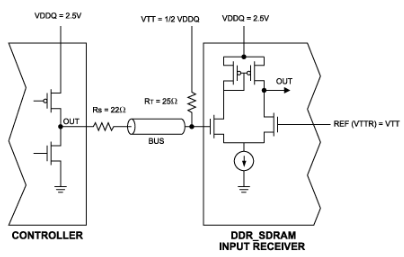

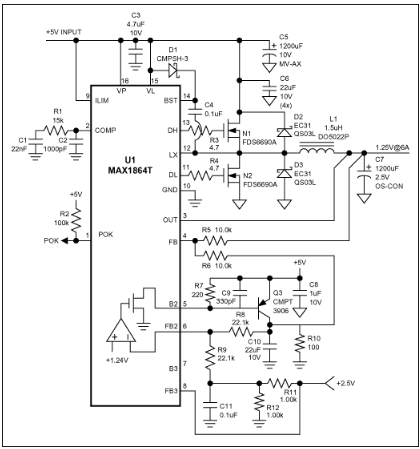

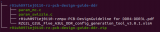

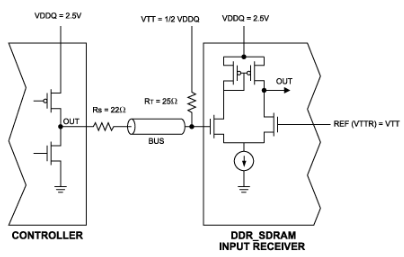

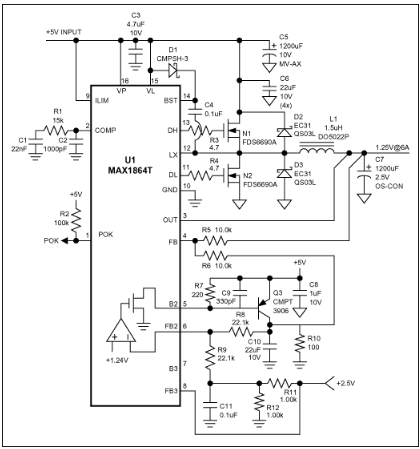

2061 雙倍數(shù)據(jù)速率(DDR)同步動態(tài)隨機存取存儲器(SDRAM)最近越來越受歡迎。DDR 內(nèi)存需要跟蹤主內(nèi)存電壓 VDDQ 的主動端接 VTT。本應(yīng)用筆記提供開關(guān)穩(wěn)壓器方案,利用MAX1957脈寬調(diào)制(PWM)降壓控制器為VTT端接提供1/2跟蹤輸出。

2023-03-13 09:35:23 3102

3102

串行數(shù)據(jù)傳輸與并行數(shù)據(jù)傳輸相比具有重要優(yōu)勢,在許多系統(tǒng)中,這些優(yōu)勢足以證明添加串行化和反串行化的并行數(shù)據(jù)電路是合理的,以便它可以作為串行數(shù)據(jù)傳輸。然而,計算機內(nèi)存是一個應(yīng)用領(lǐng)域,其中并行數(shù)據(jù)傳輸仍然

2023-04-06 15:02:30 1749

1749

注意,這里的DDR指的是Double Data Rate,雙倍數(shù)據(jù)速率。這篇文章并不是講DDR存儲器系列的東西。

2023-06-16 10:22:06 2058

2058

DDR是DDR SDRAM的簡稱,只是人們習(xí)慣了稱之為DDR,全稱為Double Data Rate Synchronous Dynamic Random Access Memory,中文名為:雙倍速率同步動態(tài)隨機存儲器,同步是指需要時鐘。

2023-06-25 15:06:40 10149

10149

本設(shè)計筆記顯示了用于工作站和服務(wù)器的高速內(nèi)存系統(tǒng)的雙倍數(shù)據(jù)速率 (DDR) 同步 DRAM (SDRAM)。使用MAX1864 xDSL/電纜調(diào)制解調(diào)器電源,電路產(chǎn)生等于并跟蹤VREF的終止電壓(VTT)。

2023-06-26 10:34:36 1589

1589

DDR是Double Data Rate的縮寫,即“雙倍速率同步動態(tài)隨機存儲器”。DDR是一種技術(shù),中國大陸工程師習(xí)慣用DDR稱呼用了DDR技術(shù)的SDRAM,而在中國臺灣以及歐美,工程師習(xí)慣用DRAM來稱呼。

2023-07-16 15:27:10 16394

16394

DDR5的主板不支持使用DDR4內(nèi)存。DDR5(第五代雙倍數(shù)據(jù)率)和DDR4(第四代雙倍數(shù)據(jù)率)是兩種不同規(guī)格的內(nèi)存技術(shù),它們在電氣特性和引腳布局上存在明顯差異。因此,DDR5內(nèi)存模塊無法插入DDR4主板插槽中,也不兼容DDR4內(nèi)存控制器。

2023-08-09 15:36:25 35589

35589 在全默認(rèn)設(shè)置的情況下,影馳HOF OC Lab幻跡S DDR5 8000內(nèi)存的工作速率為DDR5 4800,延遲設(shè)定為40-40-40-76,因此在這個設(shè)置下它的內(nèi)存性能并不突出,與普通的DDR5 4800內(nèi)存相當(dāng)。

2023-09-15 10:40:42 3033

3033

前所未有的指數(shù)級增長。面對這種前景,內(nèi)存帶寬成了數(shù)字時代的關(guān)鍵“動脈”。其中,以雙倍數(shù)據(jù)傳輸速率和更高的帶寬而聞名的DDR(DoubleDataRate)技術(shù)作為動

2023-10-28 08:13:26 1208

1208

DDR4和DDR3內(nèi)存都有哪些區(qū)別? 隨著計算機的日益發(fā)展,內(nèi)存也越來越重要。DDR3和DDR4是兩種用于計算機內(nèi)存的標(biāo)準(zhǔn)。隨著DDR4內(nèi)存的逐漸普及,更多的人開始對兩者有了更多的關(guān)注。 DDR

2023-10-30 09:22:00 13842

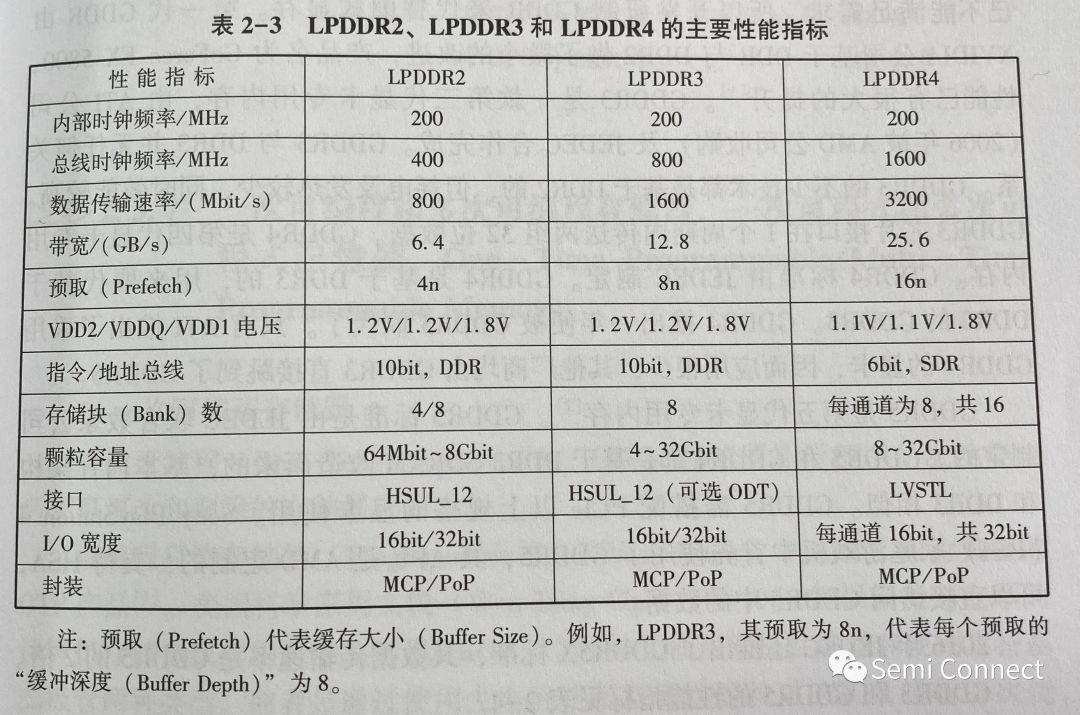

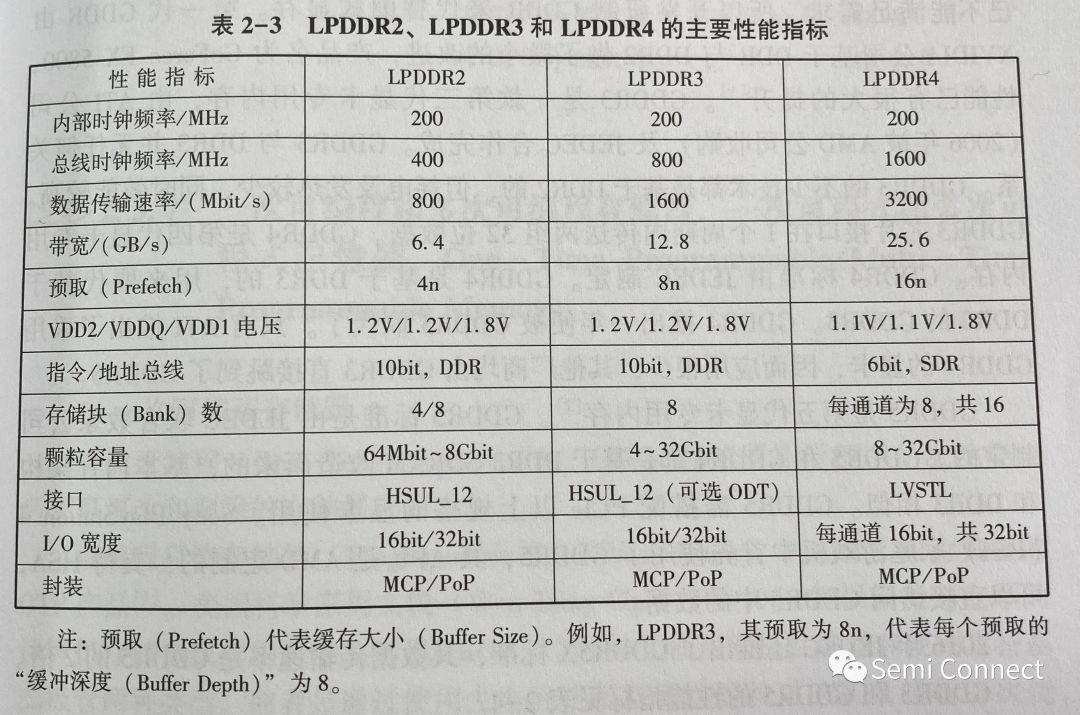

13842 低功耗雙倍速率同步動態(tài)隨機存取存儲器 (Low Power Double Data Rate SDRAM, LPDDR SDRAM)簡稱為 LPDDR,是DDR SDRAM 的一種,由于廣泛用于移動

2023-11-21 09:37:36 1567

1567

DDR是指雙倍數(shù)據(jù)速率的同步動態(tài)隨機訪問內(nèi)存(Double Data Rate Synchronous Dynamic Random Access Memory),它是SDRAM家族的一員。DDR

2023-12-11 09:27:49 2495

2495 DDR加終端匹配電阻和不加信號質(zhì)量的區(qū)別? DDR(雙倍數(shù)據(jù)傳輸速率)是一種常用于計算機內(nèi)存的高速數(shù)據(jù)傳輸技術(shù)。在DDR中,終端匹配電阻和信號質(zhì)量是對于數(shù)據(jù)傳輸穩(wěn)定性至關(guān)重要的兩個方面。下面將詳細

2023-12-29 13:54:22 2012

2012 DDR 代表雙倍數(shù)據(jù)速率double data rate,GDDR 代表圖形雙倍數(shù)據(jù)速率graphics double data rate。

2024-03-17 09:24:53 5146

5146

DDR內(nèi)存通過在時鐘周期的上升沿和下降沿都傳輸數(shù)據(jù),從而實現(xiàn)雙倍數(shù)據(jù)率。這意味著在每個時鐘周期內(nèi),DDR內(nèi)存能夠傳輸兩次數(shù)據(jù),提高了數(shù)據(jù)傳輸效率。

2024-04-27 11:04:00 3426

3426

DDR雙倍數(shù)據(jù)速率技術(shù)是在每個時鐘信號周期內(nèi)傳輸兩次數(shù)據(jù),可以實現(xiàn)以往同步DRAM設(shè)備傳輸速率的兩倍。

2024-05-07 11:05:04 1058

1058 DDR4,即第四代雙倍數(shù)據(jù)率同步動態(tài)隨機存取存儲器(Double Data Rate Synchronous Dynamic Random Access Memory),是計算機內(nèi)存技術(shù)的一個重要

2024-09-04 11:43:34 9814

9814 DDR4(第四代雙倍數(shù)據(jù)率同步動態(tài)隨機存取存儲器)的時鐘頻率和速率之間存在著緊密的關(guān)系,這種關(guān)系對于理解DDR4內(nèi)存的性能特性至關(guān)重要。以下將詳細探討DDR4時鐘頻率和速率之間的關(guān)系,包括它們?nèi)绾蜗嗷ビ绊憽⑷绾魏饬恳约霸趯嶋H應(yīng)用中的表現(xiàn)。

2024-09-04 11:44:27 8379

8379 DDR4內(nèi)存模塊是計算機內(nèi)存技術(shù)的一項重要進步,它是Double Data Rate(雙倍數(shù)據(jù)速率)第四代內(nèi)存技術(shù)的具體實現(xiàn)形式。

2024-09-04 12:35:50 3948

3948 DDR4(Double Data Rate 4th Generation Synchronous Dynamic Random Access Memory,即第四代雙倍速率同步動態(tài)隨機存取存儲器

2024-09-04 12:38:57 3356

3356 DDR4內(nèi)存的傳輸速率是衡量其性能的重要指標(biāo)之一,它直接決定了內(nèi)存模塊在單位時間內(nèi)能夠傳輸?shù)?b class="flag-6" style="color: red">數(shù)據(jù)量。

2024-09-04 12:44:25 6008

6008 無論對于芯片設(shè)計商還是器件制造商來說,DDR內(nèi)存可謂是無處不在——除了在服務(wù)器、工作站和臺式機中之外,還會內(nèi)置在消費類電子產(chǎn)品、汽車和其他系統(tǒng)設(shè)計中。每一代新的 DDR(雙倍數(shù)據(jù)速率)SDRAM

2024-11-13 11:52:57 7406

7406

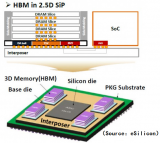

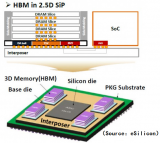

在高性能圖形處理領(lǐng)域,內(nèi)存技術(shù)起著至關(guān)重要的作用。本文介紹兩種主要的圖形內(nèi)存技術(shù):高帶寬內(nèi)存(HBM)和圖形雙倍數(shù)據(jù)速率(GDDR),它們在架構(gòu)、性能特性和應(yīng)用場景上各有千秋。通過對比分析,本文旨在為讀者提供對這兩種技術(shù)的深入理解,幫助在不同的應(yīng)用需求中做出更明智的選擇。

2024-11-15 10:47:59 6059

6059

見的兩種內(nèi)存類型,它們在性能、功耗、容量和兼容性等方面存在顯著差異。 DDR3與DDR4內(nèi)存的區(qū)別 1. 性能 DDR4內(nèi)存條相較于DDR3內(nèi)存條,在性能上有顯著提升。DDR4內(nèi)存條的起始頻率為2133MHz,而DDR3內(nèi)存條的起始頻率為1333MHz。這意味著DDR4內(nèi)存條在數(shù)據(jù)傳輸速度上更快,能夠提供

2024-11-20 14:24:22 11366

11366 DDR內(nèi)存,全稱為Double Data Rate Synchronous Dynamic Random Access Memory(雙倍數(shù)據(jù)速率同步動態(tài)隨機存取內(nèi)存),是一種用于計算機和其他

2024-11-20 14:32:50 4135

4135 在計算機系統(tǒng)中,內(nèi)存是至關(guān)重要的組件之一,它直接影響到數(shù)據(jù)的處理速度和系統(tǒng)的響應(yīng)時間。DDR內(nèi)存作為一種高效的內(nèi)存技術(shù),其數(shù)據(jù)傳輸速度是衡量其性能的關(guān)鍵指標(biāo)。 DDR內(nèi)存技術(shù)概述 DDR內(nèi)存技術(shù)是在

2024-11-20 14:35:28 3496

3496 DDR5內(nèi)存的工作原理詳解 1. DDR5內(nèi)存簡介 DDR5(Double Data Rate 5)是第五代雙倍數(shù)據(jù)速率同步動態(tài)隨機存取存儲器(SDRAM)。它是DDR4的后續(xù)產(chǎn)品,提供更高

2024-11-22 15:38:03 7936

7936 系統(tǒng)總線同步工作,以提高數(shù)據(jù)傳輸效率。 DDR (Double Data Rate) :雙倍速率同步動態(tài)隨機存取存儲器,是SDRAM的后繼者,它通過在時鐘周期的上升沿和下降沿都進行數(shù)據(jù)傳輸來實現(xiàn)雙倍

2024-11-29 14:57:27 5093

5093 DDR5內(nèi)存與DDR4內(nèi)存性能差異 隨著技術(shù)的發(fā)展,內(nèi)存技術(shù)也在不斷進步。DDR5內(nèi)存作為新一代的內(nèi)存技術(shù),相較于DDR4內(nèi)存,在性能上有著顯著的提升。 1. 數(shù)據(jù)傳輸速率 DDR5內(nèi)存的最大數(shù)據(jù)

2024-11-29 14:58:40 5418

5418 DDR內(nèi)存的工作原理 DDR(Double Data Rate)內(nèi)存,即雙倍速率同步動態(tài)隨機存取存儲器,是一種高速的內(nèi)存技術(shù)。它允許在時鐘周期的上升沿和下降沿都傳輸數(shù)據(jù),從而實現(xiàn)數(shù)據(jù)傳輸速率的翻倍

2024-11-29 15:05:16 3598

3598 DDR3、DDR4、DDR5是計算機內(nèi)存類型的不同階段,分別代表第三代、第四代和第五代雙倍數(shù)據(jù)速率同步動態(tài)隨機存取存儲器(SDRAM)。以下是它們之間的性能對比: 一、速度與帶寬 DDR3 :速度

2024-11-29 15:08:28 19722

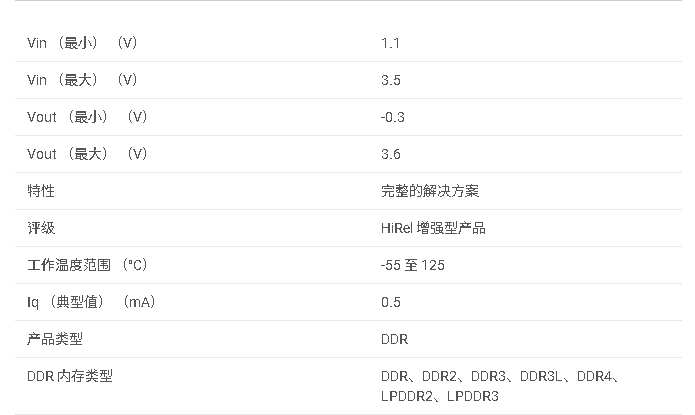

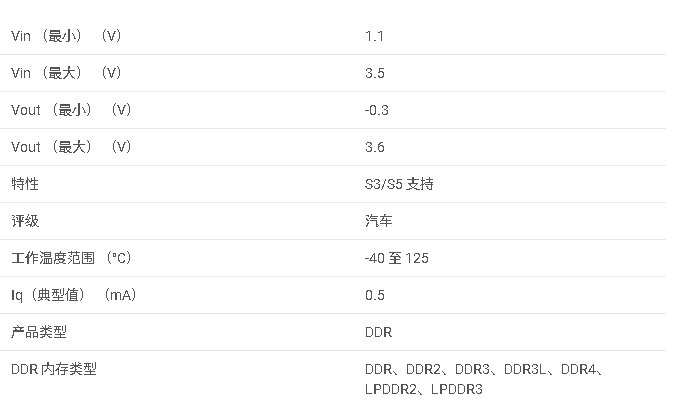

19722 TPS51200A-Q1 器件是一款灌電流和拉電流雙倍數(shù)據(jù)速率 (DDR) 終端穩(wěn)壓器,專為空間受限的低輸入電壓、低成本、低噪聲系統(tǒng)而設(shè)計。

該器件保持快速瞬態(tài)響應(yīng),并且只需要 20 μF

2025-04-25 10:07:15 1056

1056

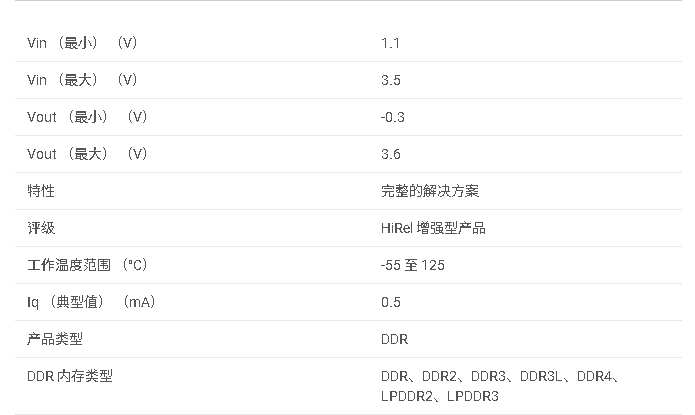

TPS51200-EP 器件是一款灌電流和拉電流雙倍數(shù)據(jù)速率 (DDR) 終端穩(wěn)壓器 專為空間受限的低輸入電壓、低成本、低噪聲系統(tǒng)而設(shè)計 考慮。

TPS51200-EP 保持快速瞬態(tài)響應(yīng),并且

2025-04-26 10:26:35 1335

1335

TPS51200-Q1 器件是一款灌電流和拉電流雙倍數(shù)據(jù)速率 (DDR) 終端穩(wěn)壓器,專為空間受限的低輸入電壓、低成本、低噪聲系統(tǒng)而設(shè)計。

TPS51200-Q1 器件保持快速瞬態(tài)響應(yīng),并且

2025-04-28 16:21:07 852

852

CJTconnDDR系列產(chǎn)品介紹長江連接器有限公司長江連接器·DDR產(chǎn)品?DDR(DoubleDataRate)內(nèi)存的主要特性包括?:雙倍數(shù)據(jù)率?:DDR內(nèi)存的核心特性是其雙倍數(shù)據(jù)率,每個時鐘周期

2025-05-17 23:35:17 930

930

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論