傳統(tǒng)上,雙倍數(shù)據(jù)速率(DDR)技術(shù)依賴于時(shí)序測量,例如建立和保持時(shí)間。隨著標(biāo)準(zhǔn)的發(fā)展和傳輸速率的提高,信號完整性變得更具挑戰(zhàn)性。

對于DDR5,定時(shí)測量已被數(shù)據(jù)和命令地址信號的眼圖模板測量所取代。SPICE 瞬態(tài)模擬器不再是最新 DDR5 和 LPDDR5 內(nèi)存標(biāo)準(zhǔn)的正確方法。

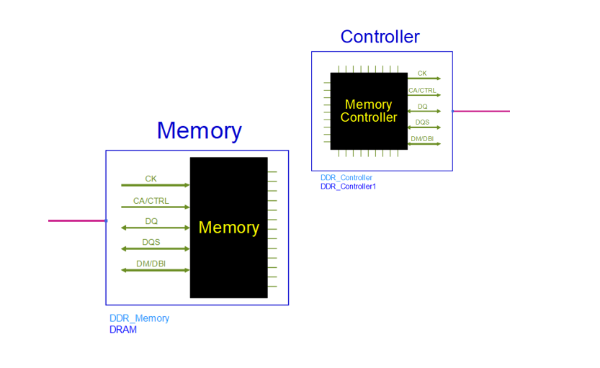

新標(biāo)準(zhǔn)在內(nèi)存控制器和DRAM上增加了均衡(EQ),而傳統(tǒng)的仿真工具無法在這種復(fù)雜性下進(jìn)行建模。

圖1.DDR5 標(biāo)準(zhǔn)在內(nèi)存控制器和 DRAM 上增加了均衡 (EQ)。

輸入/輸出緩沖器信息規(guī)范 (IBIS) 算法建模接口 (AMI) 或 IBIS-AMI 模型支持統(tǒng)計(jì)和時(shí)域通道仿真,并準(zhǔn)確高效地表示芯片內(nèi)部的處理行為。但是,訪問模型可能是新設(shè)計(jì)工作的瓶頸。

要?jiǎng)?chuàng)建可以預(yù)測眼閉合的快速準(zhǔn)確模型,AMI 模型生成器可以通過以下三種方式幫助您進(jìn)行 DDR5 和 LPDDR5 建模。

1. 根據(jù)行業(yè)標(biāo)準(zhǔn)生成模型

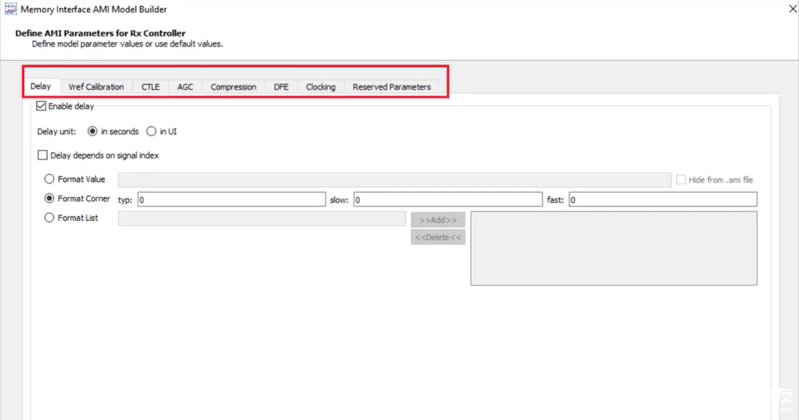

高級 AMI 模型生成器軟件可幫助您使用直觀的向?qū)浇缑鎰?chuàng)建新的 AMI 模型或編輯預(yù)先存在的模型,該界面專為滿足 DDR5 和 LPDDR5 的 JEDEC 規(guī)范而構(gòu)建。這允許您選擇所需的建模選項(xiàng)。

Figure 2. AMI model builder software with an intuitive, wizard-style interface built to meet JEDEC specifications for DDR5.

這些模型是如何配置的?本視頻將引導(dǎo)您完成輸入極端情況、單個(gè)極點(diǎn)零點(diǎn)值和輸入階躍響應(yīng)文件的過程。

2. 自信地預(yù)測大開眼界

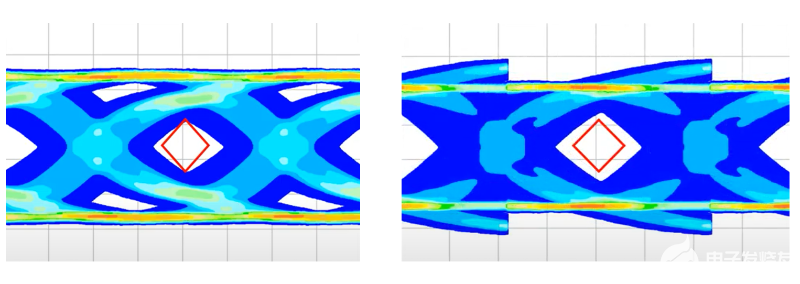

為了確保信號的眼睛打開,應(yīng)用適當(dāng)?shù)木庵陵P(guān)重要。這包括為您的接收器均衡找到最佳的決策反饋均衡 (DFE) 抽頭。

圖3.具有前向時(shí)鐘功能的IBIS-AMI模型通過仿真更好地預(yù)測眼開度測量。

在DDR5速度下,數(shù)據(jù)眼預(yù)計(jì)將關(guān)閉。AMI 模型生成器軟件可以生成具有轉(zhuǎn)發(fā)時(shí)鐘的 AMI 模型。這意味著它將數(shù)據(jù)和數(shù)據(jù)選通波形作為模型的輸入。

這種高級建模功能可確保您的仿真同時(shí)處理抖動(dòng)跟蹤和偏斜調(diào)整,也稱為不匹配的 IO。

如果您的模型必須支持 PathWave ADS 以外的仿真環(huán)境,則可以關(guān)閉雙波形輸入,改用具有虛構(gòu) CDR 的更傳統(tǒng)的模型。此視頻將向您展示如何操作。

3. 簡化您的 AMI 工作流程

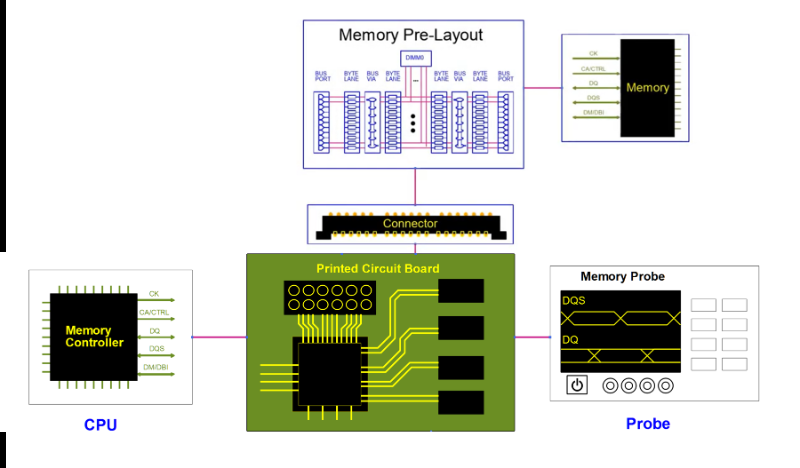

完成IBIS-AMI模型的設(shè)置后,您現(xiàn)在可以發(fā)送文件了。如果您使用的是PathWave ADS 內(nèi)存設(shè)計(jì)器,AMI 生成器會快速生成 4 種文件類型:.ami、.dll、.cfg. 和 .ibs,使模型易于在模擬中使用和使用。

圖4.帶有內(nèi)存控制器和 DRAM 的 PathWave ADS 內(nèi)存設(shè)計(jì)器布局。

如果您是內(nèi)存系統(tǒng)工程師或硅建模工程師,則可以使用最新版本的PathWave ADS快速輕松地生成IBIS-AMI模型。

審核編輯黃昊宇

-

內(nèi)存

+關(guān)注

關(guān)注

9文章

3218瀏覽量

76415 -

AMI

+關(guān)注

關(guān)注

0文章

51瀏覽量

22689 -

DDR5

+關(guān)注

關(guān)注

1文章

478瀏覽量

25782

發(fā)布評論請先 登錄

立锜科技推出完整DDR5服務(wù)器內(nèi)存電源解決方案

DDR5價(jià)格波動(dòng):從暴漲到回調(diào)

Altera面向DDR5與LPDDR5的FPGA解決方案現(xiàn)已實(shí)現(xiàn)量產(chǎn)交付

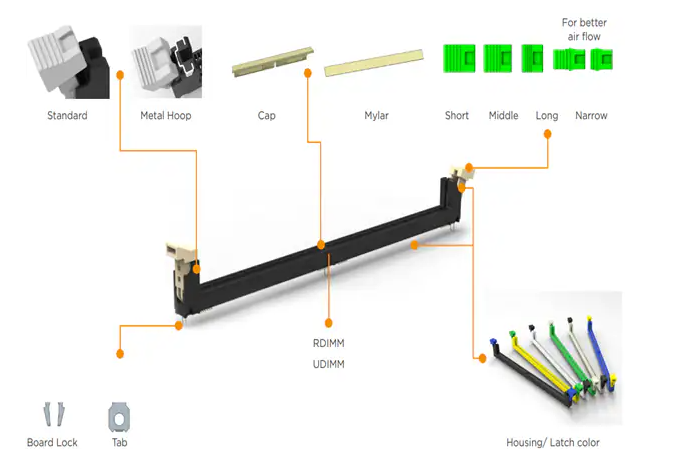

TE Connectivity DDR5 DIMM插槽技術(shù)解析與應(yīng)用指南

DDR5 暫停報(bào)價(jià)只是開始,PCB 行業(yè)的 “芯片依賴癥” 正在爆發(fā)?

如何為蜂鳥添加DDR內(nèi)存擴(kuò)展

DDR5 設(shè)計(jì)指南(一):DDR5 VS LPDDR5

臺式主板DDR5內(nèi)存插槽引腳功能表資料

漲價(jià)!部分DDR4與DDR5價(jià)差已達(dá)一倍!

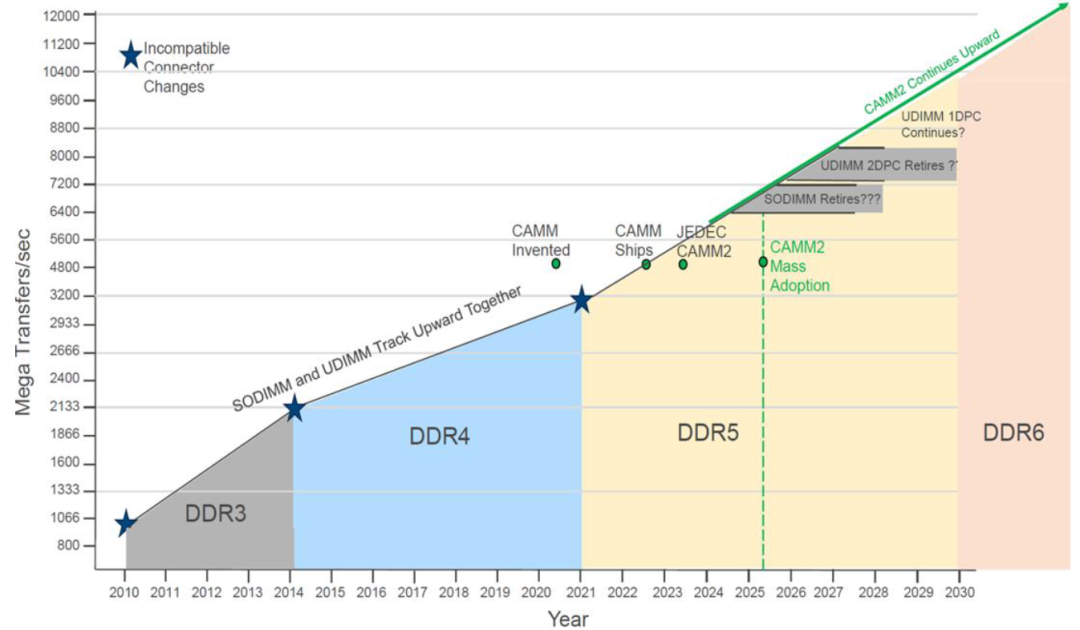

DDR內(nèi)存市場現(xiàn)狀和未來發(fā)展

上海貝嶺推出全新DDR5 SPD芯片BL5118

DDR4漲價(jià)20%,DDR5上調(diào)5%!

Cadence推出DDR5 12.8Gbps MRDIMM Gen2內(nèi)存IP系統(tǒng)解決方案

大型文件秒開、多開任務(wù)流暢——DDR5的優(yōu)勢遠(yuǎn)不止頻率

如何為 DDR5 內(nèi)存接口構(gòu)建 AMI 模型

如何為 DDR5 內(nèi)存接口構(gòu)建 AMI 模型

評論