前情回顧

2DDR3和DDR4的背景技術介紹

2.1DDR3

#DDR3作為第三代雙倍數據速率同步動態隨機存儲器,在內存發展歷程中具有重要地位。它采用了8n預取架構,即每個時鐘周期能夠傳輸8倍于數據位寬的數據量,這使得數據傳輸效率大幅提升 。

在工作電壓方面,標準的DDR3工作電壓為1.5V,隨著技術的發展,衍生出了低電壓版本#DDR3L,其工作電壓降至1.35V 。DDR3的傳輸速率范圍廣泛,從早期的800Mbps到后期的1600Mbps甚至更高,能夠滿足不同性能需求的設備。

在內存容量上,DDR3單顆芯片的容量不斷增大,從最初的幾百兆字節發展到數吉字節,支持更高的系統內存配置。其應用領域也十分廣泛,在早期的臺式機、筆記本電腦以及一些對性能要求不是極高的嵌入式設備中得到了大量應用。

2.2DDR4

#DDR4是在DDR3基礎上發展而來的新一代內存技術,帶來了多項顯著的性能提升。它采用了16n預取架構,相比DDR3的8n預取,每個時鐘周期能夠傳輸更多的數據,理論上數據傳輸速率提升了一倍。

工作電壓進一步降低至1.2V,這不僅使得DDR4的功耗大幅降低,同時也減少了發熱,提高了內存的穩定性和可靠性。在傳輸速率方面,DDR4起步速率就達到了2133Mbps,并且隨著技術的不斷發展,速率還在持續提升,能夠滿足高端服務器、圖形工作站以及高性能嵌入式系統等對數據傳輸速度的極高要求。

DDR4在內存容量上也實現了突破,單顆芯片的容量可以達到16GB甚至更高,為大規模數據存儲和處理提供了堅實的基礎。其先進的存儲架構和電氣性能優化,使得內存的兼容性和穩定性得到了進一步提升。

2.3DDR3L

DDR3L是DDR3的低電壓版本,繼承了DDR3的大部分技術特性,但在功耗方面進行了優化。1.35V的工作電壓使其相比標準DDR3在功耗上降低了約10% - 15% ,這對于對功耗敏感的設備,如筆記本電腦、平板電腦、移動設備以及一些便攜式嵌入式設備來說,具有重要意義,能夠有效延長設備的電池續航時間。

在性能表現上,DDR3L與同頻率的DDR3基本相當,能夠滿足日常辦公、網頁瀏覽、輕度游戲等應用場景的需求。同時,DDR3L在引腳定義和電氣特性上與DDR3保持兼容,這使得設備制造商在設計產品時,可以根據實際需求靈活選擇使用標準DDR3或DDR3L,而無需對#硬件電路進行大幅改動,降低了產品設計和生產成本。

2.4DDR3L和DDR4的技術特點和區別

| 特性 | DDR3L | DDR4 |

|

工作 電壓 |

1.35V | 1.2V |

|

傳輸 速率 |

800–1333Mbps |

1333-1600Mbps (在 RZ/G2L中) 實際應用中更高 |

|

預取 機制 |

8n預取 | 16n預取 |

|

內存 容量 |

單顆芯片容量相對較小,一般在數GB | 單顆芯片容量更大,可達 16GB 甚至更高 |

| 功耗 | 較低,相比標準DDR3有所下降 | 更低,相比 DDR3L 進一步降低,能效比更高 |

|

物理 設計 |

采用傳統的內存模塊設計 | 優化了物理設計,如采用了fly-by拓撲結構,減少了信號干擾,提高了信號完整性 |

|

電氣 性能 |

在高頻下信號穩定性相對較弱 | 電氣性能優化,能夠更好地支持高速數據傳輸 |

|

應用 場景 |

對功耗有一定要求,但性能需求不是極高的設備,如便攜式移動設備、中低端嵌入式系統 | 對性能和功耗都有較高要求的設備,如高端服務器、圖形工作站、高性能嵌入式系統 |

從技術特點和區別可以看出,DDR4在性能和功耗方面都優于DDR3L,但其成本相對較高;而DDR3L則在性價比和功耗控制上具有一定優勢,適用于對成本敏感且性能要求適中的應用場景。

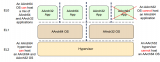

3DDR配置工具使用流程(以瑞薩RZ/G2L為例)

3.1配置工具介紹

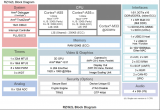

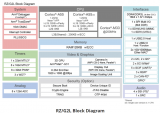

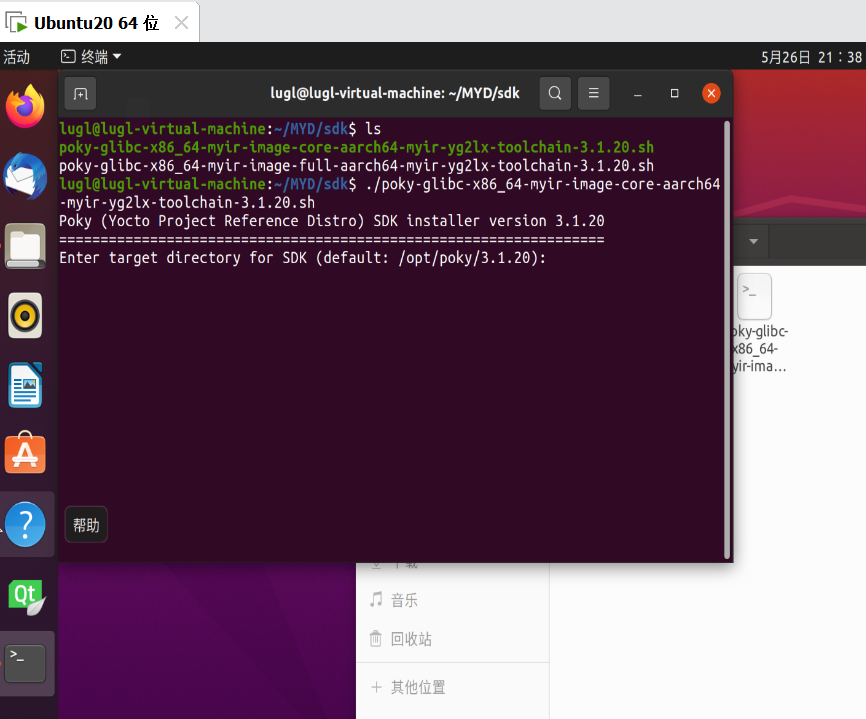

RZ/G2L的DDR配置工具全稱為“RZG2L_G2UL_Five_A3UL_DDR_config_generation_tool_v3.0.1.xlsm”,它是一款基于Excel的工具,通過特定的表格設置和參數配置,生成DDR控制器初始化所需的代碼文件,即param_mc.c和param_swizzle.c 。

該工具適用于RZ/G2L - LC - UL系列MPU處理器,由于這些處理器的DDR Memory controller和PYH相同,因此配置工具是一樣的。最新版本是v3.0.1。

在實際應用中,生成的配置文件(param_mc.c 和param_swizzle.c)在Flash - writer和trusted-firmware-a源碼工程中放置的路徑有所不同,但內容是一致的。需要根據最終選擇的Topolog的Connection和Condition進行重命名。例如,param_mc.c需重命名為param_mc_{Connection#}_{Condition#}.c,param_swizzle.c需重命名為param_swizzle_{Topology#}.c 。

在Flash – writer源碼工程中,文件路徑為

ddr/${PLAT}/param_mc{Connection#}_{Condition#}.c

ddr/common/param_swizzle{Topology#}.c;

在trusted-firmware-a源碼工程中,文件路徑為plat/renesas/rz/soc/${PLAT}/drivers/ddr/param_mc{Connection#}_{Condition#}.c

plat/renesas/rz/common/drivers/ddr/param_swizzle{Topology#}.c 。

結語

敬請期待

精彩尚未結束,下一期我們將深入探討——DDR配置工具使用流程(以瑞薩RZ/G2L為例),敬請期待!

-

存儲器

+關注

關注

39文章

7746瀏覽量

172005 -

瑞薩

+關注

關注

37文章

22500瀏覽量

91013 -

MPU

+關注

關注

0文章

456瀏覽量

51463

發布評論請先 登錄

基于瑞薩64位MPU RZ/G2L的uboot串口多波特率支持介紹

瑞薩MCU方案:瑞薩RZ/G2L Bootloader單獨編譯方法詳解

基于瑞薩電子RZ/G2L的FET-G2LD-C核心板和OK-G2LD-C開發板評測

瑞薩RZ/G2L MPU的DDR配置(2)

瑞薩RZ/G2L MPU的DDR配置(2)

評論