LVDS 采用了差分傳輸機制,每一 LVDS 信號使用兩條走線。 這兩條走線之間的電壓差定義了 LVDS 信號值。

2020-03-22 15:54:00 4017

4017 本篇主要介紹LVDS、CML、LVPECL三種最常用的差分邏輯電平之間的互連。由于篇幅比較長,分為兩部分:第一部分是同種邏輯電平之間的互連,第二部分是不同種邏輯電平之間的互連。 下面詳細介紹第一部分

2020-12-20 11:39:59 41058

41058

項目涉及5片FPGA之間的多機通信,1片主FPGA,4片從FPGA,5片FPGA采用星形連接的拓撲結構。4個從機與主機之間通信接口采用基于LVDS_33的差分IO接口標準,以滿足高速率,抗干擾

2022-12-22 14:05:33 4075

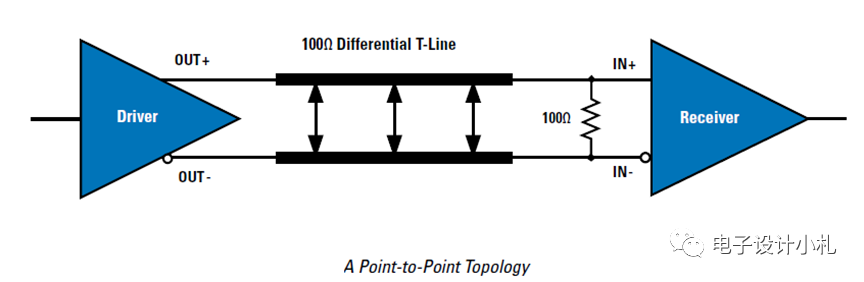

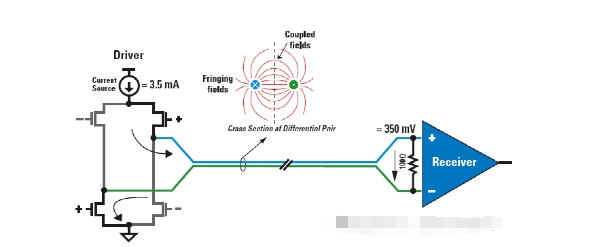

4075 LVDS是一種低擺幅的差分信號技術,它使得信號能在差分PCB線對或平衡電纜上以幾百Mbps的速率傳輸,其低壓幅和低電流驅動輸出實現了低噪聲和低功耗。

2023-10-02 16:44:00 2571

2571

M-LVDS:英文全稱Multipoint-Low-Voltage DifferentialSignaling,中文全稱:多點低電壓差分信號,其主要目的是將點對點的LVDS延申用于解決多點應用問題,因此其除了LVDS的相關低功耗、差分、抗干擾等特點外,其驅動器輸出的強度更高,共模范圍更廣。

2023-11-22 16:29:53 16274

16274

LVDS: 英文全稱Low-Voltage Differential Signaling,中文全稱:低電壓差分信號,其基本特點即:“低電壓”、“差分”,引申特點“高速”、“低功耗”、“抗干擾”、“低輻射”。

2023-11-22 16:31:05 25444

25444

LVPECL電平的差分擺幅較大(典型值約800mV),共模電壓較高(約1.3V-1.9V),需外部端接電阻匹配;而LVDS差分擺幅較小(350mV),共模電壓較低(約1.2V),且LVDS接收端內置端接電阻?。

2025-03-12 17:50:35 1883

1883

DDR哪幾根線要做差分阻抗,控制在多少ohms也要等長,要控制多少ohms

2014-12-26 10:46:04

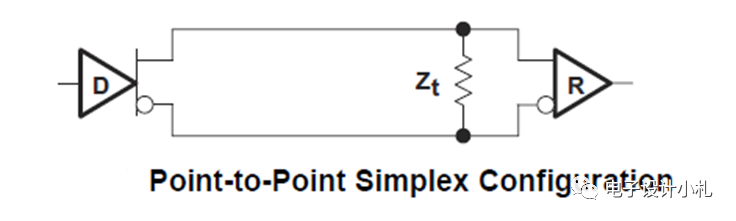

數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也

2011-02-23 09:55:17

LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗

2019-06-24 05:00:52

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術,LVDS 數據線連接廣泛應用于高速數據信號傳輸,例如

2020-10-30 16:07:34

LVDS:Low-Voltage Differential Signaling 低電壓差分信號。一種信號傳輸模式,是一種電平標準,LVDS接口又稱RS-644總線接口,是一種數據傳輸和接口

2016-04-15 16:13:33

ADN4621是否只支持差分LVDS信號隔離?是否還能支持單端的LVDS(單線LVDS)信號隔離?比如POC攝像頭的單線LVDS信號。

2024-05-27 07:05:51

今天給大俠帶來基于FPGA的LVDS屏幕接口應用,話不多說,上貨。

什么是LVDS,LVDS的全稱是Low-Voltage Differential Signaling ,即低電壓差分信號

2023-06-05 17:31:08

應用的需要。此技術基于ANSI/TIA/EIA-644 LVDS 接口標準。LVDS 技術擁有 330mV 的低壓差分信號 (250mV MIN and 450mV MAX) 和快速過渡時間。 這可以讓

2019-12-11 09:51:59

大家好假設我有一個IO信號Ain verilog設計。我想用它來使用差分信號標準LVDS。我是否必須在我的verilog代碼中使用IOBUFDS?或者有一種更簡單的方法,只需在ucf中將A設置為

2019-01-18 07:03:58

Z-turn底部的DIP擴展接口支持LVDS差分輸入輸出嗎?

2015-04-03 14:50:29

出來的cml信號在還原成hdmi信號,接到顯示器上。現在有幾個問題:

1,hdmi是什么電平?第一次接觸,hdmi信號里有幾對差分還有幾個單端的,差分的信號是不是cml電平?

2,如果差分的是cml電平

2024-12-24 06:34:16

的電壓放大器,接下來用一個I-V轉換單元去驅動數字邏輯。使用差分電流傳感電路的一個直接優勢是非常低的電壓擺幅,因而減少電流尖峰和降低EMI。有工作記載已經顯示,電流模式信號受負載電容的影響遠遠小于電壓模式

2019-04-16 07:00:03

Low Voltage Differential Signaling,英文簡稱:LVDS,中文全稱:低壓差分信號技術接口,是一種為了克服TTL電平方式傳輸寬帶高碼率數據時功耗大、EMI電磁干擾等缺點

2020-12-29 13:46:50

我們在這里使能差分信號,點擊OK生成IP核。AD9684觸發時鐘配置完后,我們配置該芯片的接收器,由于這里AD9684是并行DDR模式的LVDS數據,所以我們需要使用的Xilinx selectIO

2019-12-06 15:33:22

)。 減小視頻干擾的一種方案是用數字信號取代模擬信號,視頻信號線本身不能產生干擾。已經證明,低壓差分信號(LVDS)能夠為數字視頻傳輸提供最合理的連接。小信號幅度(0.35V)、差分結構使LVDS傳輸線具有

2019-05-05 09:29:30

的特點是每對信號線(正負極性)之間的電壓差是信號的有效部分,而不是單獨的電平。這種差分傳輸方式使得LVDS接口在長距離傳輸時能夠保持較高的抗干擾能力和數據傳輸速率。它的主要工作原理就是將發送端將輸入信號

2025-08-29 15:52:59

我正在使用Artix 7 fpga。我沒有2.5V IO庫,所以我不能使用LVDS輸出。有沒有人有使用差分HSTL與LVDS接口的經驗? TI建議為接口提供交流耦合終端,有何評論?見附件。

2020-07-30 10:49:04

大家好,我試圖在兩個FPGA(Spartan 6)之間運行邊界掃描互連測試。但是,某些信號有LVDS緩沖器。有沒有辦法使用JTAG提供LVDS信號的激勵/測量響應?AR#6664規定必須將后配置

2019-08-06 11:00:44

接口,因此說到LVDS接口時無特殊說明都是指液晶屏LVDS接口),它們的主要信號成分都是5組差分對,其中1組時鐘CLK,4組DATA(MIPI DSI接口中稱之為lane),它們到底有什么區別,能直接

2016-06-13 20:18:24

和端口之間的矛盾;而低壓差分信號LVDS(Low-Voltage Differential Signaling)接口作為一種新型的高速串行。低噪聲的數據傳輸接口,廣泛應用于視頻傳輸領域,實現USB

2018-11-22 11:24:30

大家好,我開發了DDR2內存和高速ADC 500Mpbs(2 ADC)到Spartan6 LX25器件。我想知道銀行分配的最佳選擇,因為接口都是高速且需要時鐘定時至關重要。根據MIG的推薦,DDR

2019-07-12 06:30:06

ADS6148有14位數據寬度,采用DDR LVDS接口傳輸數字數據,一共有7對差分信號。我在XILINX的SPARTAN6數據手冊中,找到了明確的支持DDR LVDS和SDR LVDS接口的描述

2024-12-17 07:00:59

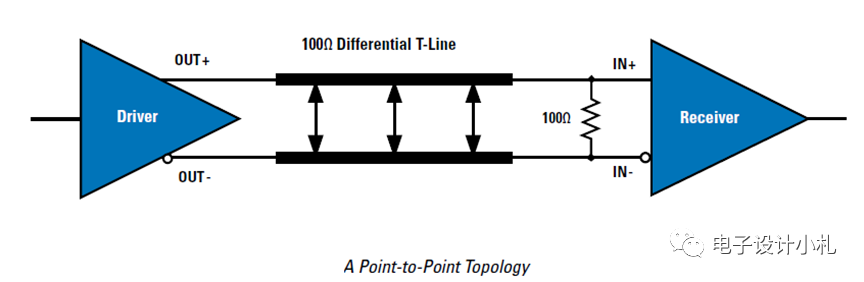

DS90UB913Q-Q1和DS90UB914Q-Q1采用STP的方式始終調不通,差分LVDS信號從913上出來后串了0.1uf的電容,然后進入914,這種連接方式是否正確,再LVDS差分線是是否要串上100Ω的電阻?謝謝!

2019-06-19 08:08:08

咨詢超高速比較的是否有差分輸入,LVDS輸出的?關于差分輸入的如何實現過零比較。

2018-08-07 08:13:23

本文將介紹如何通過一個差分接口來延長串行外設接口 (SPI) 總線,而這可以應用在支持遠程溫度或壓力傳感器的系統的設計。 在SPI應用中,主控器件和受控器件間的距離相對較近,而信號也通常不會傳遞到

2019-06-13 05:00:02

基于低電壓差分信號(LVDS)的高速信號傳輸

2010-12-17 17:21:46 40

40 什么是LVDS?現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應

2007-09-26 11:45:09 6411

6411 什么是lvds信號

LVDS:Low Voltage Differential Signaling,低電壓差分信號。LVDS傳輸支持速率一般在155Mbps(大約為77MHZ)以上。LVDS是一種低擺幅的差分信號

2008-10-16 13:49:11 9059

9059 LVDS信號電平特性

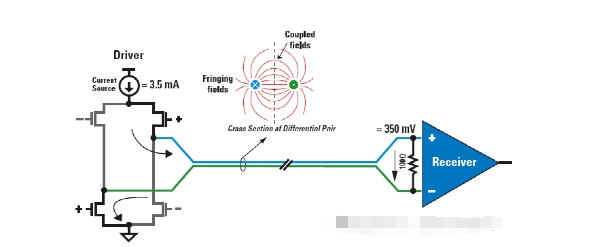

LVDS物理接口使用1.2V偏置電壓作為基準,提供大約400mV擺幅。LVDS驅動器由一個驅動差分線對的電流源組成(通常電

2008-10-16 13:50:25 17544

17544 LVDS差分信號抗噪特性

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,在發送側,可以形象理解為:

2008-10-16 13:53:16 1983

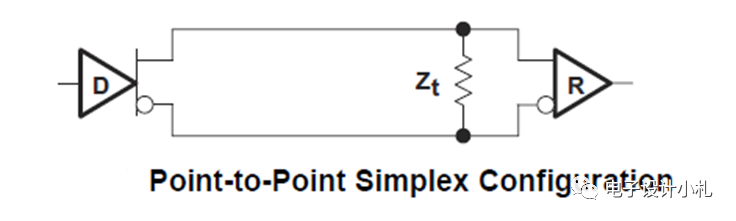

1983 摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-04-24 16:05:19 2002

2002

摘要:汽車視頻應用中,降低視頻干擾的途徑是用數字信號替代模擬信號。最有效的視頻傳輸方案是采用低電壓差分信號(LVDS)接口,因為它具有較低的信號幅度(0.35V)和差分架構,可

2009-04-25 09:22:52 2210

2210

摘要:ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時鐘分配、點對點以及多點之間的信號傳輸。本文描述了使用LVDS將高速通訊信號分配到多個目的端的方法。

2009-05-01 11:14:27 1918

1918

摘要:汽車視頻應用中,降低視頻干擾的途徑是用數字信號替代模擬信號。最有效的視頻傳輸方案是采用低電壓差分信號(LVDS)接口,因為它具有較低的信號幅度(0.35V)和差分架構,可

2009-05-02 10:47:39 2044

2044

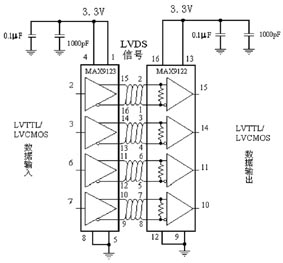

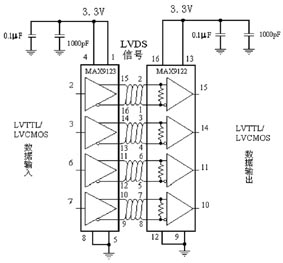

LVDS接口電路及設計

LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓

2009-06-16 11:19:26 6092

6092

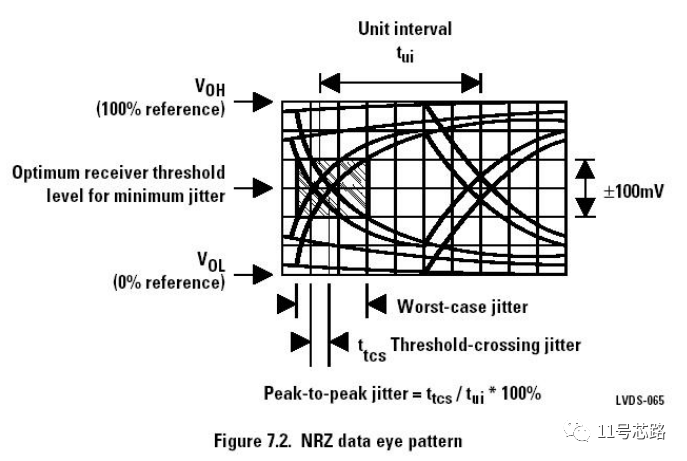

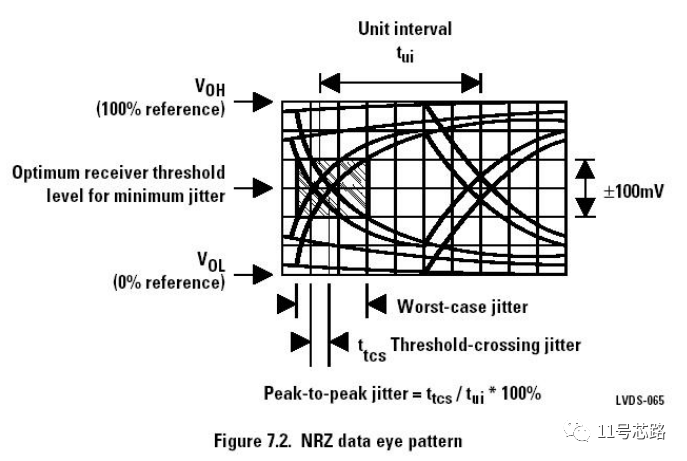

低壓差分信號(LVDS)是一種低壓、差分信號傳輸方案,主要用于高速數據傳輸。根據 ANSI/TIA/EIA-644 規范中的定義,它是一種最為常見的差分接口。這種標準只對適合于 LVDS 應用的驅動

2010-06-10 09:59:48 2560

2560

隨著數字電路數據量的提高,數據的傳輸速率也越來越快,LVDS(低壓差分信號)標準越來越多的應用在FPGA和ASIC器 件中。文章對LVDS信號的特點進行了分析,說明了PCB設計中差分走線的注意事項并結合實際應用設計了一塊LVDS接口板。 關鍵詞: LVDS; PCB設計;接口;阻抗

2011-02-23 09:54:03 341

341 LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。LVDS即低電壓差分信號,這種技術的核心是采用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點

2011-06-02 09:30:41 12703

12703

LVDS,即Low Voltage Differential Signaling,是一種低壓差分信號技術接口。它是美國NS公司(美國國家半導體公司)為克服以TTL電平方式傳輸寬帶高碼率數據時功耗大、EMI電磁干擾大等缺點而研

2012-07-19 16:01:53 6477

6477

什么是LVDS?

現在的液晶顯示屏普遍采用LVDS接口,那么什么是LVDS呢?

LVDS(Low Voltage Differential Signaling)即低壓差分信號傳輸,是一種滿足當今高性能數據傳輸應用的新型技術。

2016-06-17 15:42:45 16

16 (Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 66

66 來源:羅姆半導體社區 差分放大電路在數顯表應用很多,昌暉儀表以圖文形式簡單介紹差分信號、單端信號的概念及差分放大電路的作用,方便大家對差分放大電路相關知識有所了解。 1、什么是單端信號?什么是差分信號

2022-11-17 15:56:35 5460

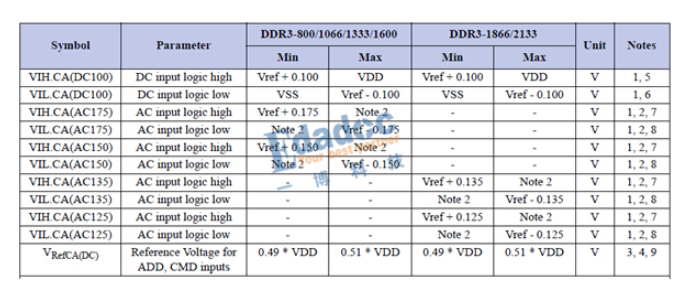

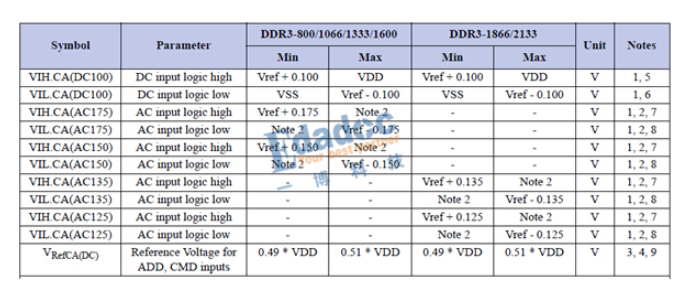

5460 通常,DDR設計完成之后 ,對信號質量并沒有一個完全確定的概念,需要我們通過仿真和測試的手段去判斷和驗證。而此時,往往我們拿到的就是一個波形,測試波形或者仿真波形,該如何去判斷其信號質量,參照的標準

2021-04-09 10:04:19 6961

6961

什么是LVDS,LVDS的全稱是Low-Voltage Differential Signaling ,即低電壓差分信號。LVDS可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點。

2020-11-01 10:03:18 11519

11519

差分放大電路在數顯表應用很多,本文以圖文形式簡單介紹差分信號、單端信號的概念及差分放大電路的作用,方便大家對差分放大電路相關知識有所了解。 1、什么是單端信號?什么是差分信號?單端傳輸是指用一根

2020-12-03 22:48:00 34

34 信號傳輸應用常用的方法是低壓差分信號傳輸(LVDS)。這涉及到串行數據傳輸的既有接口標準 (TIA/EIA-644),除了極佳的節能特性和高達幾 Gbps 的數據速率潛力之外,它還具有很高的抗擾度

2020-12-15 02:01:55 1025

1025 wp02-將凌力爾特公司的DDR LVDS ADC與Altera Stratix IV FPGA接口

2021-05-23 11:13:28 1

1 。這些良好特性可歸因于內部使用的電流控制或驅動器模塊的限流功能(最大3 mA)。信號差分電壓僅為 20 mV。但是,它隨后在接收器側被放大回 300 mV(差分)的邏輯電平。由此獲得的好處包括電磁干擾 (EMI) 極其低、開關速度極其快等。 LVDS接口常常與控制和調節系

2021-05-24 14:05:26 3544

3544

許多人認為只有在探測差分信號時才使用差分探頭。在這里PRBTEK告訴工程師們,其實在探測單端信號時,也可以使用差分探頭,它將為您節省大量時間和金錢,并提高測量的準確性。最大限度地利用差分探頭,獲得

2021-12-07 11:44:20 1245

1245 LVDS(Low Voltage Differential Signal)即低電壓差分信號。

2022-07-03 15:20:13 5609

5609 探頭有很多種,差分探頭在開關電源中的應用非常普遍,差分探頭差分信號的常用測量方法如下。

2022-10-14 15:40:24 6058

6058 項目涉及5片FPGA之間的多機通信,1片主FPGA,4片從FPGA,5片FPGA采用星形連接的拓撲結構。4個從機與主機之間通信接口采用基于LVDS_33的差分IO接口標準,以滿足高速率,抗干擾

2022-12-23 06:15:04 1871

1871 LVDS (Low Voltage Differential Signaling)是一種小振幅差分信號技術,它使用非常低的幅度信號 (250mV~450mv)通過一對平行的PCB走線或平衡電纜傳輸數據是一種專業的低電壓差分信號

2023-04-06 09:46:43 3265

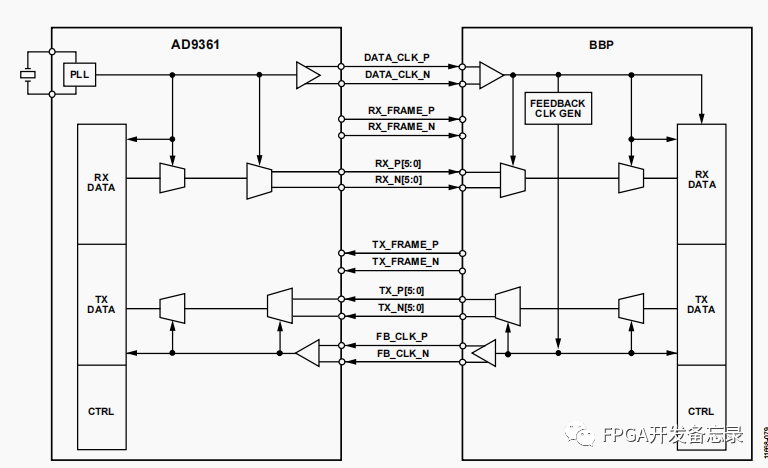

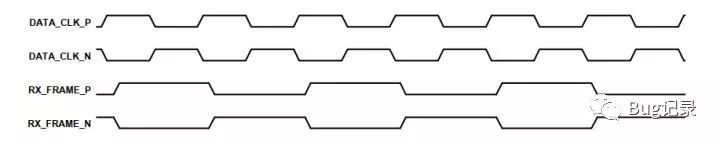

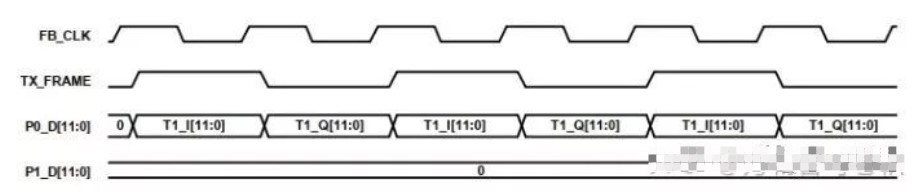

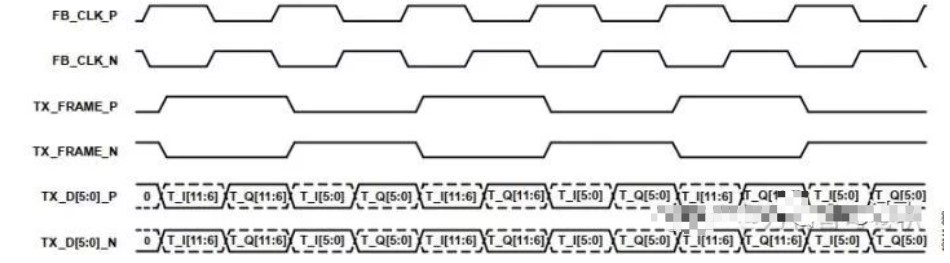

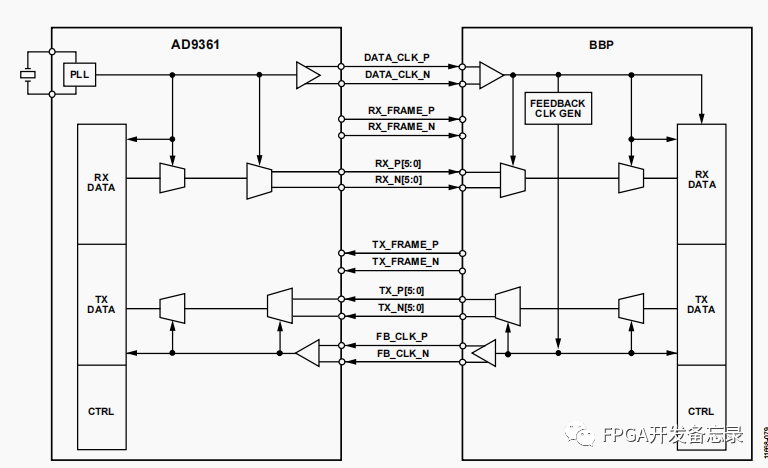

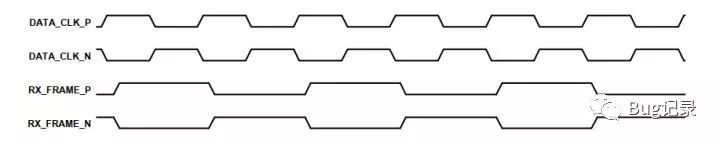

3265 接下來將介紹AD9361數據路徑在低電壓差分信號(LVDS)模式下運行。AD9361數據接口使用并行總線(P0和P1)在AD9361和BBP之間傳輸數據樣本。

2023-04-25 15:51:25 9580

9580

最近調試芯片遇到一個選擇題,需要決定數據接口的接口標準,是選用LVDS差分接口還是CMOS單端接口。

2023-06-16 09:55:33 4052

4052

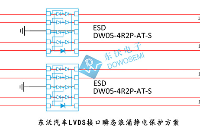

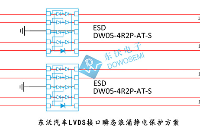

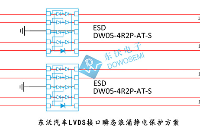

都知道,汽車工作環境比較惡劣,為此,在設計高速低電壓差分信號(LVDS)接口系統時,應選用正確的電路保護元件免受瞬態威脅并滿足現代汽車的安全性和可靠性。事實證明,在 LVDS 差分線路上,選用瞬態

2023-06-08 09:36:30 3802

3802

都知道,汽車工作環境比較惡劣,為此,在設計高速低電壓差分信號(LVDS)接口系統時,應選用正確的電路保護元件免受瞬態威脅并滿足現代汽車的安全性和可靠性。事實證明,在 LVDS 差分線路上,選用瞬態

2023-06-08 09:43:37 2994

2994

LVDS傳輸的是什么信號?判斷LVDS信號正常的方法 一、LVDS傳輸的是什么信號? LVDS是一種低電壓差分信號,有兩種電壓狀態,即高電平和低電平,它類似于RS485協議。LVDS信號作為一種數字信號

2023-10-18 15:38:13 7368

7368 什么叫做LVDS信號?請問TTL信號與LVDS信號有什么區別? LVDS信號 LVDS(Low Voltage Differential Signaling)又稱低壓差分信號傳輸技術,是一種采用差分

2023-10-18 15:38:18 4101

4101 組成部分。 由于數據的傳輸速率越來越快,傳統的單端信號傳輸方式不再適用,因為它存在著信號失真、干擾和耗能等問題。而LVDS則是一種差分信號傳輸技術,通過將信號分為正負兩個信號同時傳輸,可以避免上述問題的出現。 在LVDS接口中,時鐘脈沖信號與數據信號是同時傳輸的。時鐘信號用來指示數據信號的

2023-10-18 15:38:20 2320

2320 GMSL中,數據傳輸使用千兆位電平差分信號,而在LVDS中,則是使用低壓差分信號。GMSL使用差分電平較高,能夠提供更大的數據傳輸速度。 數據

2023-12-08 14:13:05 10313

10313 LVDS(Low Voltage Differential Signaling)接口是一種低電壓差分信號傳輸LVDS(Low Voltage Differential Signaling)接口是一種

2024-01-18 11:20:09 3381

3381 差分探頭是一種常用的測試工具,用于測試差分信號。差分信號是指由兩個相反的信號組成的信號,其特點是具有高抗干擾能力和低噪聲。差分探頭通常用于測試高速數字信號、模擬信號和射頻信號等應用場景。那么,差分

2024-05-21 09:57:23 1158

1158

電子發燒友網站提供《低壓差分信號(LVDS)在LED燈墻中的應用.pdf》資料免費下載

2024-08-30 09:23:24 0

0 LVDS(Low-Voltage Differential Signaling,低電壓差分信號)接口確實需要驅動,但其驅動方式與其他常見的接口有所不同。 一、LVDS接口概述 LVDS接口是一種

2024-10-06 15:06:00 4020

4020

LVDS(Low Voltage Differential Signaling,低電壓差分信號)接口是一種數據傳輸和接口技術,以下是對其用途、應用以及連接方法的介紹: 一、LVDS接口的用途

2024-11-21 16:04:44 8943

8943 LVDS(Low Voltage Differential Signaling,低電壓差分信號)接口和HDMI(High-Definition Multimedia Interface,高清多媒體

2024-11-21 16:06:50 4098

4098 LVDS(Low Voltage Differential Signaling)是一種高速串行通信技術,廣泛應用于連接顯示器和圖形處理器等設備。LVDS接口通過小電壓擺幅的差分信號傳輸數據,以減少

2024-11-21 16:08:18 3356

3356 LVDS(Low-Voltage Differential Signaling,低電壓差分信號)接口因其低功耗、低電磁干擾和長傳輸距離等特點,在多種設備中得到了廣泛應用。以下是對LVDS接口適用設備

2024-11-21 16:11:08 4058

4058 LVDS接口是一種低壓差分信號技術,它通過小電壓擺幅和差分信號傳輸數據,以減少功耗和電磁干擾。LVDS接口廣泛應用于筆記本電腦、監視器和高端電視等顯示設備中,因為它能夠提供高質量的視頻信號傳輸,同時

2024-11-21 16:13:39 2667

2667 LVDS(Low-Voltage Differential Signaling,低電壓差分信號)接口能夠實現高分辨率顯示,主要得益于其高效的差分信號傳輸方式和在數據傳輸方面的優勢。以下是對LVDS

2024-11-21 16:23:27 1930

1930 差分平衡電平接口,作為一種先進的信號傳輸技術,它通過一對接線端A和B的相對輸出電壓(uA-uB)來精確傳遞信號,這一獨特設計使得差分平衡電平接口在復雜噪聲環境中展現出卓越的性能。 一、差分平衡電平

2025-02-04 16:34:00 1321

1321 MAX9374和MAX9374A是為電訊應用而設計的2.0GHz差分LVPECL到LVDS電平轉換器,具有250ps的傳輸延遲。差分輸出信號符合ANSI TIA/EIA-644 LVDS標準。輸入

2025-05-19 10:43:28 743

743

) 差分信號是由兩個幅度相等、相位相反的信號組成,其信息通過兩者的差值傳遞。差分探頭的設計初衷就是優化這類信號的測量,典型應用包括: 高速數字總線:如 USB(尤其是 USB 3.0 及以上)、HDMI、LVDS(低壓差分信號,常用于顯示屏

2025-08-05 13:02:09 733

733 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速率、低功耗和低電磁干擾等優勢,得到了廣泛應用。德州儀器(TI)的SN65LVDS33、SN65LVDT33、SN65LVDS

2025-11-26 16:16:48 521

521 高速差分接收器SN65LVDS33和SN65LVDS34:特性、應用與設計要點 在當今高速數據傳輸的時代,差分信號傳輸技術因其抗干擾能力強、傳輸速率高等優點,被廣泛應用于各種電子系統中。德州儀器

2025-12-24 17:40:06 509

509 高速差分接收器SN55LVDS33-SP的特性與應用解析 在電子設計領域,高速差分接收器的性能對于數據傳輸的穩定性和效率至關重要。今天,我們就來深入探討德州儀器(TI)的SN55LVDS

2025-12-26 09:25:12 284

284 深入剖析DS90LV011AH:高性能LVDS差分驅動器的設計與應用 在電子設計領域,高速、低功耗的數據傳輸需求日益增長。LVDS(低電壓差分信號)技術因其出色的性能,在眾多應用場景中得到廣泛應用

2025-12-29 11:05:10 125

125 SN65LVDS20與SN65LVP20:高速差分收發神器揭秘 在高速信號處理的領域中,差分信號的處理與傳輸一直是工程師們關注的焦點。德州儀器(TI)推出的SN65LVDS20和SN65LVP20這

2025-12-29 16:00:33 132

132 高速差分接收器SN65LVDS348/352系列:設計與應用指南 在電子工程領域,高速數據傳輸和可靠的信號處理一直是關鍵挑戰。德州儀器(TI)的SN65LVDS348、SN65LVDT348

2025-12-30 16:55:06 385

385 高速差分接收器SN65LVDS系列:設計與應用全解析 在高速數據傳輸的領域中,差分接收器是實現高效、穩定信號接收的關鍵組件。今天我們要深入探討的是德州儀器(Texas Instruments

2025-12-30 17:00:03 398

398 高速差分接收器:SN65LVDS系列的卓越性能與應用 在電子設計領域,高速差分接收器一直是實現高效數據傳輸的關鍵組件。今天,我們將深入探討德州儀器(TI)的SN65LVDS

2025-12-31 11:10:02 131

131 高速差分接收器SN65LVDS系列:特性、應用與設計要點 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速率、低功耗和抗干擾能力強等優勢,得到了廣泛應用。德州儀器(TI

2025-12-31 11:10:06 140

140 高速差分接收器SN65LVDS系列:性能亮點與應用指南 在電子設計領域,高速差分接收器對于實現可靠的數據傳輸至關重要。TI推出的SN65LVDS32B、SN65LVDT32B

2025-12-31 11:10:16 141

141 高速差分接收器SN65LVDS/T系列:特性、應用與設計要點 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速率、低功耗和抗干擾能力強等優勢,得到了廣泛應用。德州儀器(TI

2025-12-31 11:20:05 133

133 高速差分接收器SN65LVDS/T系列:性能與應用解析 引言 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速、低功耗和抗干擾能力強等優勢,得到了廣泛應用。德州儀器(TI

2025-12-31 11:20:09 162

162 解析高速差分接收器SN65LVDS/T系列:LVDS技術的卓越之選 在高速數據傳輸領域,低電壓差分信號(LVDS)技術憑借其高速、低功耗、低噪聲等優勢,成為了眾多工程師的首選。德州儀器(TI

2025-12-31 11:20:12 128

128

電子發燒友App

電子發燒友App

評論