廉價的雙倍數(shù)據(jù)速率(DDR)內(nèi)存(以及DDR2和DDR3等后來的版本)為臺式機(jī)和筆記本電腦的工作內(nèi)存提供了支柱。通過在脈沖序列的前沿和后沿上為存儲器提供時鐘,存儲器吞吐量加倍,而功耗僅略微增加。但是,為了充分利用這種吞吐量并避免這種高頻方案的常見問題,例如,無意中觸發(fā)邏輯器件的振鈴和反射,總線終端電路需要自己的電源。為了有效地工作,該電源必須提供主存儲器芯片組電源的輸入電壓的一半,同時能夠提供源電流和吸收電流。

本文介紹DDR存儲器電源的獨特需求,然后檢查主要供應(yīng)商的一些專用電源控制器,以減輕設(shè)計工程師的挑戰(zhàn)。

DDR的特殊要求

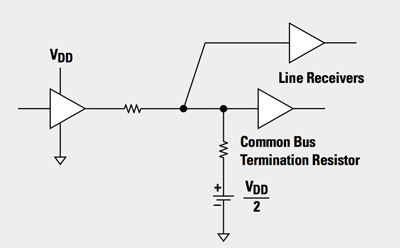

圖1說明了一種用于計算機(jī)時鐘分配網(wǎng)絡(luò)的流行終端方案,旨在防止可能無意中觸發(fā)連接到總線的邏輯設(shè)備的虛假振鈴和反射。這種拓?fù)浣Y(jié)構(gòu)的另一個優(yōu)點是,與簡單地通過直接接地的電阻器終止線路相比,它將時鐘網(wǎng)絡(luò)中消耗的功率減半(當(dāng)總線高一半時,而其他時間則低)。權(quán)衡要求額外的電源產(chǎn)生VDD/2。

圖1:在公共總線終端電阻線上增加第二個電源,使電阻上的平均功耗減半(德州儀器公司提供)。

終端電阻連接到第二電源電壓(VTT),該電壓等于主電源電壓(VDD)的一半。連接第二個電壓的結(jié)果是,無論電源電壓如何,終端電阻的功耗都是恒定的,并且等于VTT(或VDD/2)平方除以終端電阻(來自P =V2/R)。但是,對二次電源的要求是不尋常的。除電源電壓(VTT)為主電源電壓(VDD)的一半外,器件還需要提供源電流和吸收電流(圖2)。當(dāng)VDD為低電平時,電流從VTT電源流入驅(qū)動器。但是,當(dāng)VDD為高電平時,電流從驅(qū)動器流向VTT電源。同樣重要的是,VTT電源在狀態(tài)之間平滑切換,以避免增加功耗的低效率。

圖2:DDR存儲器VTT電源的工作模式。在左側(cè),器件以降壓模式工作,并在右側(cè)提供電流,作為升壓電源和吸收電流(德州儀器公司提供)。

同步開關(guān)DC/DC穩(wěn)壓器通常用于VTT電源,因為它比線性低壓差穩(wěn)壓器(LDO)更有效(盡管一些設(shè)計人員更青睞LDO,因為它更容易融入到LDO中。電源設(shè)計)。然而,在這兩種不同的工作模式下保持高效率(低功耗)和良好的瞬態(tài)響應(yīng)是一項挑戰(zhàn)。

在同步開關(guān)降壓穩(wěn)壓器中,精確控制從高端MOSFET導(dǎo)通點到低端器件導(dǎo)通點的過渡。可以幾乎沒有損失地進(jìn)行高側(cè)到低側(cè)的轉(zhuǎn)換。實際上,首先關(guān)閉高側(cè)開關(guān),這允許外部儲能電感器將相電壓擺動到零。通過使用比較器來感測相電壓,然后在沒有電壓的情況下打開底部開關(guān),可以實現(xiàn)兩個器件的零電壓切換。相反,從低端到高端的轉(zhuǎn)換是“硬切換”,并且由于相電壓必須在正時切換,導(dǎo)致一些交叉?zhèn)鲗?dǎo)和電容損耗,因此會產(chǎn)生一些低效率。1

但是,在升壓模式下反之亦然:零電壓切換發(fā)生在低端到高端轉(zhuǎn)換期間,硬切換發(fā)生在電感拉低時。電源設(shè)計人員已經(jīng)提出了一些巧妙的技巧來克服在電源長時間以降壓或升壓配置工作時很難工作的硬切換低效率,并且很少(如果有的話)在兩種模式之間切換。

DDR存儲器電路中次級穩(wěn)壓器的降壓和升壓操作(源極和吸收電流)之間的持續(xù)快速翻轉(zhuǎn),同時器件保持恒定輸出電壓為主電源(VDD)的一半,與輸入電壓無關(guān),如果要保持高效率,則輸出電流需要與用于傳統(tǒng)電源的控制方案相比的不同類型的控制方案。

用于DDR電源的控制模塊

幸運(yùn)的是,DDR電源設(shè)計人員不必?fù)?dān)心提出控制機(jī)制,因為幾家主要半導(dǎo)體供應(yīng)商已將注意力轉(zhuǎn)移到任務(wù)上,并已實現(xiàn)商業(yè)化的控制器DDR內(nèi)存電源的獨特需求。

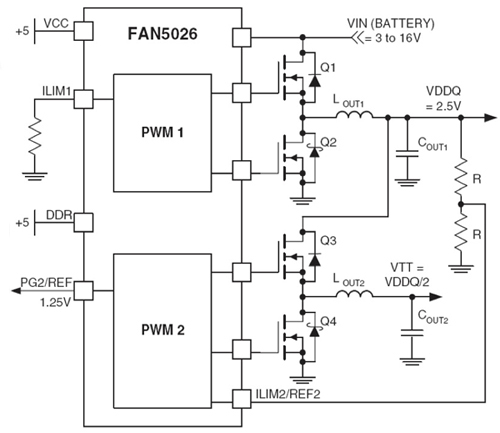

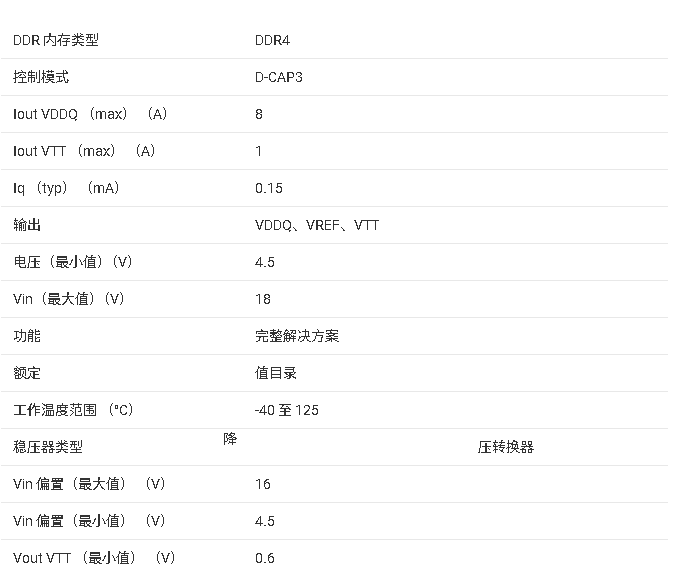

飛兆半導(dǎo)體提供用于存儲器應(yīng)用的FAN5026雙DDR/雙輸出開關(guān)控制器。該器件設(shè)計用作雙脈沖寬度調(diào)制(PWM)控制器,驅(qū)動兩個同步開關(guān)穩(wěn)壓器。

在DDR模式下,一個通道跟蹤另一個通道的輸出電壓,并提供必要的輸出電流吸收和源功能。該器件提供兩個主電源(VDD)輸出和一個跟蹤VDD/2的二次電源(VTT)。該芯片可在3至16 V的輸入范圍內(nèi)工作,該公司表示該器件可在0.9至5.5 V范圍內(nèi)調(diào)節(jié)兩個輸出電壓,提供高效率和穩(wěn)壓。同步整流和遲滯工作可在輕負(fù)載條件下保持效率。

該模塊面向服務(wù)器和臺式機(jī)DDR內(nèi)存電源或顯卡電源要求等應(yīng)用。圖3顯示了FAN5026的應(yīng)用電路。

圖3:Fairchild FAN5026 DDR電源控制器的應(yīng)用電路。

德州儀器還提供DDR和DDR2控制器模塊TPS51020。該芯片可在4.5至28 V輸入電壓下工作,專為高性能,高效率應(yīng)用而設(shè)計,其中與電流檢測電阻相關(guān)的損耗是不可接受的。例子包括鋰離子電池供電的便攜式計算機(jī)。通過在PWM串中啟用自動跳過操作,可以保持輕載條件下的高效率(圖4)。

圖4:TI的TPS51020專為便攜式計算機(jī)而設(shè)計。該公司稱該器件為雙開關(guān)穩(wěn)壓器DDR電源提供單芯片解決方案。在DDR模式下,TPS51020提供DDR應(yīng)用所需的所有功能,包括VTT的VDD/2跟蹤,電流源和吸收能力以及VTT參考輸出。

凌力爾特公司將LTC3876作為完整的DDR電源解決方案提供。該器件兼容DDR,DDR2,DDR3和未來DDRX低電壓標(biāo)準(zhǔn),集成了VDD和VTT控制器以及精密線性VTT參考。該公司表示,差分輸出檢測放大器和精密內(nèi)部基準(zhǔn)電壓相結(jié)合,可提供精確的VDD電源。

VTT控制器跟蹤精度VTT參考值,總直流誤差小于20 mV。在跟蹤VDD/2時,參考電壓保持1.2%的調(diào)節(jié)精度。 LTC3876的輸入范圍為4.5至38 V,VDD范圍為1.0至2.5 V,相應(yīng)的VTT輸出范圍為0.5至1.25 V.

DDR內(nèi)存及其后續(xù)版本使現(xiàn)代計算機(jī)能夠在高速而不會顯著增加功耗。但是,如果要在DDR運(yùn)行的高頻率下避免雜散信號,則需要仔細(xì)設(shè)計芯片組并終止公共總線。幸運(yùn)的是,通過選擇市場上的一種商用DDR電源模塊,工程師可以在電源設(shè)計方面取得重大進(jìn)展。這些器件集成了為存儲器芯片組供電所需的所有功能,并為精確跟蹤主電源的終端跟蹤提供恒定的減半電壓。

-

電源

+關(guān)注

關(guān)注

185文章

18923瀏覽量

264152 -

存儲器

+關(guān)注

關(guān)注

39文章

7747瀏覽量

172033 -

DDR

+關(guān)注

關(guān)注

11文章

760瀏覽量

69412

發(fā)布評論請先 登錄

MAX1917評估套件:DDR內(nèi)存電源管理解決方案

德明利推出CKD DDR5內(nèi)存條 為AI PC提供穩(wěn)定高頻內(nèi)存解決方案

MAX17000評估套件:DDR內(nèi)存電源解決方案的利器

探索LTM4632:DDR - QDR4內(nèi)存的完美電源解決方案

探索LTC3634:DDR電源的理想解決方案

LTC3634:DDR電源的高效解決方案

TPS54116-Q1:高性能DDR電源解決方案

立锜科技推出完整DDR5服務(wù)器內(nèi)存電源解決方案

MAX1917:DDR內(nèi)存電源管理的理想選擇

MAX17000:DDR2和DDR3內(nèi)存電源管理解決方案的卓越之選

MAX17000A:DDR2和DDR3內(nèi)存電源管理的理想之選

深入解析LTC3876:DDR電源的理想解決方案

DRAM動態(tài)隨機(jī)存取存儲器DDR2 SDRAM內(nèi)存解決方案

DDR SDRAM是什么存儲器(雙數(shù)據(jù)速率同步動態(tài)隨機(jī)存取存儲器介紹)

?TPS65295 DDR4內(nèi)存電源解決方案技術(shù)文檔總結(jié)

DDR存儲器電源的內(nèi)存解決方案

DDR存儲器電源的內(nèi)存解決方案

評論