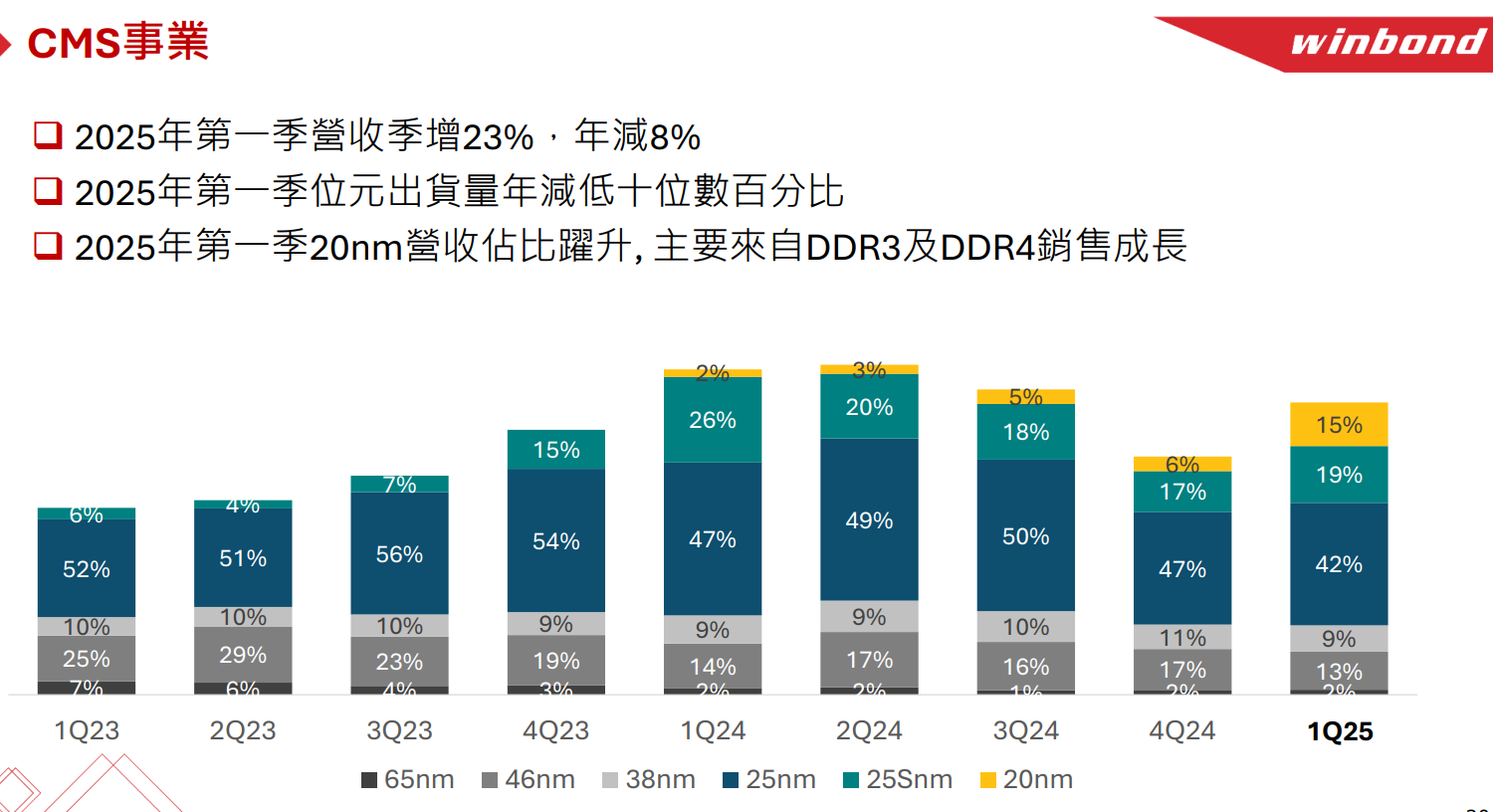

下,渠道搶貨助推價(jià)格上漲。未來(lái)隨著大廠的減產(chǎn),其他內(nèi)存廠商承接市場(chǎng)需求或?qū)⒊掷m(xù)影響DDR4的供需走勢(shì)。 ? 極速漲價(jià) ? CFM閃存市場(chǎng)數(shù)據(jù)顯示,近期渠道資源從高端到底部低端料號(hào)價(jià)格自上而下全線走高,渠道存儲(chǔ)廠商仍堅(jiān)定強(qiáng)勢(shì)拉漲DDR4 UDIMM報(bào)價(jià),部分DDR4顆粒現(xiàn)貨價(jià)格

2025-06-19 00:54:00 10155

10155

很多人可能覺(jué)得PCB信號(hào)速率越高,如25Gbps,56G/112G-PAM4信號(hào)等調(diào)試上發(fā)現(xiàn)的問(wèn)題會(huì)越多,其實(shí)不然。我們收到最多的調(diào)試問(wèn)題還是DDR3、DDR4等,不是跑不到額度速率,就是識(shí)別不到

2026-01-05 15:46:16

了三星自DDR2時(shí)代延續(xù)的命名傳統(tǒng),不再以“K4”為前綴。這一變化背后,折射出三星在DDR5技術(shù)競(jìng)爭(zhēng)中的新戰(zhàn)略布局

2026-01-02 05:53:00 4510

4510 探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器緩沖器 在DDR2內(nèi)存模塊的設(shè)計(jì)中,擁有高性能且穩(wěn)定的寄存器緩沖器至關(guān)重要。Renesas的IDT74SSTUBF32866B就是

2025-12-24 16:30:09 124

124 Renesas IDT74SSTUBF32866B:DDR2的25位可配置寄存器緩沖器詳解 在DDR2內(nèi)存模塊的設(shè)計(jì)中,一款合適的寄存器緩沖器至關(guān)重要。Renesas

2025-12-23 15:55:06 168

168 20000

H56G42AS2DX014NGDDR6 16Gb 227K

H56C8H24AIR-S2C GDDR6 8Gb 800K

A3T1GF40CBF-GM21+ DDR3 1Gb 1KK

2025-11-27 15:58:19

本章的實(shí)驗(yàn)任務(wù)是在 PL 端自定義一個(gè) AXI4 接口的 IP 核,通過(guò) AXI_HP 接口對(duì) PS 端 DDR3 進(jìn)行讀寫測(cè)試,讀寫的內(nèi)存大小是 4K 字節(jié)。

2025-11-24 09:19:42 3467

3467

信號(hào)完整性(Signal Integrity, SI)問(wèn)題:隨著DDR內(nèi)存頻率的提高,信號(hào)完整性問(wèn)題變得更加突出。高速信號(hào)在傳輸過(guò)程中會(huì)受到各種因素的影響,如反射、串?dāng)_、噪聲干擾等,這些問(wèn)題會(huì)導(dǎo)致

2025-11-17 10:25:33 3397

3397

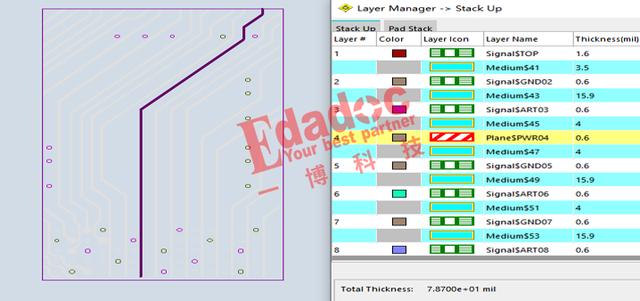

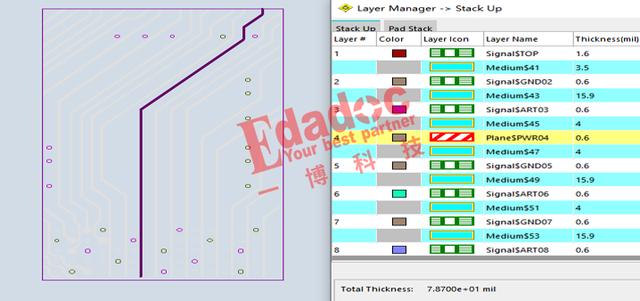

的設(shè)計(jì)也變化萬(wàn)千,有時(shí)候?yàn)榱顺杀緶p小層數(shù),這樣就可能會(huì)導(dǎo)致信號(hào)參考到電源平面的情況。當(dāng)然,作為一名有經(jīng)驗(yàn)的設(shè)計(jì)工程師,還是會(huì)優(yōu)先保證主要的高速串行信號(hào)上下層都有完整的地平面做參考。在保證重要的高速信號(hào)后

2025-11-11 17:46:12

雖然我看到過(guò)DDR的走線參考電源平面也能調(diào)試成功的案例,但是依然不妨礙我還想問(wèn):到底DDR走線能不能參考電源層啊?

2025-11-11 17:44:20 627

627

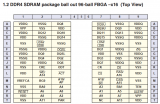

下面是HummingBird EV Kit給的版圖,其中DDR3_D0對(duì)應(yīng)的應(yīng)該是板子上的FPGA的C2引腳:?

不過(guò)我在配置MIG的時(shí)候,通過(guò)讀入ucf文件的方式配置DDR3 SDRAM的引腳

2025-11-06 07:57:09

電子發(fā)燒友網(wǎng)站提供《DDR3 SDRAM參考設(shè)計(jì)手冊(cè).pdf》資料免費(fèi)下載

2025-11-05 17:04:01 4

4 是簡(jiǎn)單方便的方法。

蜂鳥提供了icb2axi模塊,為了方便在block design中使用,將其封裝為IP,保留其可配置參數(shù),如下所示:

為了方便多個(gè)設(shè)備訪問(wèn)DDR,這里采用axi接口

2025-10-31 06:07:38

)

MM2S_LENGTH0x0028DMA寫數(shù)據(jù)長(zhǎng)度(字節(jié)為單位)

具體連接圖如下,由于本次使用的總線為50MHz,DMA時(shí)鐘為50M;DDR3 ui_clk為100MHz;e203這里使用了10MHz。時(shí)鐘的轉(zhuǎn)換完全

2025-10-29 08:21:10

由于FPGA內(nèi)部存儲(chǔ)資源有限,很多時(shí)候不能滿足需求,因此可以利用DDR對(duì)系統(tǒng)進(jìn)行存儲(chǔ)擴(kuò)展。由于DDR3內(nèi)部控制十分復(fù)雜,因此可以基于AXI總線,利用Vivado提供的MIG IP對(duì)DDR3進(jìn)行控制

2025-10-29 07:16:34

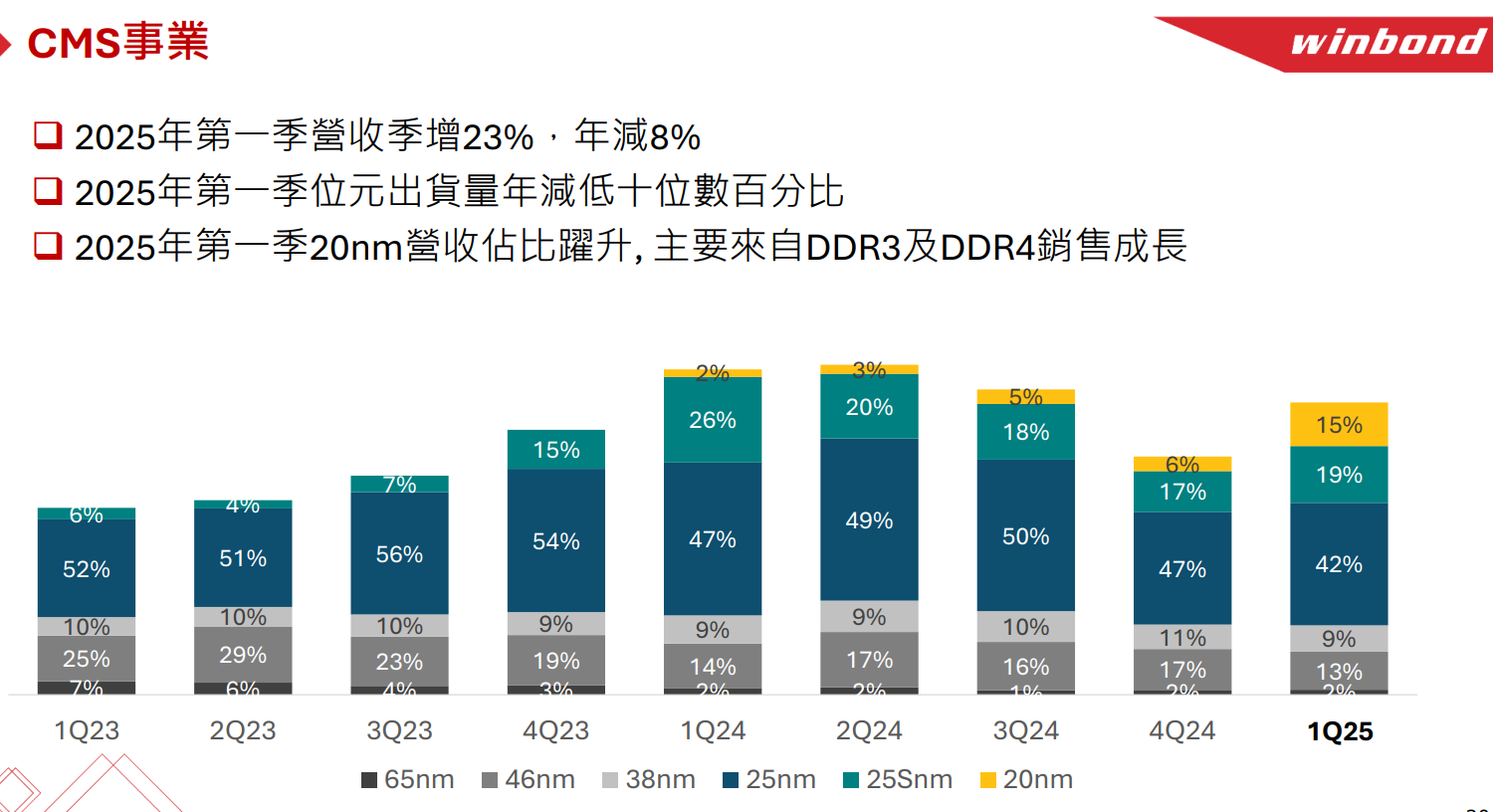

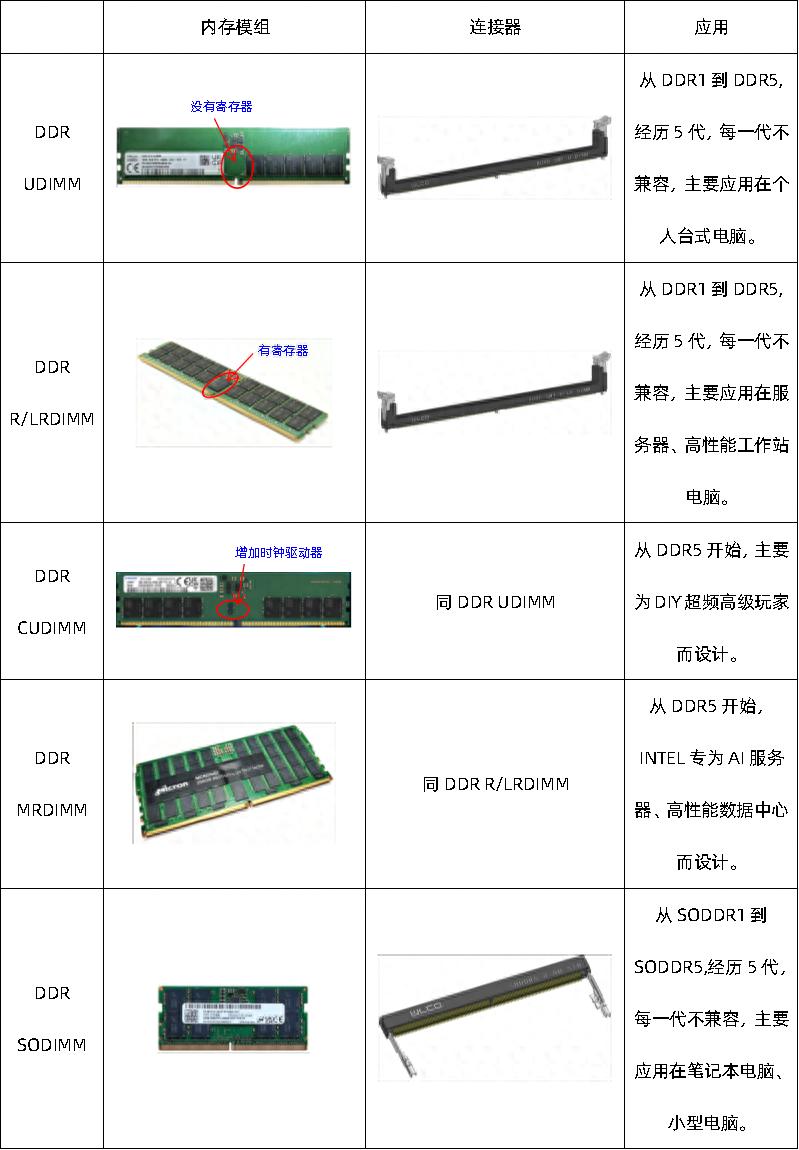

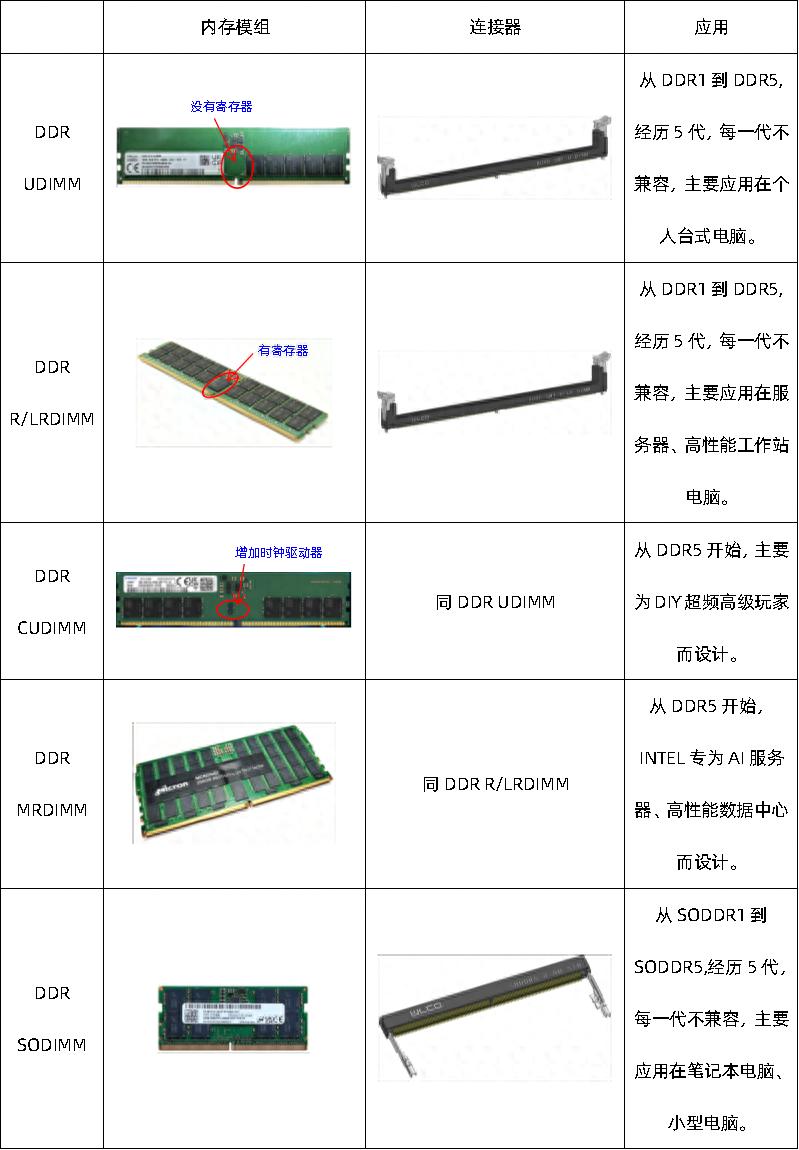

來(lái)源:深圳市興萬(wàn)聯(lián)電子有限公司投稿 作者:蔡友華 很多同事、同行、客戶都曾問(wèn)到:DDR與SODDR有什么區(qū)別?LPDDR SOCAMM2又是什么?今天,我來(lái)為大家整理一份簡(jiǎn)明的資料,進(jìn)行一次系統(tǒng)性

2025-10-28 11:06:23 1062

1062

文件夾內(nèi),打開文件夾。閱讀readme說(shuō)明文檔,我們能夠知道,原作者采用了vivado MIG IP來(lái)控制開發(fā)板上的DDR3,由于芯來(lái)科技的E203平臺(tái)系統(tǒng)片內(nèi)總線是icb總線,所以我們需要做跨時(shí)鐘域

2025-10-28 07:25:32

DDR使用

在我們的項(xiàng)目中,我們使用的是芯來(lái)科技的DDR200T開發(fā)板,我們通過(guò)調(diào)用板上的DDR3 IP核完成如下表的配置,配置完成后例化該DDR3,然后利用DMA和VDMA作為數(shù)據(jù)的緩沖模塊,將

2025-10-28 07:24:01

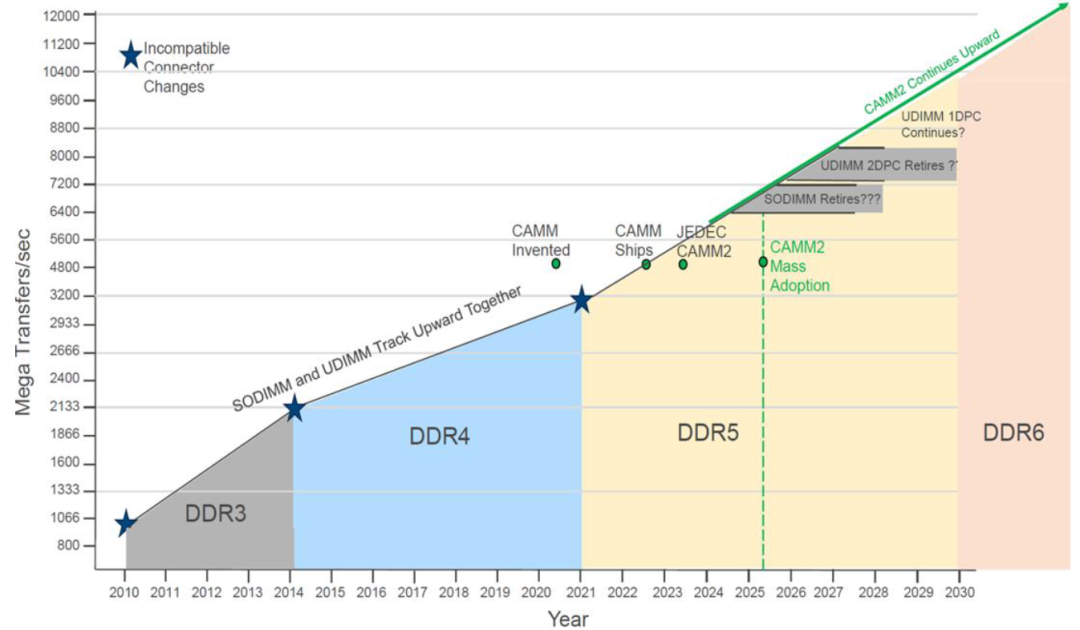

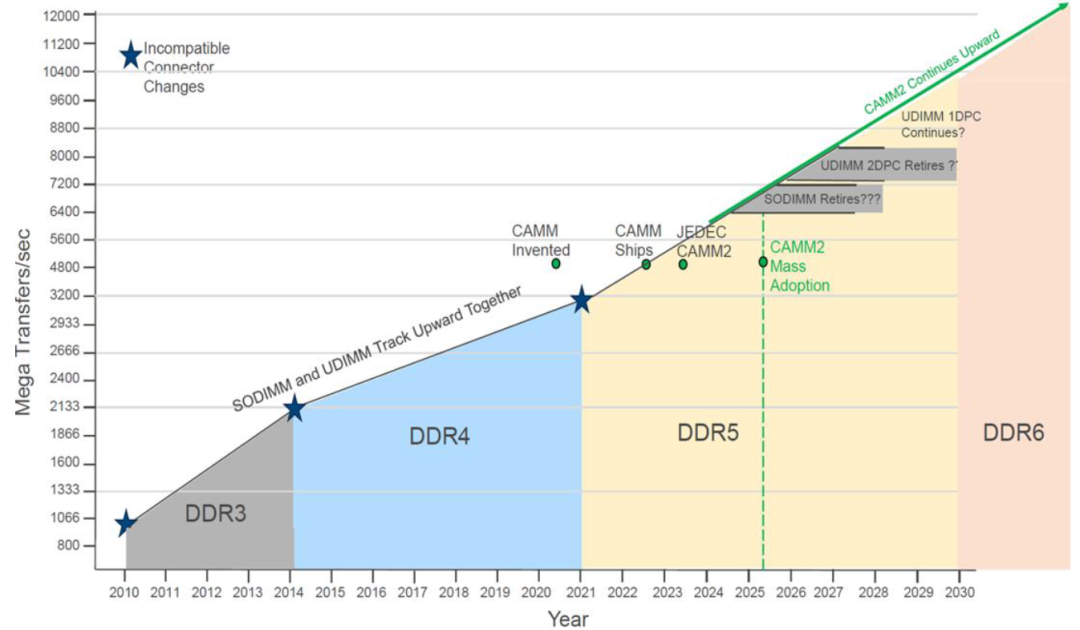

“ ?本文將詳細(xì)介紹 DDR5、LPDDR5 的技術(shù)細(xì)節(jié)以及 Layout 的規(guī)范要求。然后比較 CAMM2 模組與 SODIMM 的差別。? ” ?? 本文將介紹什么是 DDR5,DDR5 和之前

2025-10-27 19:28:16 7359

7359

前言:2025年,存儲(chǔ)市場(chǎng)持續(xù)“高燒”——-國(guó)際大廠停產(chǎn)DDR3/4,減產(chǎn)LPDDR4/4X,漲價(jià)50%只是起步-國(guó)產(chǎn)料號(hào)月更、周更,同一料號(hào)不同Die,顆粒參數(shù)“開盲盒”-更大的坑是:對(duì)于嵌入式

2025-10-24 11:59:51 918

918

的S00_AXI_ACLK、M00_AXI_ACLK,分別接系統(tǒng)頂層時(shí)鐘hfextclk、mig產(chǎn)生的用戶時(shí)鐘ui_clk,以此來(lái)實(shí)現(xiàn)跨時(shí)鐘域。

(2)例化DDR3模型(仿真的時(shí)候需要用,vivado

2025-10-24 07:25:00

] correct : %drn”,i,rd_data);

ddr_offset += 0x00000004;

}

(2)測(cè)試效果,讀數(shù)正確

vivado綜合:

注意:(1)綜合不需要例化ddr3模型,將

2025-10-23 06:16:44

Dynamic Random Access Memory)是DDR SDRAM的第三代產(chǎn)品,相較于DDR2,DDR3具有更高的運(yùn)行性能與更低的電壓。DDR SDRAM是在SDRAM技術(shù)的基礎(chǔ)上發(fā)展改進(jìn)而來(lái)的,同

2025-10-21 14:30:16

由于e203內(nèi)部DTCM空間較小,所以本隊(duì)針對(duì)DDR200T開發(fā)板進(jìn)行針對(duì)e203的DDR3存儲(chǔ)器擴(kuò)展。

論壇中所給出的e203擴(kuò)展DDR的方法大致分為兩種,一種是直接將DDR存儲(chǔ)器的接口使用ICB

2025-10-21 12:43:40

蜂鳥DDR200T中DDR3的ip配置案列,提供DDR3引腳配置。具體參數(shù)可更具項(xiàng)目實(shí)際更改。

這里選用的axi接口

在賽靈思的IP配置中沒(méi)有MT41K28M6JT-125K內(nèi)存的信息,因此選用

2025-10-21 11:19:08

Access Memory)是DDR SDRAM的第三代產(chǎn)品,相較于DDR2,DDR3具有更高的運(yùn)行性能與更低的電壓。DDR SDRAM是在SDRAM技術(shù)的基礎(chǔ)上發(fā)展改進(jìn)而來(lái)的,同SDRAM相比

2025-10-21 10:40:28

Random Access Memory)是DDR SDRAM的第三代產(chǎn)品,相較于DDR2,DDR3具有更高的運(yùn)行性能與更低的電壓。DDR SDRAM是在SDRAM技術(shù)的基礎(chǔ)上發(fā)展改進(jìn)而來(lái)的,同SDRAM相比

2025-10-21 08:43:39

在 FPGA 中測(cè)試 DDR 帶寬時(shí),帶寬無(wú)法跑滿是常見問(wèn)題。下面我將從架構(gòu)、時(shí)序、訪問(wèn)模式、工具限制等多個(gè)維度,系統(tǒng)梳理導(dǎo)致 DDR 帶寬跑不滿的常見原因及分析方法。

2025-10-15 10:17:41 735

735 三星近期已向全球 OEM 客戶發(fā)出正式函件,明確旗下 DDR4 模組將于 2025 年底進(jìn)入產(chǎn)品壽命結(jié)束(EOL)階段,最后訂購(gòu)日期定于 6 月上旬,最后出貨日期則為 12 月 10 日。此次停產(chǎn)

2025-10-14 17:11:37 1033

1033 DDR是硬件設(shè)計(jì)的重要一環(huán),作為一名硬件工程師除了對(duì)DDR基礎(chǔ)和原理要有了解外,最重要的也就是對(duì)DDR控制器的掌握。本文章從DDR外部管腳的角度進(jìn)行描述,學(xué)習(xí)DDR的關(guān)鍵設(shè)計(jì)要注意和了解的部分。

2025-10-10 09:15:24 2073

2073

回收DDR2,回收DDR3,收購(gòu)DDR2,收購(gòu)DDR3 DDR4 DDR5長(zhǎng)期現(xiàn)金高價(jià)回收DDR,回收三星DDR,回收海力士DDR,回收南亞DDR,回收爾必達(dá)DDR,回收美光DDR,回收DDR2

2025-10-09 14:15:34

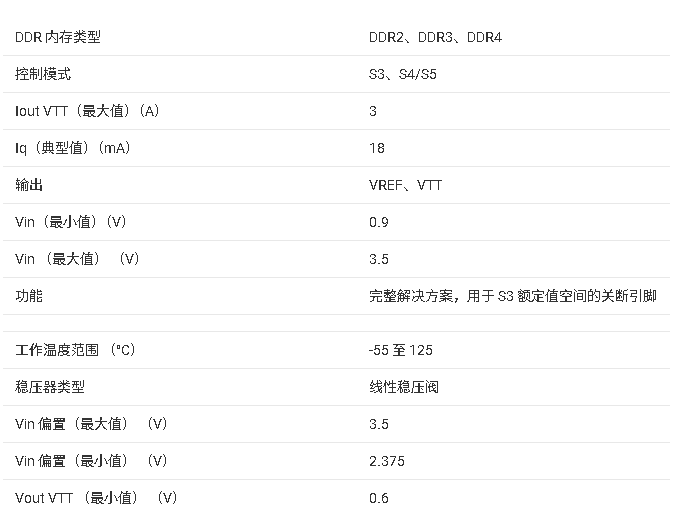

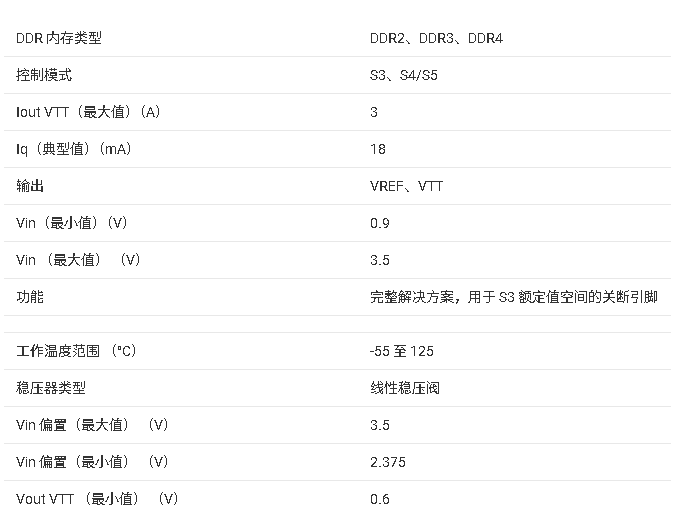

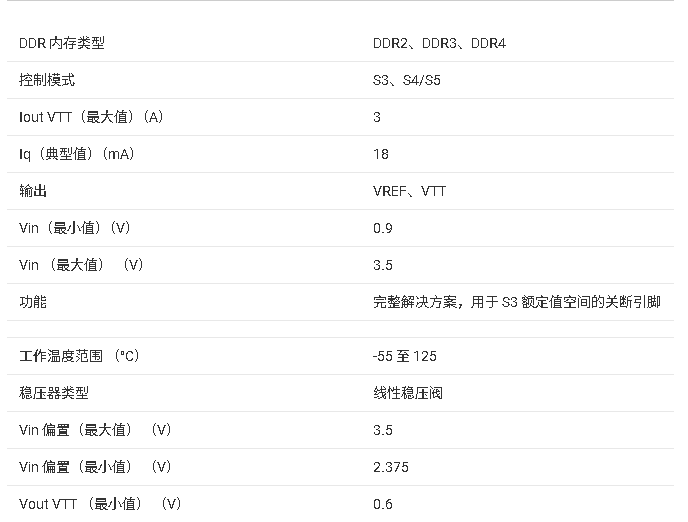

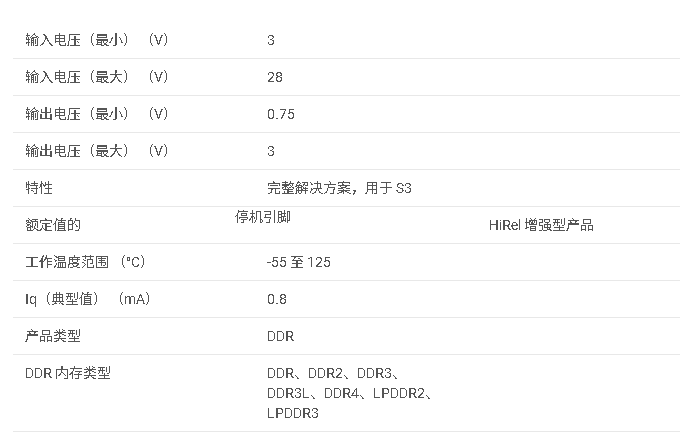

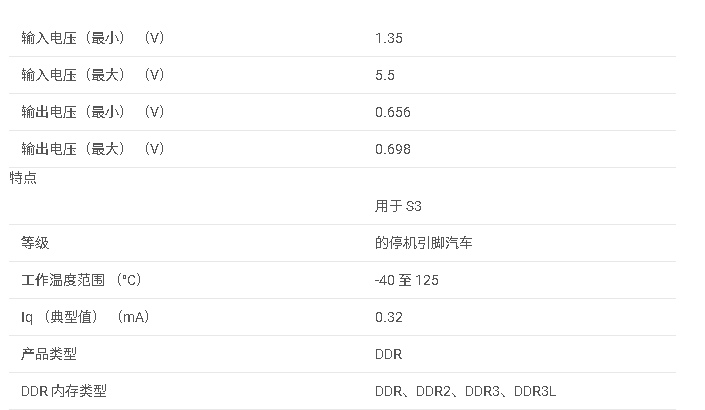

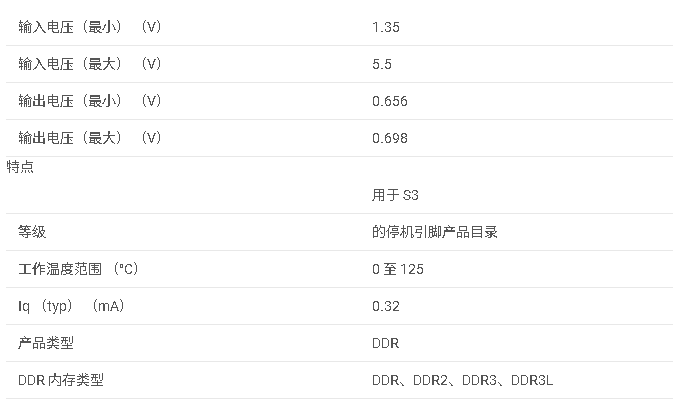

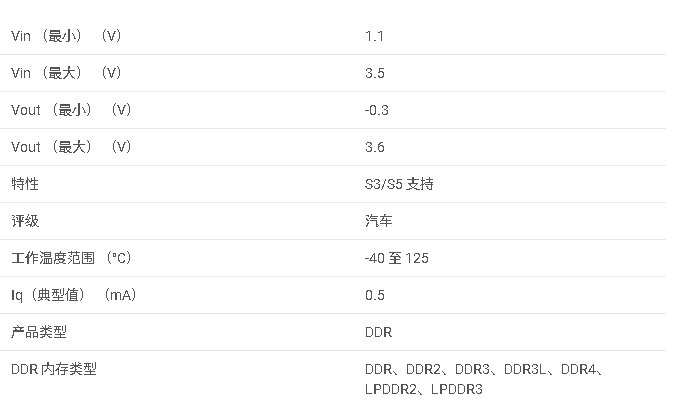

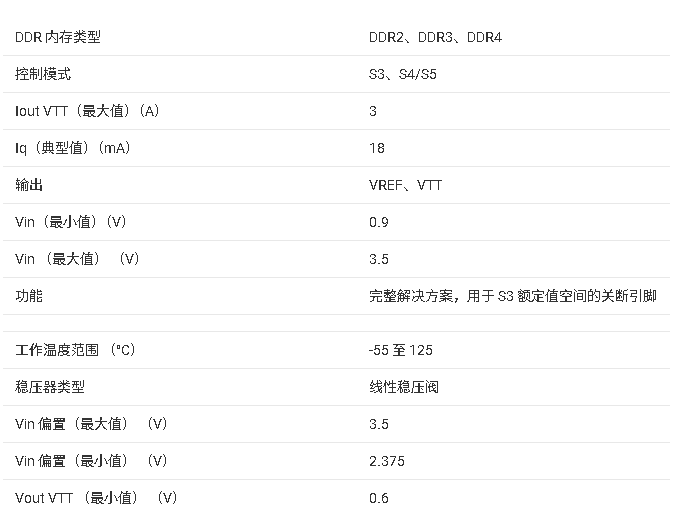

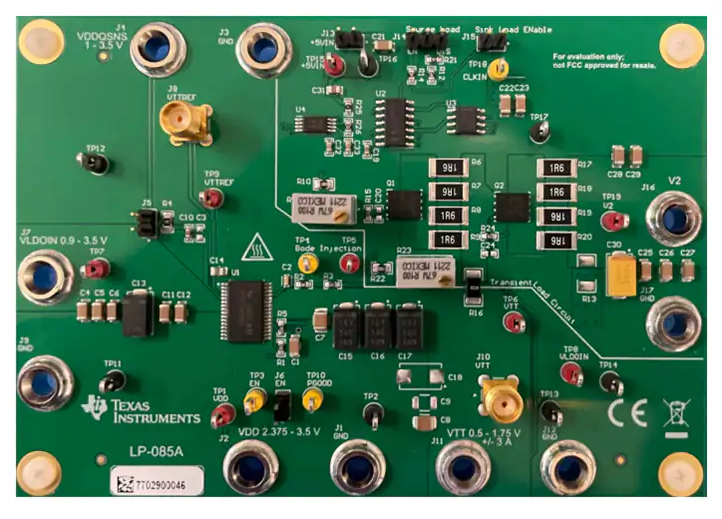

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接應(yīng)用。TPS7H3301-SP VTT 穩(wěn)壓器的快速瞬態(tài)響應(yīng)允許在讀/寫條件下提供非常穩(wěn)定的電源。在

2025-09-09 14:45:15 719

719

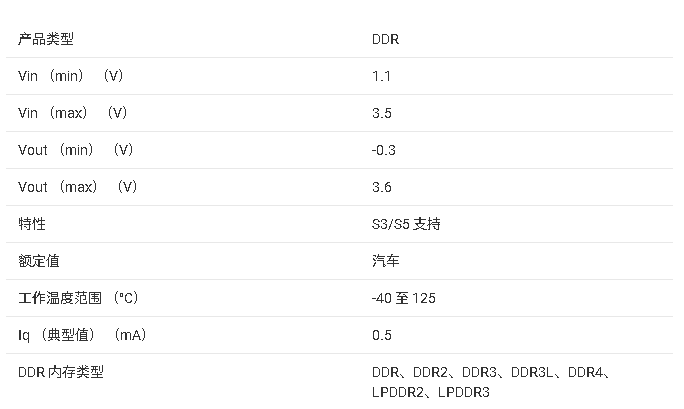

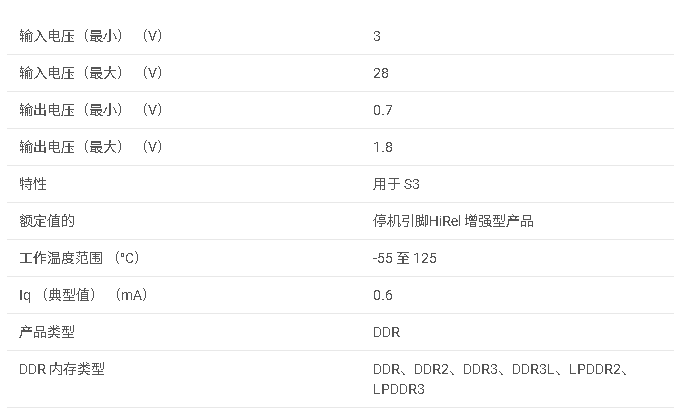

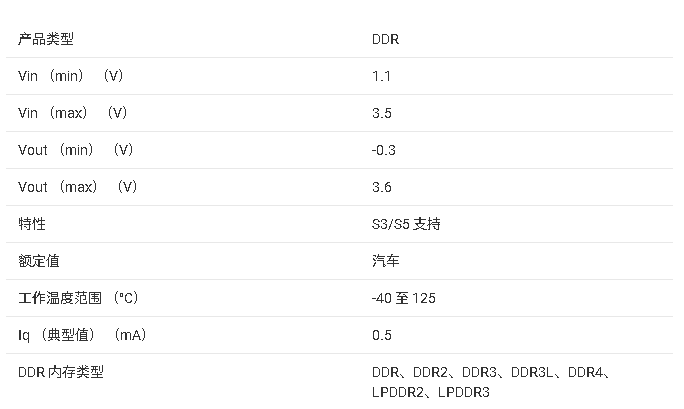

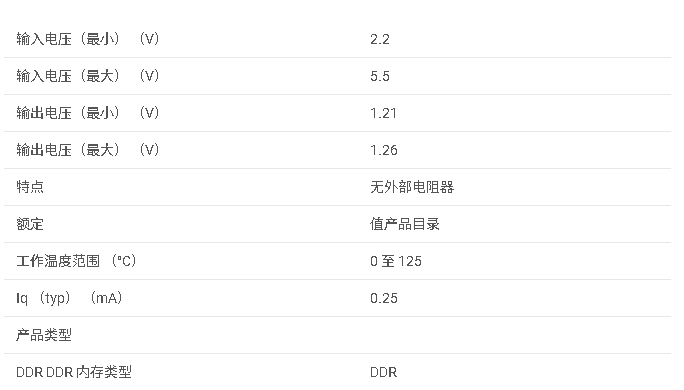

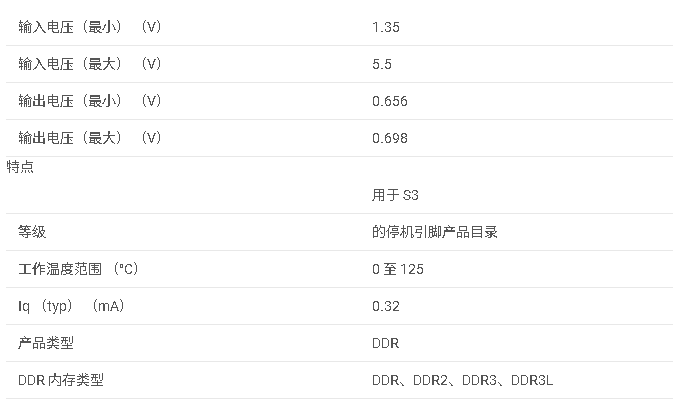

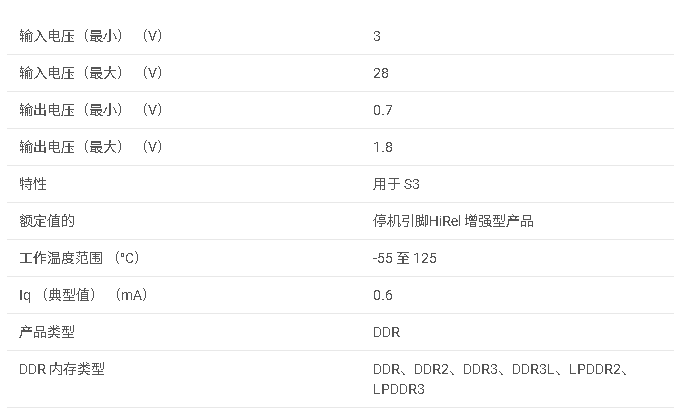

20 μF。該器件支持遙感功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 總線端接的所有電源要求。

2025-09-09 14:28:07 713

713

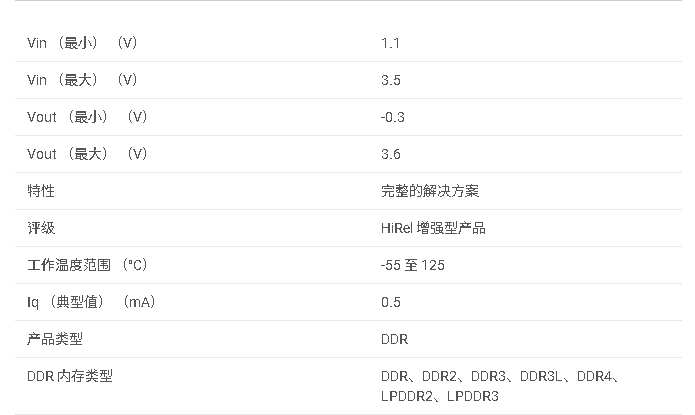

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應(yīng)用。TPS7H3302 VTT 穩(wěn)壓器的快速瞬態(tài)響應(yīng)允許在讀/寫條件下提供非常穩(wěn)定的電源

2025-09-09 13:53:22 687

687

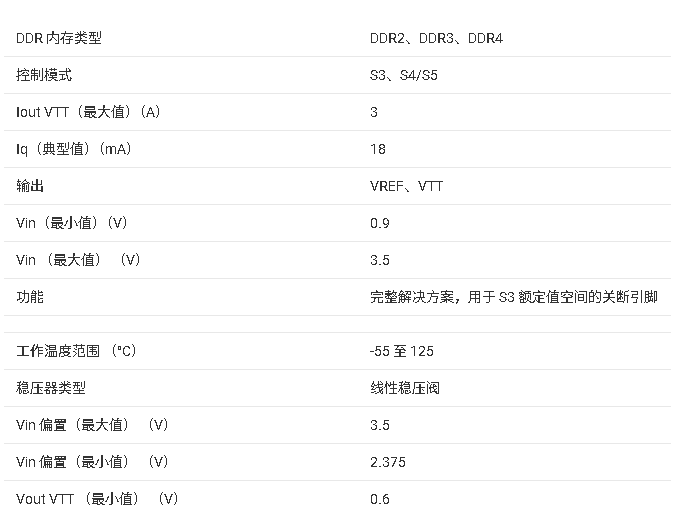

該TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接應(yīng)用。TPS7H3302 VTT 穩(wěn)壓器的快速瞬態(tài)響應(yīng)允許在讀/寫條件下提供非常穩(wěn)定的電源

2025-09-09 13:48:37 754

754

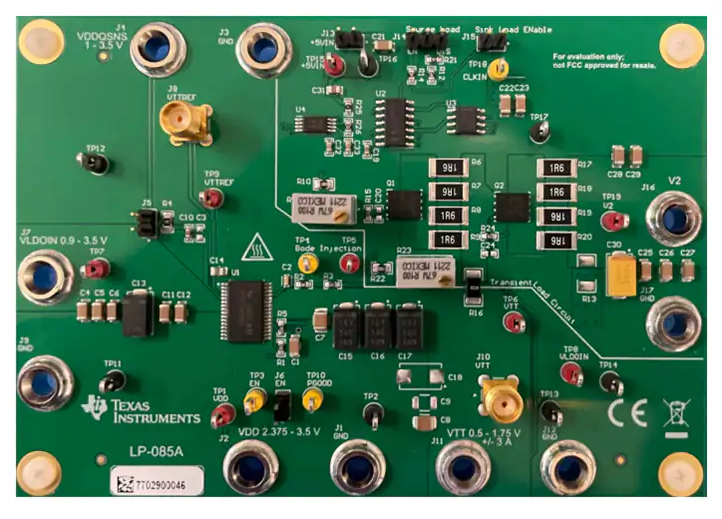

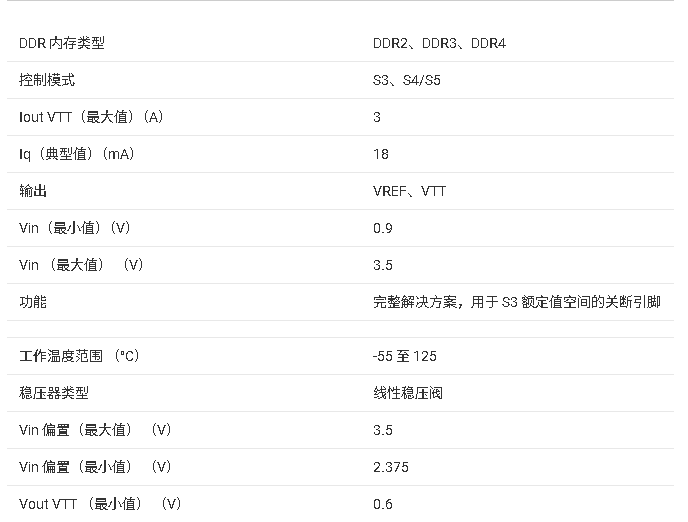

3A,支持測(cè)試DDR、DDR2、 DDR3、DDR3L和DDR4。該評(píng)估模塊配有方便的測(cè)試點(diǎn)和跳線,用于評(píng)估TPS7H3302-SEP DDR端子。TPS7H3302EVM評(píng)估模塊非常適合用于抗輻射DDR電源應(yīng)用以及用于DDR、DDR2、DDR3和DDR4的存儲(chǔ)器終端穩(wěn)壓器。

2025-08-27 16:14:21 831

831

憑借與紫光國(guó)芯的緊密合作,貞光科技能夠?yàn)榭蛻籼峁?b class="flag-6" style="color: red">DDR3、LPDDR4及LPDDR4X全系列車規(guī)級(jí)存儲(chǔ)產(chǎn)品。在產(chǎn)品覆蓋、技術(shù)支持和供應(yīng)保障等方面的綜合優(yōu)勢(shì),使貞光科技成為車載電子領(lǐng)域可靠且高效

2025-08-26 16:12:15 1423

1423

詳細(xì)了解硬件信息,包括#DDR 顆粒的型號(hào)、容量、速率、數(shù)據(jù)寬度等參數(shù),以及原理圖中DDR顆粒與處理器的連接方式、引腳定義等 。這些信息是進(jìn)行準(zhǔn)確配置的基礎(chǔ),直接影響到內(nèi)存的性能和穩(wěn)定性。

2025-08-13 09:25:05 3550

3550

DDR3 作為第三代雙倍數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,在內(nèi)存發(fā)展歷程中具有重要地位。它采用了8n預(yù)取架構(gòu),即每個(gè)時(shí)鐘周期能夠傳輸8倍于數(shù)據(jù)位寬的數(shù)據(jù)量,這使得數(shù)據(jù)傳輸效率大幅提升 。

2025-08-04 13:42:34 2910

2910

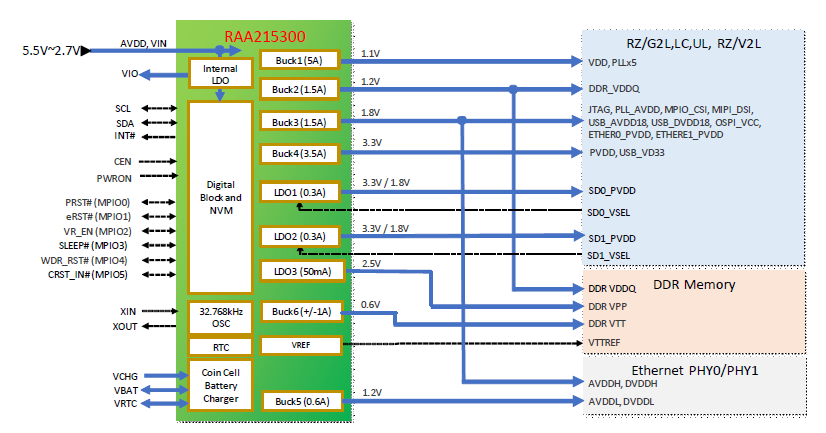

RZ/G2L微處理器配備Cortex-A55(1.2GHz)CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。此外,這款微處理器還

2025-08-04 13:40:03 3085

3085

電子發(fā)燒友網(wǎng)綜合報(bào)道,據(jù)業(yè)界消息,三星電子、SK海力士、美光均已完成DDR6規(guī)格的初期原型開發(fā),正與英特爾、AMD、英偉達(dá)等CPU/GPU廠商共同推進(jìn)平臺(tái)驗(yàn)證。當(dāng)前目標(biāo)性能為8800MT/s,后續(xù)

2025-07-31 08:32:00 3664

3664 本文緊接著前一個(gè)文檔《AD設(shè)計(jì)DDR3時(shí)等長(zhǎng)設(shè)計(jì)技巧-數(shù)據(jù)線等長(zhǎng) 》。本文著重講解DDR地址線、控制信號(hào)線等長(zhǎng)設(shè)計(jì),因?yàn)榈刂肪€、控制信號(hào)線有分支,SOC有可能帶有2片DDR或者更多,我們叫做T型分支

2025-07-29 16:14:51 2

2 的講解數(shù)據(jù)線等長(zhǎng)設(shè)計(jì)。? ? ? 在另一個(gè)文件《AD設(shè)計(jì)DDR3時(shí)等長(zhǎng)設(shè)計(jì)技巧-地址線T型等長(zhǎng)》中著重講解使用AD設(shè)計(jì)DDR地址線走線T型走線等長(zhǎng)處理的方法和技巧。

2025-07-28 16:33:12 4

4 ICF-PRX100-DDR硬件參考指南_V1.4_.pdf

2025-07-28 16:13:31 0

0 :

Window11 PDS2022.2-SP6.4

芯片型號(hào):

PG2L50H-484

2.實(shí)驗(yàn)原理

開發(fā)板集成 1 顆 4Gbit(512MB)DDR3 芯片,型號(hào)為 MT41K256M16。DDR3

2025-07-10 10:46:48

出整個(gè)數(shù)據(jù)流的路徑。這是一個(gè)典型的FPGA圖像處理系統(tǒng)架構(gòu):

輸入端 (Camera Input) -> ISP (圖像信號(hào)處理) -> DDR3 緩存 (Frame

2025-07-06 15:18:53

北京貞光科技有限公司作為紫光國(guó)芯的核心代理商,貞光科技在車規(guī)級(jí)存儲(chǔ)和工業(yè)控制領(lǐng)域深耕多年,憑借專業(yè)的技術(shù)服務(wù)能力為汽車電子、ADAS系統(tǒng)等高可靠性應(yīng)用提供穩(wěn)定供應(yīng)保障。近期DDR4內(nèi)存價(jià)格出現(xiàn)大幅

2025-06-27 09:45:11 4125

4125

(2GX8)內(nèi)存在6月2日的報(bào)價(jià)為5.171美元,當(dāng)時(shí)比DDR5低約8%。然而,最新報(bào)價(jià)顯示DDR4已上漲至8.633美元,不到一個(gè)月時(shí)間內(nèi)漲幅高達(dá)67%,且已經(jīng)超過(guò)DDR5的價(jià)格的44%。最新市場(chǎng)數(shù)據(jù)

2025-06-27 00:27:00 4538

4538 DDR內(nèi)存占據(jù)主導(dǎo)地位。全球DDR內(nèi)存市場(chǎng)正經(jīng)歷一場(chǎng)前所未有的價(jià)格風(fēng)暴。由于原廠加速退出DDR3/DDR4市場(chǎng),轉(zhuǎn)向DDR5和HBM(高帶寬內(nèi)存)生產(chǎn),DDR3和DDR4市場(chǎng)呈現(xiàn)供不應(yīng)求、供需失衡、漲勢(shì)延續(xù)的局面。未來(lái),DDR5滲透率將呈現(xiàn)快速提升,市場(chǎng)份額增長(zhǎng)的趨勢(shì)。

2025-06-25 11:21:15 2009

2009

隨著計(jì)算密集型任務(wù)的日益增長(zhǎng),DDR4內(nèi)存的性能瓶頸已逐步顯現(xiàn)。DDR5的出現(xiàn)雖解燃眉之急,但真正推動(dòng)內(nèi)存發(fā)揮極致性能的背后“功臣”——正是 DDR5 SPD(Serial Presence Detect)芯片。

2025-06-11 10:07:30 1913

1913

隨著汽車產(chǎn)業(yè)向智能化、網(wǎng)聯(lián)化加速轉(zhuǎn)型,高級(jí)駕駛輔助系統(tǒng)(ADAS)和智能駕駛技術(shù)已成為現(xiàn)代汽車不可或缺的核心組件。紫光國(guó)芯作為國(guó)內(nèi)領(lǐng)先的存儲(chǔ)器芯片制造商,其車規(guī)級(jí)DDR3存儲(chǔ)產(chǎn)品在智能駕駛和ADAS

2025-06-05 16:50:17 1220

1220

/VSYS/VDDD/V5V_P1的電都是正常的。

請(qǐng)教問(wèn)題:

1。CYPD5235的CC Pin功能異常,還可能會(huì)跟什么有關(guān)?

2。去掉的MP8859,會(huì)影響CYPD5235的軟件代碼執(zhí)行嗎?如果會(huì)

2025-05-30 07:04:55

CJTconnDDR系列產(chǎn)品介紹長(zhǎng)江連接器有限公司長(zhǎng)江連接器·DDR產(chǎn)品?DDR(DoubleDataRate)內(nèi)存的主要特性包括?:雙倍數(shù)據(jù)率?:DDR內(nèi)存的核心特性是其雙倍數(shù)據(jù)率,每個(gè)時(shí)鐘周期

2025-05-17 23:35:17 929

929

初三星公司已經(jīng)與主要客戶協(xié)商新定價(jià),DDR4的價(jià)格提高約20%,DDR5的價(jià)格上漲5%。 此外,SK海力士、美光此前也傳出漲價(jià)的消息。據(jù)供應(yīng)鏈人士透露,海力士DRAM(消費(fèi)級(jí))顆粒(Memory Chip/Die)價(jià)格已上漲約12%。 長(zhǎng)江存儲(chǔ)旗下零售品牌致態(tài)此前也透露,或從2025年4月起上調(diào)渠道提貨價(jià)

2025-05-13 15:20:11 1204

1204 最新消息,三星電子本月初與主要客戶就提高DRAM芯片售價(jià)達(dá)成一致。DDR4 DRAM價(jià)格平均上漲兩位數(shù)百分比;DDR5價(jià)格上漲個(gè)位數(shù)百分比。據(jù)稱 DDR4 上調(diào) 20%,DDR5 上調(diào)約 5

2025-05-13 01:09:00 6843

6843 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)近日宣布率先推出基于臺(tái)積公司 N3 工藝的 DDR5 12.8Gbps MRDIMM Gen2 內(nèi)存 IP 解決方案。該新解決方案可滿足

2025-05-09 16:37:44 905

905 LP2995 線性穩(wěn)壓器旨在滿足 JEDEC SSTL-2 和 SSTL-3 標(biāo)準(zhǔn) DDR-SDRAM 終止規(guī)范。該器件包含一個(gè)高速運(yùn)算放大器 對(duì)負(fù)載瞬變提供出色的響應(yīng)。輸出級(jí)可防止擊穿,同時(shí)

2025-05-06 09:33:38 715

715

下面是調(diào)用的DDR3模塊的,模塊的倒數(shù)第二行是,模塊的時(shí)鐘輸入,時(shí)鐘源來(lái)自PLL產(chǎn)生的系統(tǒng)時(shí)鐘的倍頻。

2025-05-03 10:21:00 1339

1339

LP2996-N 和 LP2996A 線性穩(wěn)壓器旨在滿足 JEDEC SSTL-2 標(biāo)準(zhǔn) DDR-SDRAM 終止規(guī)范。該器件還支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3

2025-04-29 18:11:05 834

834

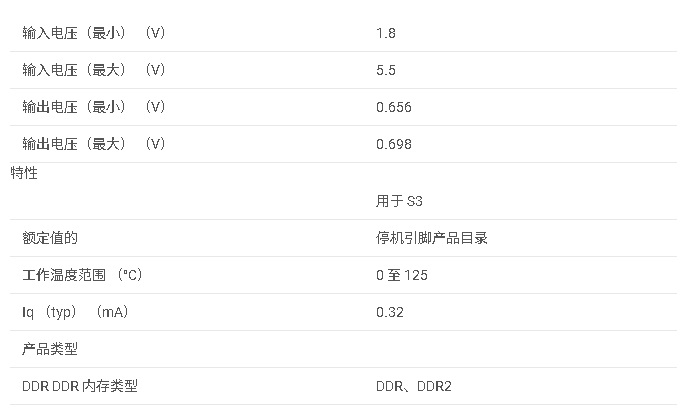

該TPS51100保持快速瞬態(tài)響應(yīng),僅需 20 μF(2 × 10 μF)的 陶瓷輸出電容。TPS51100 支持遙感功能和所有功能 需要根據(jù) JEDEC 規(guī)范為 DDR 和 DDR2 VTT 總線

2025-04-29 17:15:20 774

774

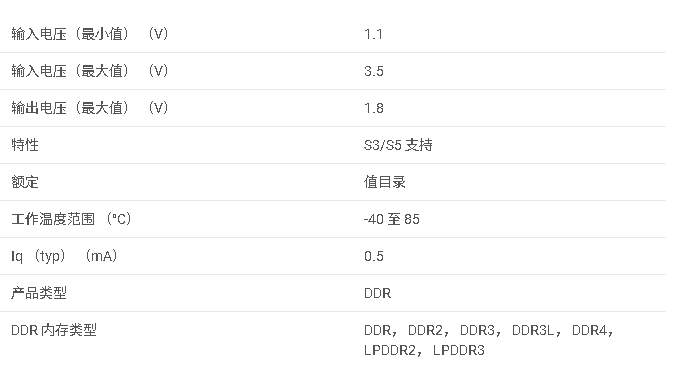

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內(nèi)存系統(tǒng)提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1031

1031

在高速PCB設(shè)計(jì)中,DDR模塊是絕對(duì)繞不過(guò)去的一關(guān)。無(wú)論你用的是DDR、DDR2還是DDR3,只要設(shè)計(jì)不規(guī)范,后果就是——信號(hào)反射、時(shí)序混亂、系統(tǒng)頻繁死機(jī)。

2025-04-29 13:51:03 2491

2491

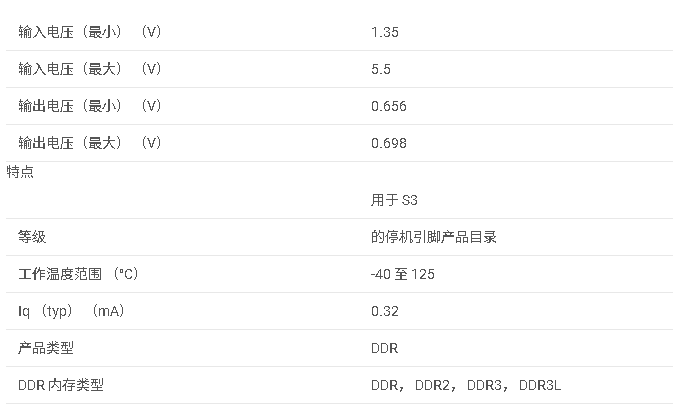

LP2998 線性穩(wěn)壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標(biāo)準(zhǔn) DDR-SDRAM 和 DDR2 內(nèi)存終止的規(guī)范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

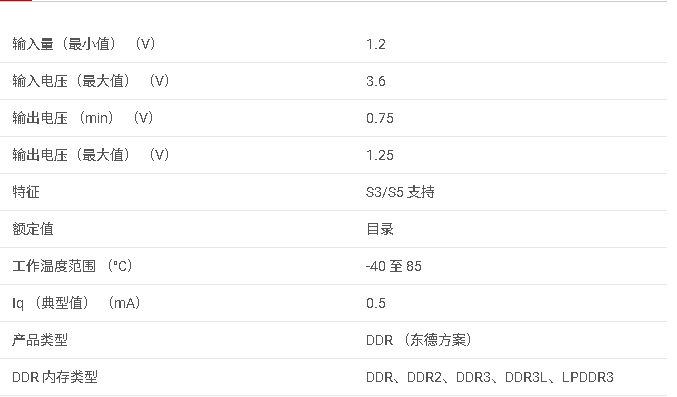

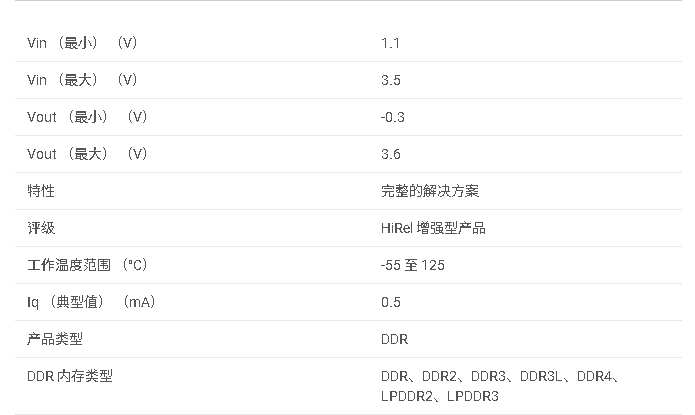

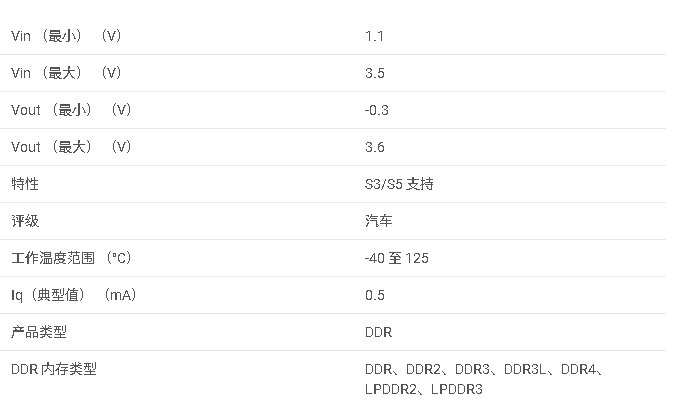

僅為 20 μF。該TPS51200支持遠(yuǎn)程感應(yīng)功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-29 09:59:25 1345

1345

只需要 20 μF 的最小輸出電容。TPS51200-Q1 器件支持遠(yuǎn)程感應(yīng)功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-28 16:21:07 852

852

TPS59116 為 DDR/SSTL-2、DDR2/SSTL-18 和 DDR3 內(nèi)存提供完整的電源 系統(tǒng)。它將同步降壓控制器與 3A 灌電流/拉電流跟蹤線性穩(wěn)壓器和緩沖低噪聲基準(zhǔn)集成在一起

2025-04-28 13:54:45 814

814

TPS51216 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內(nèi)存系統(tǒng)提供完整的電源。它將同步降壓穩(wěn)壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-28 11:09:05 663

663

TPS51916 器件以最低的總成本和最小的空間為 DDR2、DDR3、DDR3L 和 DDR4 內(nèi)存系統(tǒng)提供完整的電源。它集成了同步降壓穩(wěn)壓控制器 (VDDQ),具有 2A 灌電流和 2A 源跟蹤 LDO (VTT) 和緩沖低噪聲基準(zhǔn) (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬態(tài)響應(yīng),并且只需要 1 × 10μF 的陶瓷輸出電容。該器件支持遠(yuǎn)程感應(yīng)功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 總線的所有電源要求。VTT 電流

2025-04-28 10:04:48 685

685

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、 和 LPDDR3 內(nèi)存系統(tǒng)。它將同步降壓控制器與 1A 灌電流/拉電流集成在一起 跟蹤線性穩(wěn)壓器和緩

2025-04-27 13:35:32 741

741

TPS51716為 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的電源 以最低的總成本和最小空間實(shí)現(xiàn)內(nèi)存系統(tǒng)。它集成了一個(gè)同步降壓 具有 2A 灌電流/拉電流跟蹤 LDO

2025-04-27 11:36:05 763

763

LP2998 線性穩(wěn)壓器旨在滿足 JEDEC SSTL-2 和 JEDEC SSTL-18 標(biāo)準(zhǔn) DDR-SDRAM 和 DDR2 內(nèi)存終止的規(guī)范。該器件還支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

LP2996A 線性穩(wěn)壓器旨在滿足 JEDEC SSTL-2 規(guī)范 DDR-SDRAM 終止。該器件還支持 DDR2、DDR3 和 DDR3L VTT 總線端接,帶 V~DDQ~最小為 1.35V

2025-04-26 15:02:50 746

746

TPS51216-EP 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內(nèi)存系統(tǒng)提供完整的電源。它將同步降壓穩(wěn)壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-26 11:12:30 681

681

只需要最小輸出 電容為 20 μF。TPS51200-EP 支持遙感功能和所有功率要求 用于 DDR、DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 總線終端。

2025-04-26 10:26:35 1335

1335

的最小輸出電容。該器件支持遠(yuǎn)程感應(yīng)功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 總線終端的所有電源要求。

2025-04-25 10:07:15 1053

1053

如果把CPU比作廚師,內(nèi)存就是廚房的操作臺(tái),DDR5內(nèi)存相當(dāng)于給廚師換了一個(gè)更大、更快、更整潔的操作臺(tái),做起菜來(lái)自然效率提升。隨著DDR5內(nèi)存價(jià)格逐步下降,這項(xiàng)具備更高帶寬和超大容量的新技術(shù),正在

2025-04-18 10:34:13 71

71

在全球科技競(jìng)爭(zhēng)加劇、國(guó)產(chǎn)替代加速推進(jìn)的背景下,紫光國(guó)芯憑借其在DDR3與RDIMM等高端內(nèi)存芯片領(lǐng)域的技術(shù)積累,不斷實(shí)現(xiàn)突破,推動(dòng)國(guó)產(chǎn)存儲(chǔ)芯片向高端市場(chǎng)邁進(jìn)。作為其核心代理商,貞光科技在市場(chǎng)推廣

2025-04-16 16:39:30 1342

1342

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產(chǎn)品,相較于DDR2,DDR3有更高的運(yùn)行性能與更低的電壓。

2025-04-10 09:42:53 3930

3930

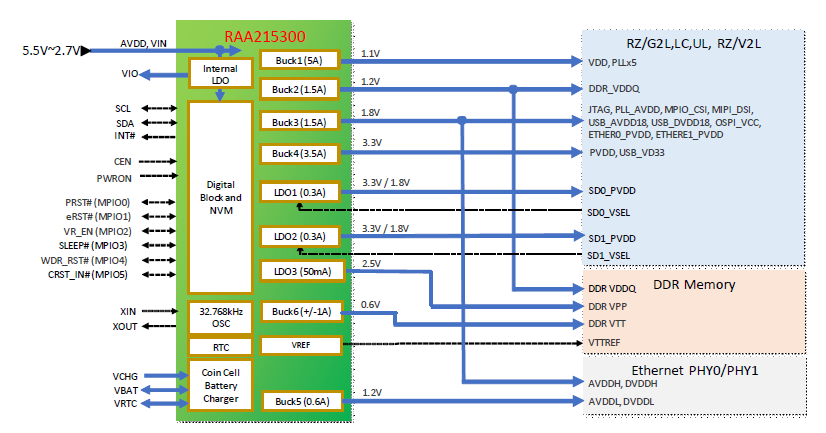

RAA215300 是一款高性能、低成本的 9 通道 PMIC,專為 32 位和 64 位 MCU 和 MPU 應(yīng)用而設(shè)計(jì)。 該 PMIC 支持DDR3、DDR3L、DDR4 和 LPDDR4 內(nèi)存

2025-04-09 15:31:25 657

657

我想知道 iMX8MPlus 部分的 DDR、eMMC、SD 卡和閃存的最大可能大小MIMX8ML8DVNLZAB。

2025-03-28 06:20:39

我們目前正在使用 iMX6UL DDR 寄存器編程輔助工具為 U-Boot 生成 DCD 表。我們的設(shè)備使用的是 MT41K128M16JT-107,即 DDR3-1866,這意味著它的時(shí)鐘周期頻率

2025-03-27 07:16:35

燦芯半導(dǎo)體(上海)股份有限公司(燦芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平臺(tái)的DDR3/4, LPDDR3/4 Combo IP。該IP具備廣泛的協(xié)議兼容性,支持DDR3

2025-03-21 16:20:03 984

984 初次使用XC7A35T-FGG484做設(shè)計(jì),用的是25MHZ有源晶振,有源晶振3.3V供電,DDR3的供電1.35V,現(xiàn)在接上晶振后,DDR3的供電變成1.8V

求助怎么解決。

2025-03-21 14:25:05

、準(zhǔn)備工作 1.選擇合適的探頭:選擇具有高帶寬和低電容的探頭,以減少信號(hào)失真。對(duì)于DDR信號(hào)測(cè)試,通常推薦使用差分探頭,以便準(zhǔn)確測(cè)量差分信號(hào)。 2.設(shè)置示波器參數(shù):確保示波器的帶寬至少是待測(cè)信號(hào)頻率的兩倍以上。同時(shí),設(shè)置合適的采樣率和存儲(chǔ)深度,以捕捉足

2025-03-14 12:06:00 942

942

:NT5CC256M16EP-EKI DDR3(L) 4Gb SDRAM CL-TRCD-TRP{13-13-13}

手冊(cè)要求 933MHz Clock但是STM32MP13x 最高給 DDRC 頻率

2025-03-11 07:11:03

DDR內(nèi)存控制器是一個(gè)高度集成的組件,支持多種DDR內(nèi)存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過(guò)精心設(shè)計(jì)的架構(gòu)來(lái)優(yōu)化內(nèi)存訪問(wèn)效率。

2025-03-05 13:47:40 3573

3573

我看了一下所購(gòu)買的評(píng)估開發(fā)板,上面帶有DDR2的接口,我想使用DDR2來(lái)進(jìn)行存儲(chǔ),但是沒(méi)有找到接口相關(guān)的引腳文件,ucf文件中也沒(méi)有DDR2相關(guān)的引腳

2025-02-28 08:42:16

1. DLPC410的datasheet寫明1bit的刷新率可以達(dá)到32KHz,在目前的EVM上可以實(shí)現(xiàn)嗎?

2. 如果第1個(gè)問(wèn)題回答是否定的,那么如何設(shè)計(jì)才能達(dá)到高刷新率?

3.EVM上的內(nèi)存是DDR2,如果提升為DDR3或者DDR4是否可以提高刷新率?

2025-02-21 10:23:16

據(jù)報(bào)道,業(yè)內(nèi)人士透露,全球三大DRAM內(nèi)存制造商——三星電子、SK海力士和美光,有望在2025年內(nèi)正式停產(chǎn)已有多年歷史的DDR3和DDR4兩代內(nèi)存。 隨著技術(shù)的不斷進(jìn)步和消費(fèi)級(jí)平臺(tái)的更新?lián)Q代

2025-02-19 11:11:51 3460

3460 “春節(jié)期間,國(guó)內(nèi)補(bǔ)貼政策持續(xù)釋放效能,市場(chǎng)需求在短期內(nèi)維持旺盛,推動(dòng)大尺寸面板價(jià)格在今年1月持續(xù)上漲,進(jìn)入2月,美對(duì)華上調(diào)10%關(guān)稅政策落地,對(duì)墨西哥等地增加關(guān)稅的不確定性風(fēng)險(xiǎn)增加,品牌方或加大采購(gòu)需求,面板廠僅小幅上調(diào)稼動(dòng)率以應(yīng)對(duì),預(yù)計(jì)今年2月面板價(jià)格全線上漲。”

2025-02-18 10:30:42 1923

1923 ;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM內(nèi)存模塊,專為滿足現(xiàn)代計(jì)算需求而設(shè)計(jì)。該產(chǎn)品以其高帶寬和低功耗的特性,廣泛應(yīng)用于個(gè)人電腦、服務(wù)器和嵌入式系統(tǒng)中,成為市場(chǎng)上備

2025-02-10 20:10:39

如需了解價(jià)格貨期等具體信息,歡迎在首頁(yè)找到聯(lián)系方式鏈接我。不要留言,留言會(huì)被吞,收不到留言。 8GB DDR4 ECC UDIMM 產(chǎn)品概述 8GB DDR4 ECC UDIMM

2025-02-10 20:07:47

如需了解價(jià)格貨期等具體信息,歡迎在首頁(yè)找到聯(lián)系方式鏈接我。不要留言,留言會(huì)被吞,收不到留言。 16GB DDR4 ECC UDIMM 產(chǎn)品概述 16GB DDR4 ECC

2025-02-10 20:05:15

M425R2GA3PB0-CWM 是一款高性能的 DDR5 SO-DIMM 內(nèi)存模塊,具有 16GB 的容量,專為滿足現(xiàn)代移動(dòng)計(jì)算需求而設(shè)計(jì)。這款內(nèi)存條采用了 Samsung 的先進(jìn)技術(shù),適用于各種

2025-02-10 07:49:16

最后一期我們主要介紹智多晶DDR Controller使用時(shí)的注意事項(xiàng)。

2025-01-24 11:14:14 1479

1479

本期主要介紹智多晶DDR Controller的常見應(yīng)用領(lǐng)域、內(nèi)部結(jié)構(gòu)、各模塊功能、配置界面、配置參數(shù)等內(nèi)容。

2025-01-23 10:29:54 1268

1268

一個(gè)10Nf~100nF的電容,整個(gè)VTT電路上需要有uF級(jí)大電容進(jìn)行儲(chǔ)能。

一般情況下,DDR的數(shù)據(jù)線都是一驅(qū)一的拓?fù)浣Y(jié)構(gòu),且DDR2和DDR3內(nèi)部都有ODT做匹配,所以不需要拉到VTT做匹配即可

2025-01-21 06:02:11

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論