完善資料讓更多小伙伴認識你,還能領(lǐng)取20積分哦,立即完善>

標簽 > pll

文章:581個 瀏覽:138167次 帖子:522個

鎖相環(huán)(PLL,Phase Lock Loop)的主要作用是實現(xiàn)輸出時鐘對輸入?yún)⒖紩r鐘的相位與頻率的精確跟蹤和同步。鎖相環(huán)(PLL)的主要模塊包括相位頻...

Texas Instruments CDC536:高性能時鐘驅(qū)動器的深度剖析

Texas Instruments CDC536:高性能時鐘驅(qū)動器的深度剖析 在電子設(shè)計領(lǐng)域,時鐘驅(qū)動器的性能對于整個系統(tǒng)的穩(wěn)定性和可靠性起著至關(guān)重要的...

Texas Instruments CDCU877/CDCU877A:高性能時鐘驅(qū)動器的卓越之選

Texas Instruments CDCU877/CDCU877A:高性能時鐘驅(qū)動器的卓越之選 在電子設(shè)備的設(shè)計中,時鐘信號的精確分配和管理至關(guān)重要。...

2026-02-10 標簽:pll時鐘驅(qū)動器CDCU877/CDCU877A 138 0

CDCE906:高性能可編程時鐘合成器的深度解析 在電子工程師的工作中,一款性能卓越的時鐘合成器對于系統(tǒng)的穩(wěn)定運行至關(guān)重要。今天,我們就來深入了解一下德...

CDCE706:高性能3 - PLL時鐘合成器的深度解析 在電子設(shè)計領(lǐng)域,時鐘合成器對于確保系統(tǒng)的穩(wěn)定運行和精確計時起著至關(guān)重要的作用。今天,我們就來深...

SyncE/IEEE1588/DPLL時鐘凈化器為什么更依賴VCXO?

VCXO是通信同步與PLL/DPLL時鐘凈化器的核心可調(diào)振蕩源,決定鎖相穩(wěn)定性與抖動指標。本文從工程視角梳理:頻點與輸出規(guī)劃、APR拉偏范圍預(yù)算、VCT...

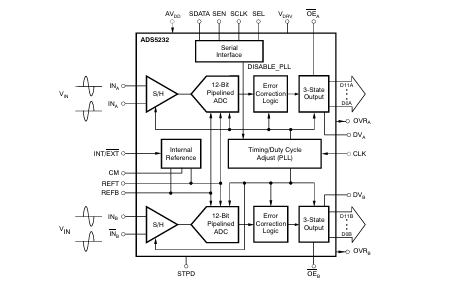

? 在當今的電子設(shè)計領(lǐng)域,模擬到數(shù)字的轉(zhuǎn)換是許多系統(tǒng)中的關(guān)鍵環(huán)節(jié)。德州儀器(TI)的ADS5232作為一款雙路、高速、高動態(tài)范圍的12位流水線式模數(shù)轉(zhuǎn)換...

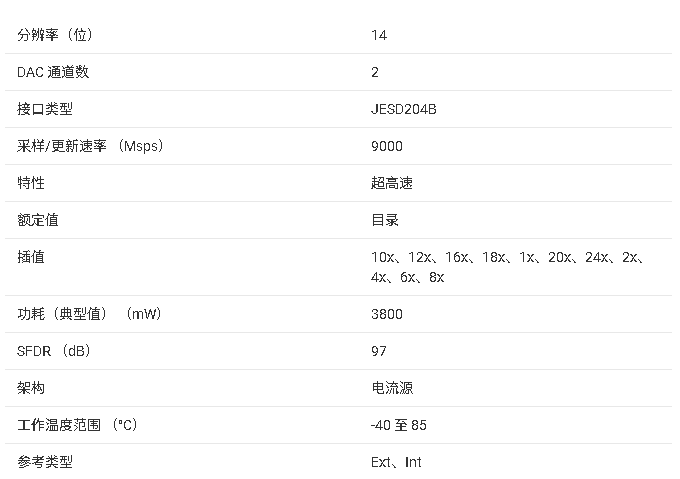

DAC38RF82 雙通道、14位、9GSPS、1x-24x插值、6 和 9 GHz PLL 數(shù)模轉(zhuǎn)換器技術(shù)手冊

DAC38RF82和DAC38RF89是高性能、寬帶寬的射頻采樣數(shù)模(DAC),能夠?qū)崿F(xiàn)高達3.33 GSPS的雙通道輸入數(shù)據(jù)速率或8位至9GSPS的單...

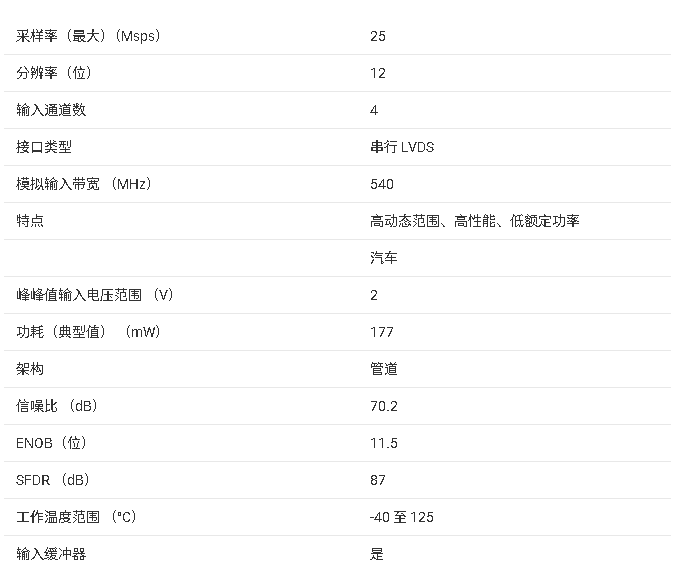

ADC3421-Q1 汽車四通道 12 位 25MSPS 模數(shù)轉(zhuǎn)換器

ADC3421-Q1 是一款汽車級、高線性度、超低功耗、四通道、12 位、25 MSPS 模數(shù)轉(zhuǎn)換器 (ADC)。該器件專為支持具有大動態(tài)范圍要求的高輸...

?AFE159x系列低功耗生物電位測量模擬前端技術(shù)文檔總結(jié)

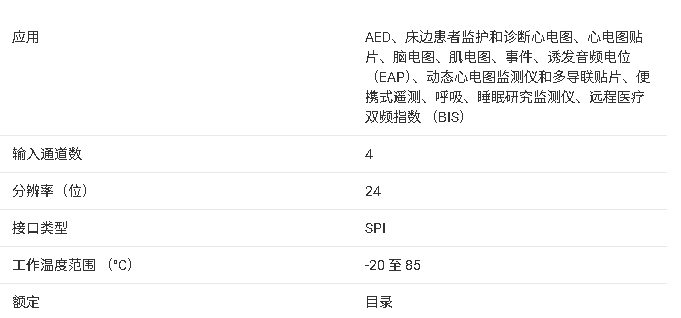

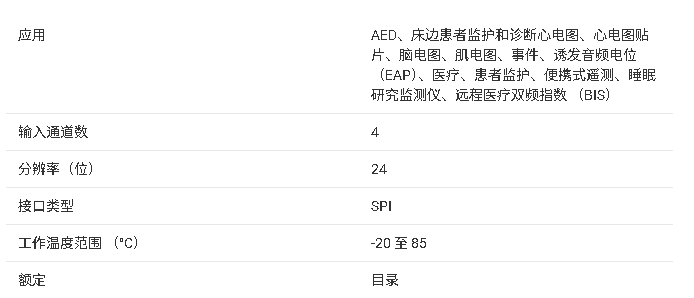

該AFE1594是多通道、同步采樣、24位、增量Σ (ΔΣ)模數(shù)轉(zhuǎn)換器(ADC)系列,具有內(nèi)置可編程增益儀表放大器(INA)、內(nèi)部基準電壓源和片內(nèi)PLL...

2025-10-23 標簽:adcpll模數(shù)轉(zhuǎn)換器 680 0

AFE159P4數(shù)據(jù)手冊完整總結(jié)

該AFE1594是一系列多通道、同步采樣、24 位、三角積分 (ΔΣ) 模數(shù)轉(zhuǎn)換器 (ADC),具有內(nèi)置可編程增益儀表放大器 (INA)、內(nèi)部基準電壓源...

2025-10-23 標簽:adcpll模數(shù)轉(zhuǎn)換器 602 0

?AFE159x系列數(shù)據(jù)手冊完整總結(jié)

該AFE1594是一系列多通道、同步采樣、24 位、三角積分 (ΔΣ) 模數(shù)轉(zhuǎn)換器 (ADC),具有內(nèi)置可編程增益儀表放大器 (INA)、內(nèi)部基準電壓源...

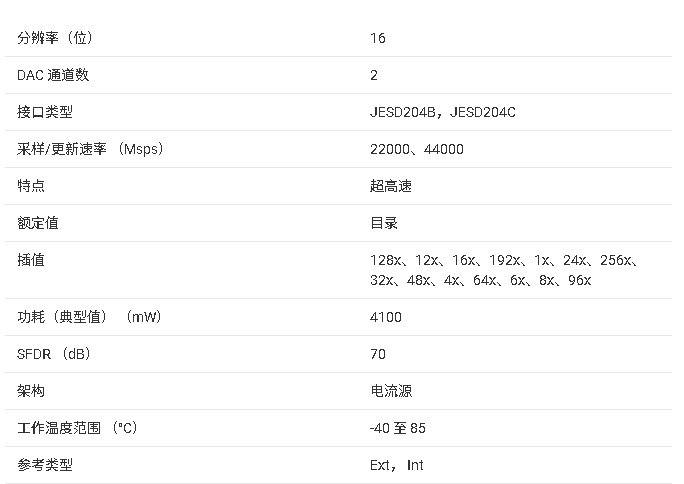

該DAC39RF20是一款具有 16 位分辨率的單通道和雙通道數(shù)模轉(zhuǎn)換器 (DAC)。通過外部全速率時鐘,這些器件在單邊沿采樣模式(NRZ 和 RF)下...

2025-10-22 標簽:數(shù)據(jù)傳輸dacpll 1.1k 0

【FPGA 開發(fā)分享】如何在 Vivado 中使用 PLL IP 核生成多路時鐘

EsteemPCB Academy 是一個專注于 FPGA、嵌入式系統(tǒng)與硬件開發(fā)的技術(shù)學(xué)習(xí)平臺,致力于通過通俗易懂的課程內(nèi)容,幫助工程師和學(xué)習(xí)者快速掌握...

2025-09-28 標簽:FPGApllFPGA開發(fā) 7.1k 0

?CDC2536 鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)?

CDC2536是一款高性能、低偏斜、低抖動的時鐘驅(qū)動器。它使用鎖相環(huán) (PLL) 將時鐘輸出信號在頻率和相位上精確對齊到時鐘輸入 (CLKIN) 信號。...

?CDC536 3.3V鎖相環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

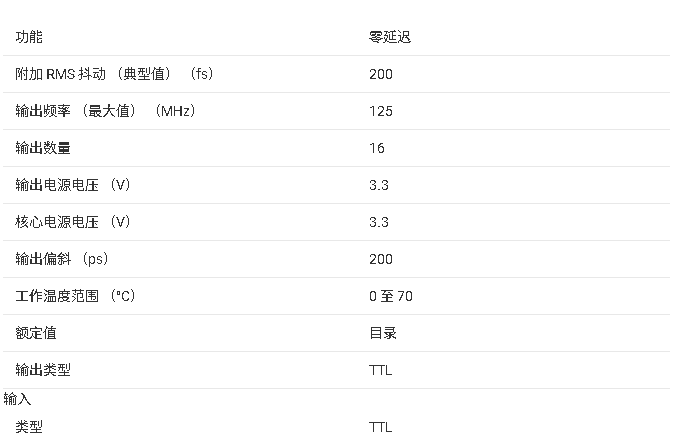

CDC536 是一款高性能、低偏斜、低抖動的時鐘驅(qū)動器。它使用鎖相環(huán) (PLL) 來精確地 在頻率和相位上,將時鐘輸出信號與時鐘輸入 (CLKIN) 信...

?CDC516 3.3V相位鎖定環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

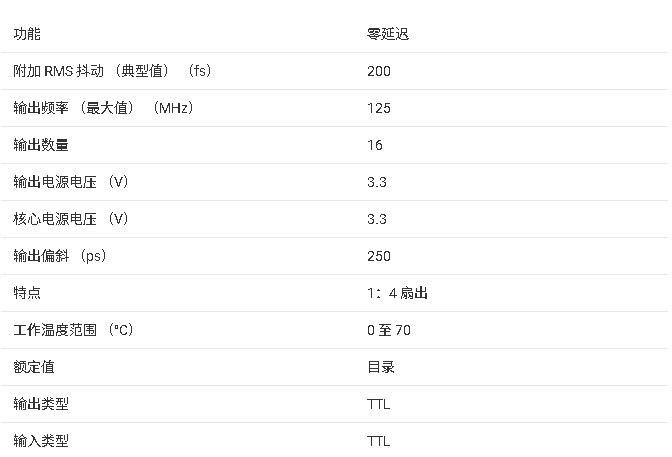

CDC516 是一款高性能、低偏斜、低抖動、鎖相環(huán)時鐘驅(qū)動器。它使用鎖相環(huán) (PLL) 將反饋輸出 (FBOUT) 與時鐘 (CLK) 輸入信號在頻率和...

?CDC509 3.3V相位鎖定環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

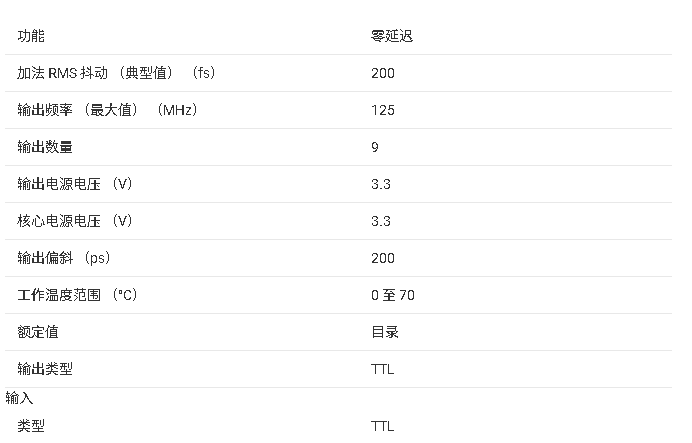

CDC509 是一款高性能、低偏斜、低抖動、鎖相環(huán) (PLL) 時鐘驅(qū)動器。它使用 PLL 在頻率和相位上將反饋 (FBOUT) 輸出精確對齊到時鐘 (...

?CDC2516 3.3V相位鎖定環(huán)時鐘驅(qū)動器技術(shù)文檔總結(jié)

該CDC2516是一款高性能、低偏斜、低抖動、鎖相環(huán) (PLL) 時鐘驅(qū)動器。它使用 PLL 在頻率和相位上將反饋輸出 (FBOUT) 與時鐘 (CLK...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |