一、PLL原理

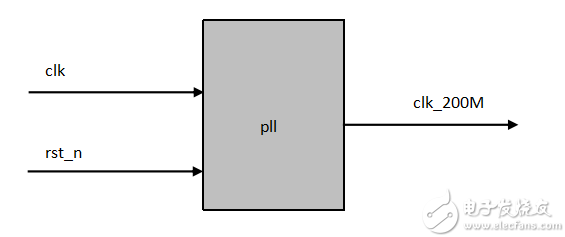

鎖相環(PLL,Phase Lock Loop)的主要作用是實現輸出時鐘對輸入參考時鐘的相位與頻率的精確跟蹤和同步。鎖相環(PLL)的主要模塊包括相位頻率檢測器(PFD)、電荷泵、環路濾波器、壓控振蕩器(VCO)以及計數器,例如反饋計數器(M)、預分頻計數器(N)和后分頻計數器(C)。鎖相環的架構取決于您在設計中所使用的器件。典型的PLL結構如下所示(參考Altera文檔Altera Phase-Locked Loop (Altera PLL) IP Core User Guide):

用戶可以重新配置計數器,修改電荷泵和環路濾波器組件來實時更新輸出時鐘頻率、PLL帶寬和相移,且無需重配置整個 FPGA。本案例主要是配置不同的頻率輸出,主要關注這些計數器的重配置:

預分頻計數器N

反饋計數器M

后分頻計數器C

關于輸出頻率fout和輸入頻率fin之間的換算公式如下:

pll_controller.v代碼里面給出了不同頻率下M、N、C的經驗值:

二、 ALTPLL RECONFIG IP

本案例是通過一個PLL控制器(pll_controller.v)根據不同的顯示模式(mode)將不同的參數傳輸給ALTPLL RECONFIG IP處理后繼而傳遞給ALTPLL IP以實現PLL輸出頻率的改變。

如下是PLL控制器、ALTPLL RECONFIG IP和ALTPLL IP的RTL視圖:

ALTPLL RECONFIG IP是Altera 公司提供的 IP核,用于動態實時地重新配置 ALTPLL IP。借助該 IP 核,無需重新配置整個 FPGA,就可以實時更新 ALTPLL 的輸出時鐘頻率、PLL 帶寬和相移等參數。

在實際應用中可將ALTPLL RECONFIG IP、單口 ROM 和.mif 文件三者配合工作來實現對 ALTPLL IP 內核中參數的更新,也可以設計一個PLL控制器直接對ALTPLL RECONFIG IP的參數進行更新。本案例選擇后者。

PLL控制器、ALTPLL RECONFIG IP和ALTPLL IP之間的關系簡化一下得到如下框圖:

PLL控制器通過mgmt接口(mgmt代表管理接口Management Interface)控制ALTPLL RECONFIG IP,mgmt 接口采用的是 Avalon-MM(Avalon Memory-Mapped)協議,它是一種簡單的內存映射接口協議,支持主從機之間的通信,適合用于配置、控制和數據傳輸等場景。

Avalon-MM的讀寫接口核心信號包括:

地址線(address):指定要訪問的從機內部寄存器或存儲單元地址。

數據線(writedata/readdata):寫操作時傳遞要寫入的數據,讀操作時返回讀取的數據。

寫使能(write):高電平有效時,將writedata 寫入 address 指定的位置。讀使能(read):高電平有效時,從address 指定的位置讀取數據到 readdata。

通過Avalon-MM 協議,主設備可以通過地址、數據和控制信號(如讀 / 寫使能)與 ALTPLL_RECONFIG IP 進行交互,完成對 PLL 配置參數的讀取和修改。更多關于Avalon-MM協議請參考Altera文檔1. Introduction to the Avalon Interface Specifications

基于Avalon-MM接口的PLL動態重配置波形舉例如下(本教程采用polling模式):

PLL控制器則是按照上述時序對ALTPLL_RECONFIG IP 進行控制,其中與頻率重配置相關的寄存器描述如下(更多詳情參考Altera文檔1.1.1.4.1. Fractional PLL Dynamic Reconfiguration Registers and...):

| 寄存器名稱 | 位寬 | 地址 | 設置 | 讀/寫 |

| Mode Register | 1 | 0 |

設置0選擇Waitrequest模式 設置1選擇polling模式 |

Read/Write |

| Status Register | 1 | 1 | 讀取0代表busy,讀取1代表配置完成 | Read |

| Start Register | 1 | 2 | 寫0或者寫1都可以開啟PLL 重配置 | Write |

| N Counter | 18 | 3 |

N_counter[7:0]=low_count N_counter[15:8]=high_count Total_div=high_count+low_count N_counter[16]=0, fREF= fIN/Total_div N_counter[16] = 1,選擇bypassed N_counter[17]=0,偶分頻 N_counter[17]=1,奇分頻 |

Read/Write |

| M Counter | 18 | 4 |

M_counter[7:0]=low_count M_counter[15:8]=high_count Total_div=high_count+low_count M_counter[16]=0,fFB=fVCO/Total_div M_counter[16]=1,選擇bypassed M_counter[17]=0,偶分頻 M_counter[17] =1,奇分頻 |

Read/Write |

| C Counter | 23 | 5 |

C_counter[7:0]=low_count C_counter[15:8]=high_count Total_div=high_count+low_count C_counter[16]=0, fOUT= fVCO/Total_ div C_counter[16] = 1,選擇bypassed C_counter[17]=0,偶分頻 C_counter[17]=1,奇分頻 C_counter[22:18],范圍00000到10001 (0–17)沒用來指示選哪個Ccounter,比如選擇C2,則設置C_ counter[22:18]=00010 |

Read/Write |

| BandwidthSetting | 4 | 8 | 參考pll-reconfiguration-calculator.xlsx | Read/Write |

| ChargePump Setting | 3 | 9 | 參考pll-reconfiguration-calculator.xlsx | Read/Write |

三、ALTPLL IP

ALTPLL IP是Altera 公司提供的鎖相環 IP 核,通過振蕩器產生的波形相位匹配輸入信號相位來工作,可實現時鐘倍頻、分頻、相位偏移和可編程占空比等功能,為 FPGA 系統提供穩定的時鐘信號。

設置ALTPLL IP時其參考時鐘填入50MHz,輸出時鐘填入162MHz(上電后配置FPGA時ALTPLL 默認輸出162MHz):

在PLL IP 的Settings選項勾選Enable dynamic reconfiguration of PLL,就會多出reconfig_to_pll 和 reconfig_from_pll 這兩組信號:

reconfig_to_pll:由ALTPLL RECONFIG IP 輸出,發送到 ALTPLL IP,用于傳遞配置指令和參數。例如,動態修改 PLL 的輸出頻率、相位偏移、帶寬等參數的控制信號和數據,都是通過這組信號從配置 IP 傳輸到 PLL 核。

reconfig_from_pll:由ALTPLL IP 輸出,反饋到 ALTPLL RECONFIG IP,用于傳遞PLL 的狀態信息。例如,PLL 的鎖定狀態(locked)、配置是否成功的響應信號等,幫助配置 IP 確認操作結果或監測 PLL 工作狀態。

這兩組信號是專用的內部接口(非Avalon 協議),僅用于兩個 IP 核之間的直接通信,實現 PLL 動態重配置的底層數據交互,無需用戶手動干預信號時序。在IP例化時,ALTPLL_RECONFIG IP實例的reconfig_to_pll[63:0]總線連接到 ALTPLL IP實例的reconfig_to_pll[63:0]總線,同時將 ALTPLL IP實例的reconfig_from_pll[63:0]總線連接到 ALTPLL_RECONFIG IP實例的reconfig_from_pll[63:0]總線即可。

-

鎖相環

+關注

關注

36文章

635瀏覽量

91113 -

濾波器

+關注

關注

162文章

8412瀏覽量

185712 -

pll

+關注

關注

6文章

982瀏覽量

138175 -

計數器

+關注

關注

32文章

2316瀏覽量

98180

原文標題:4-DE10-Nano的HDMI彩條顯示案例(分辨率可切換)—— ALTPLL IP與ALTPLL RECONFIG IP介紹

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA學習系列:14. 鎖相環pll設計

Altera公司鎖相環IP核介紹

Altera公司鎖相環IP核介紹

評論