操作步驟

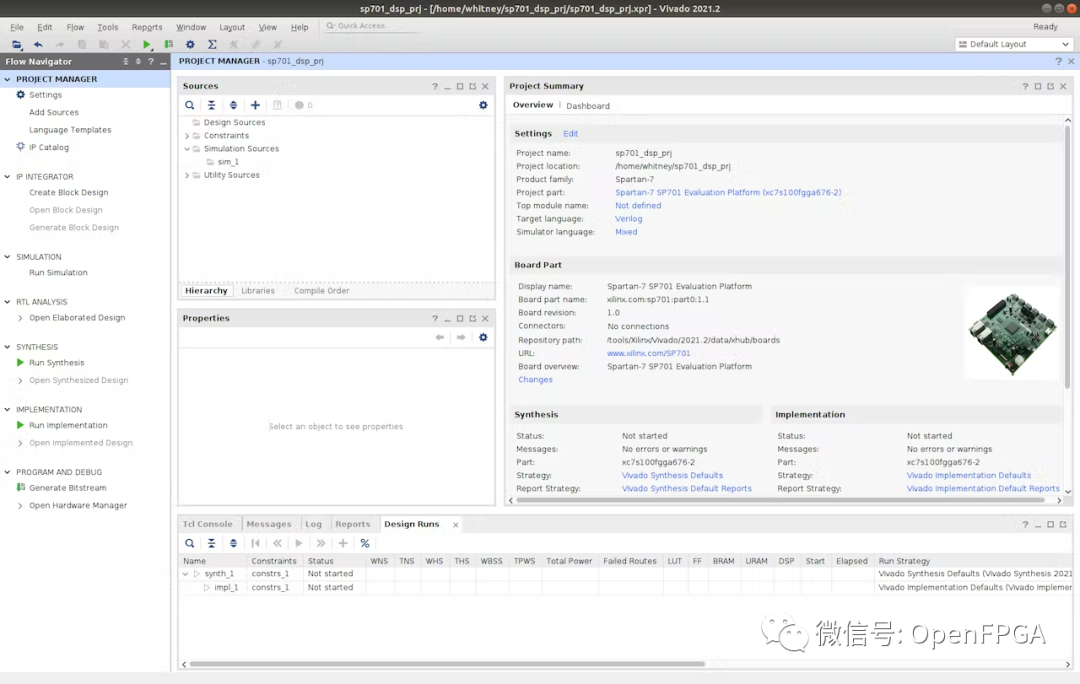

1.?新建工程項(xiàng)目

1)?雙擊桌面圖標(biāo)打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2)?點(diǎn)擊‘Create Project’,或者單擊File>New Project創(chuàng)建工程文件;

3)?將新的工程項(xiàng)目命名為‘lab3’,選擇工程保存路徑,勾選‘Create project subdirectory’,創(chuàng)建一個(gè)新的工程文件夾,點(diǎn)擊Next繼續(xù);

4)?選擇新建一個(gè)RTL工程,勾選Do not specify sources at this time(不指定添加源文件),先不添加源文件。點(diǎn)擊 Next繼續(xù);

5)?選擇目標(biāo)FPGA器件:xc7a35tcpg236-1或Basys3;

6)?最后在新工程總結(jié)中,檢查工程創(chuàng)建是否有誤。沒有問題,則點(diǎn)擊Finish,完成新工程的創(chuàng)建。

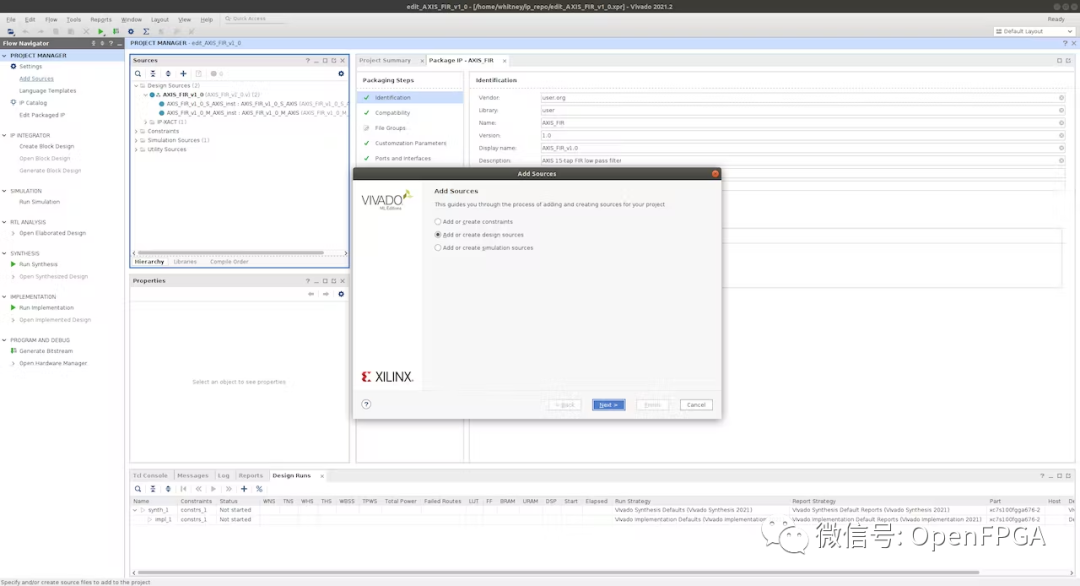

2.?添加源文件

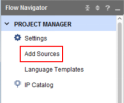

1)?在左側(cè)Flow Navigator中展開PROJECT MANAGER,選擇‘Add Sources’;

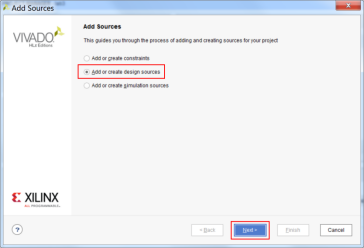

2)?在Add Sources窗口中,選擇‘Add or create design sources’,點(diǎn)擊Next;

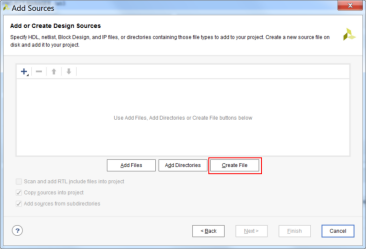

3)?點(diǎn)擊‘Create File’,創(chuàng)建源文件;

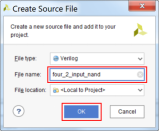

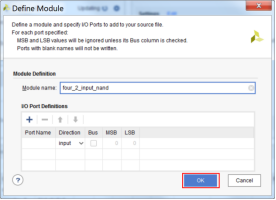

4)?將源文件命名為‘four_2_input_nand’,點(diǎn)擊OK;

5)?點(diǎn)擊Finish,完成源文件創(chuàng)建;

6)?在模塊端口(I/O)定義窗口不做設(shè)置,點(diǎn)擊OK繼續(xù);

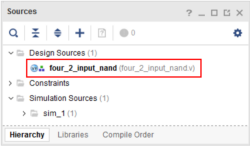

7)?在Sources窗格中,雙擊打開‘four_2_input_nand.v’文件,開始編輯;

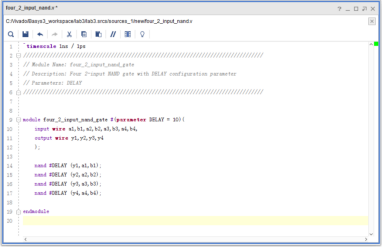

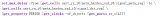

8)?在右側(cè)的文本編輯框中,編輯代碼如下圖所示:

源代碼如下:

?

`timescale 1ns / 1ps module?four_2_input_nand_gate?#(parameter?DELAY?=?10)( ????input?wire?a1,b1,a2,b2,a3,b3,a4,b4, ????output?wire?y1,y2,y3,y4 ???); ????nand?#DELAY?(y1,a1,b1); ????nand?#DELAY?(y2,a2,b2); ????nand?#DELAY?(y3,a3,b3); ????nand?#DELAY?(y4,a4,b4); ???? endmodule

?

9)?編輯完成后,Ctrl+S保存;

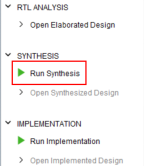

10)?在Flow Navigator中,展開SYNTHESIS,點(diǎn)擊‘Run Synthesis’。彈出窗口使用默認(rèn)選項(xiàng),點(diǎn)擊OK開始綜合。

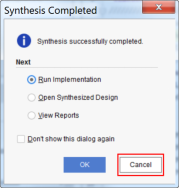

11)?綜合完成后,點(diǎn)擊‘Cancel’關(guān)閉窗口。

3.?IP封裝

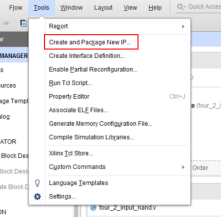

1)?在頂部工具欄中,點(diǎn)擊Tools>Create and Package New IP;

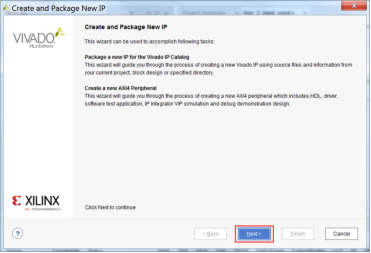

2)?彈出的向?qū)Т翱冢c(diǎn)擊Next繼續(xù);

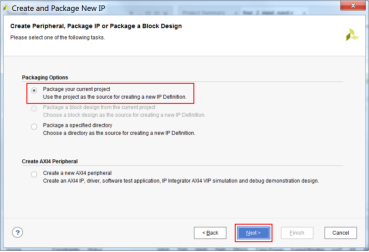

3)?選擇對當(dāng)前工程進(jìn)行封裝,點(diǎn)擊Next繼續(xù);

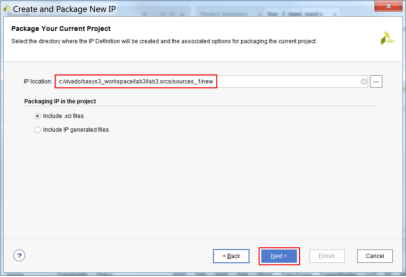

4)?選擇IP保存路徑,保持默認(rèn)設(shè)置,點(diǎn)擊Next繼續(xù);

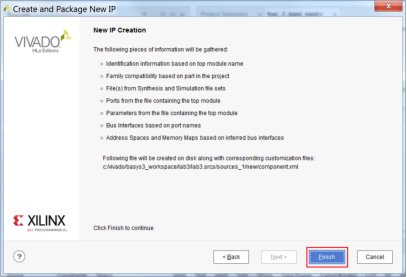

5)?點(diǎn)擊Finish完成設(shè)置;

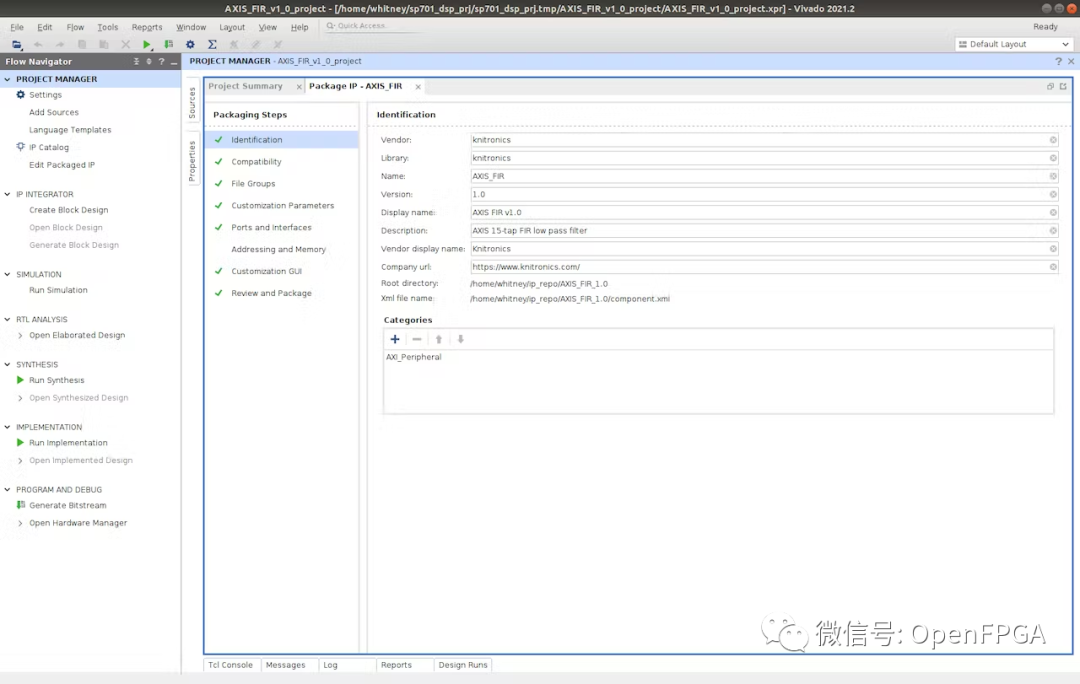

6)?設(shè)置IP參數(shù);

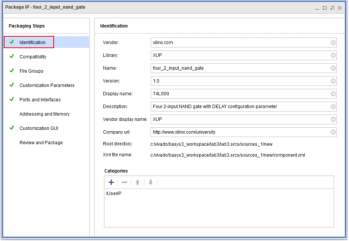

6.1 在右側(cè)Package IP窗口中,選擇Identification,按下圖設(shè)置:

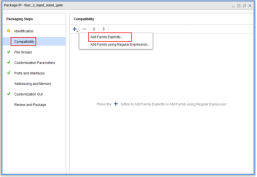

6.2 選擇Compatibility,如果已經(jīng)存在artix7、kintex7、spartan7和zynq可以略過此步。否則需要按以下步驟添加:

6.2.1?選擇‘Add Family Explicity’

6.2.2 在彈出窗口中勾選相應(yīng)的系列,Life-cycle選擇‘Production’。

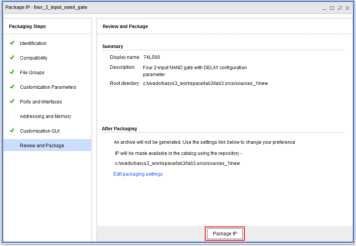

6.3 點(diǎn)擊OK完成添加,選擇Review and Package,點(diǎn)擊‘Package IP’完成對74LS00 IP的封裝。

6.4 完成后,系統(tǒng)提示封裝成功。

4. 基于Tcl的封裝流程:

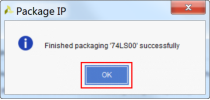

1)?打開Vivado 2017.2,在底部Tcl Console中依次執(zhí)行下列步驟完成對74LS00 IP的封裝;

2)?在命令框依次輸入如下命令:

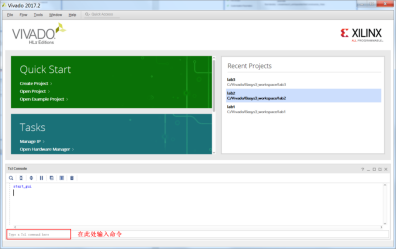

2.1?cd C:/Basys3_workshop/sources/lab3/

進(jìn)入到工作文件夾,文件夾中包含封裝IP所需的源文件

2.2?set ip_name 74LS00 ?設(shè)置IP名稱

2.3?set source_files four_2_input_nand.v ?設(shè)置源文件

2.4?set description "Four 2-input NAND gate with DELAY configuration parameter" ?對IP進(jìn)行功能描述

2.5?set readme_file readme.txt ?添加readme文本文件

2.6 set logo_file xup_IPI.png ?設(shè)置IP logo圖片

2.7 source ./package_ip.tcl

運(yùn)行工作目錄下的Tcl文件,進(jìn)行IP封裝

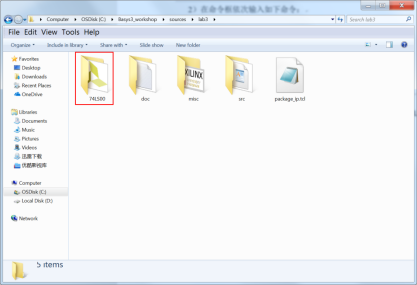

1)?完成之后,封裝完成的74LS00 IP保存在C:/Basys3_workshop/sources/lab3/74LS00文件夾內(nèi)

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論