聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133425 -

IP

+關注

關注

5文章

1862瀏覽量

155827 -

Vivado

+關注

關注

19文章

857瀏覽量

71104

發布評論請先 登錄

相關推薦

熱點推薦

學會用Signal Tap邏輯分析儀查看信號波形

Signal Tap Logic Analyzer是Quartus Prime設計軟件中自帶的系統級調試工具,它可以在FPGA設計中采集和顯示實時的信號行為;當配置完FPGA后,無需額外的I/O引腳即可檢查器件操作期間內部信號的

利用vivado實現對e200_opensource 蜂鳥E203一代的仿真

最后,點擊run simulation進行 行為級仿真

得到最后的仿真結果如圖所示

本文參考論壇內另外兩篇文章:

[1] 在Windows環境下用Vivado調試E203作者:leon

[2

發表于 10-31 06:14

vivado時序分析相關經驗

-logic_level_distribution -logic_level_dist_paths 5000 -name design_analysis_prePlace”此tcl命令可以對設計中的邏輯級數分布

發表于 10-30 06:58

vcs和vivado聯合仿真

我們在做參賽課題的過程中發現,上FPGA開發板跑系統時,有時需要添加vivado的ip核。但是vivado仿真比較慢,vcs也不能直接對添加了vivado

發表于 10-24 07:28

Vivado浮點數IP核的握手信號

Vivado浮點數IP核的握手信號

我們的設計方案中,FPU計算單元將收到的三條數據和使能信號同步發給20多個模塊,同時只有一個模塊被時鐘使能,進行計算,但結果都會保留,發給數選。計算單元還需接受

發表于 10-24 07:01

Vivado浮點數IP核的一些設置注意點

Vivado浮點數IP核的一些設置注意點

我們在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定義其計算種類及多模式選擇。有時多種計算可以用同一

發表于 10-24 06:25

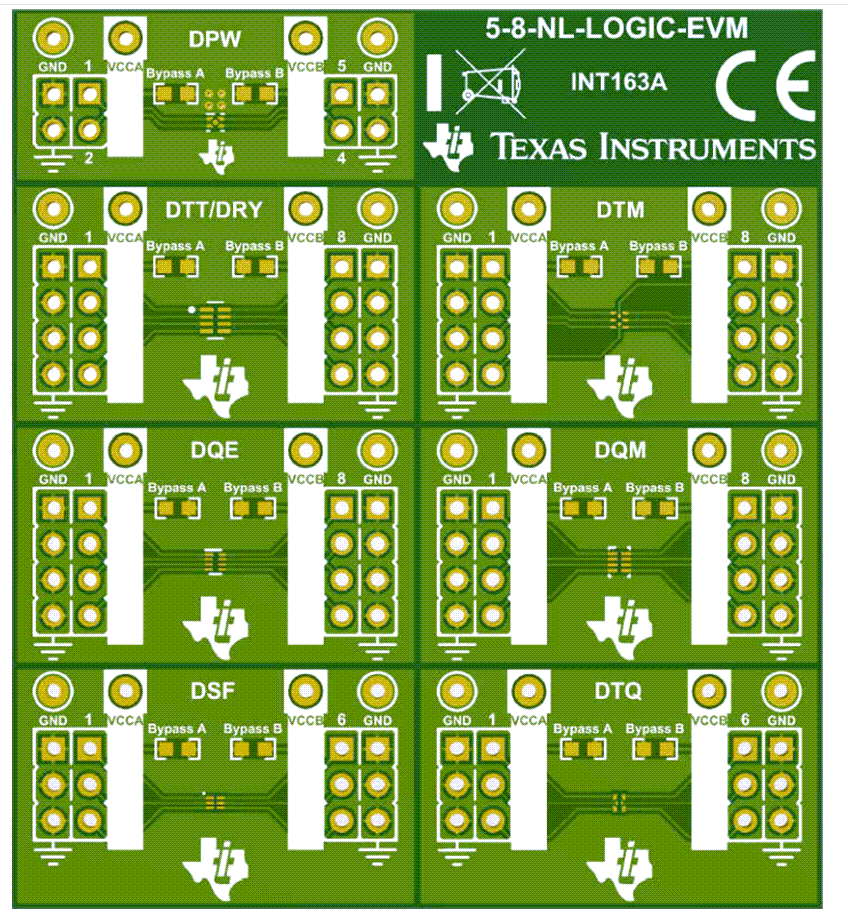

Texas Instruments 5-8-NL-LOGIC-EVM邏輯轉換評估模塊技術解析

Texas Instruments 5-8-NL-LOGIC-EVM邏輯和轉換評估模塊 (EVM) 設計用于支持任何邏輯或轉換器件。它支持DTT (X1QFN-8)、DRY (USON-6)、DPW

AMD Vivado ChipScope助力硬件調試

許多硬件問題只有在整個集成系統實時運行的過程中才會顯現出來。AMD Vivado ChipScope 提供了一套完整的調試流程,可在系統運行期間最大限度提升對可編程邏輯的觀測能力,助力設計調試

FPGA調試方式之VIO/ILA的使用

在Vivado中,VIO(Virtual Input/Output)是一種用于調試和測試FPGA設計的IP核,它允許設計者通過JTAG接口實時讀取和寫入FPGA內部的寄存器,從而檢查設計的運行狀態并修改其行為。VIO

SDRAM控制器設計之signaltap調試

Signal Tap Logic Analyzer是Intel Quartus Prime設計軟件中自帶的新一代系統級調試工具,它可以在FPGA設計中采集和顯示實時的信號行為。當設計在FPGA上全速運行時,無需額外的I/O引腳即

如何使用Vivado Logic Analyzer與邏輯調試IP進行交互

如何使用Vivado Logic Analyzer與邏輯調試IP進行交互

評論