本文主要是Lattice公司市場總監Shakeel Peera給大家談面對競爭激烈的FPGA市場,Lattice公司將持續優化FPGA成本和功耗。

2012-08-14 14:12:55 1159

1159

的技巧。本文提出的方法用于架構設計和前段設計的初期,如功耗估計、低功耗架構優化和時鐘門控等。##功耗的估算##功耗的優化##架構考慮及RAM的功耗優化##時鐘樹單元/連線##時序分析##測試結果

2014-03-25 09:58:50 17915

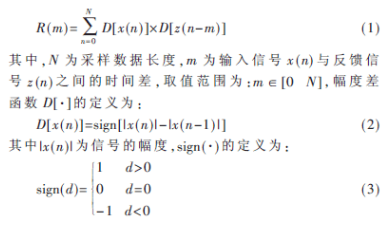

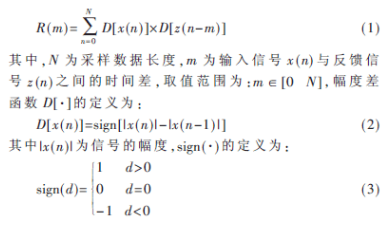

17915 根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。

2014-09-01 11:26:40 3313

3313 以下是筆者一些關于FPGA功耗估計和如何進行低功耗設計的知識。##關于FPGA低功耗設計,可從兩方面著手:1)算法優化;2)FPGA資源使用效率優化。

2014-12-17 09:27:28 9945

9945 在項目設計初期,基于硬件電源模塊的設計考慮,對FPGA設計中的功耗估計是必不可少的。筆者經歷過一個項目,整個系統的功耗達到了100w,而單片FPGA的功耗估計得到為20w左右,有點過高了,功耗過高

2017-12-19 09:29:14 7052

7052

基于FPGA vivado 17.2 的數字鐘設計

2018-06-08 09:41:47 11516

11516

仿真功能概述 仿真FPGA開發中常用的功能,通過給設計注入激勵和觀察輸出結果,驗證設計的功能性。Vivado設計套件支持如下仿真工具:Vivado Simulator、Questa、ModelSim

2020-12-31 11:44:00 6234

6234

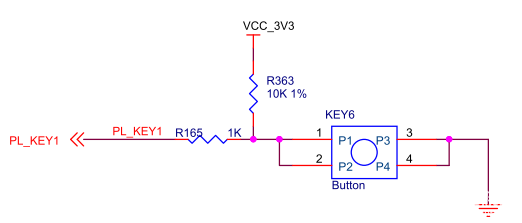

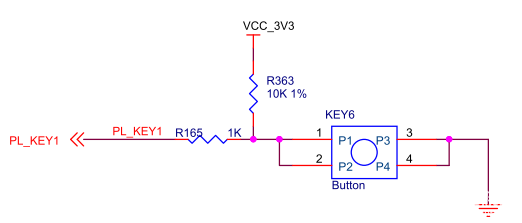

按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivado RTL ANALYSIS的使用。

2021-01-22 09:46:34 2922

2922

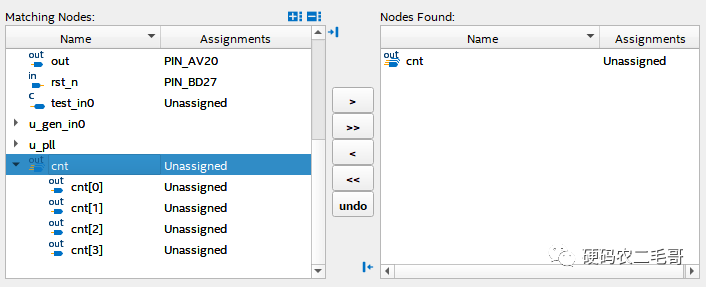

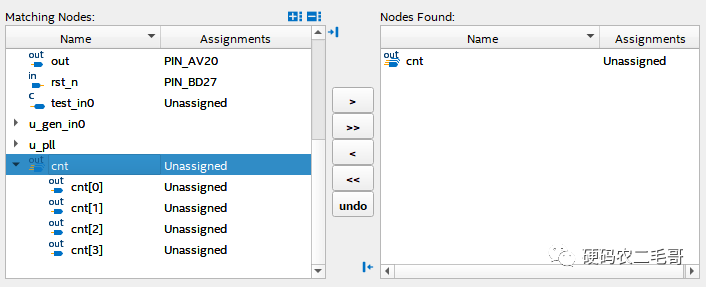

本文分別對quartus和vivado防止信號被優化的方法進行介紹。

2023-05-25 11:25:46 5016

5016

Suhel?Dhanani AMD 自適應 SoC 與 FPGA 事業部軟件營銷總監 在設計規模和復雜性不斷增長的世界里,SoC 和 FPGA 設計需要以更低功耗提供更高性能的情況將繼續在行業中存在

2023-07-12 08:15:04 1782

1782 FPGA的功耗由4部分組成:上電功耗、配置功耗、靜態功耗和動態功耗。一般的FPGA都具有這4種功耗,但是Actel Flash FPGA由于掉電數據不丟失,無需配置芯片,所以上電后不需要一個很大的啟動電流,也不需要配置過程,只有靜態功耗和動態功耗,沒有上電功耗和配置功耗。

2024-07-18 11:11:00 3195

3195

FPGA功耗的基本概念,如何降低FPGA功耗?IGLOO能夠做到如此低的功耗是因為什么?

2021-04-30 06:08:49

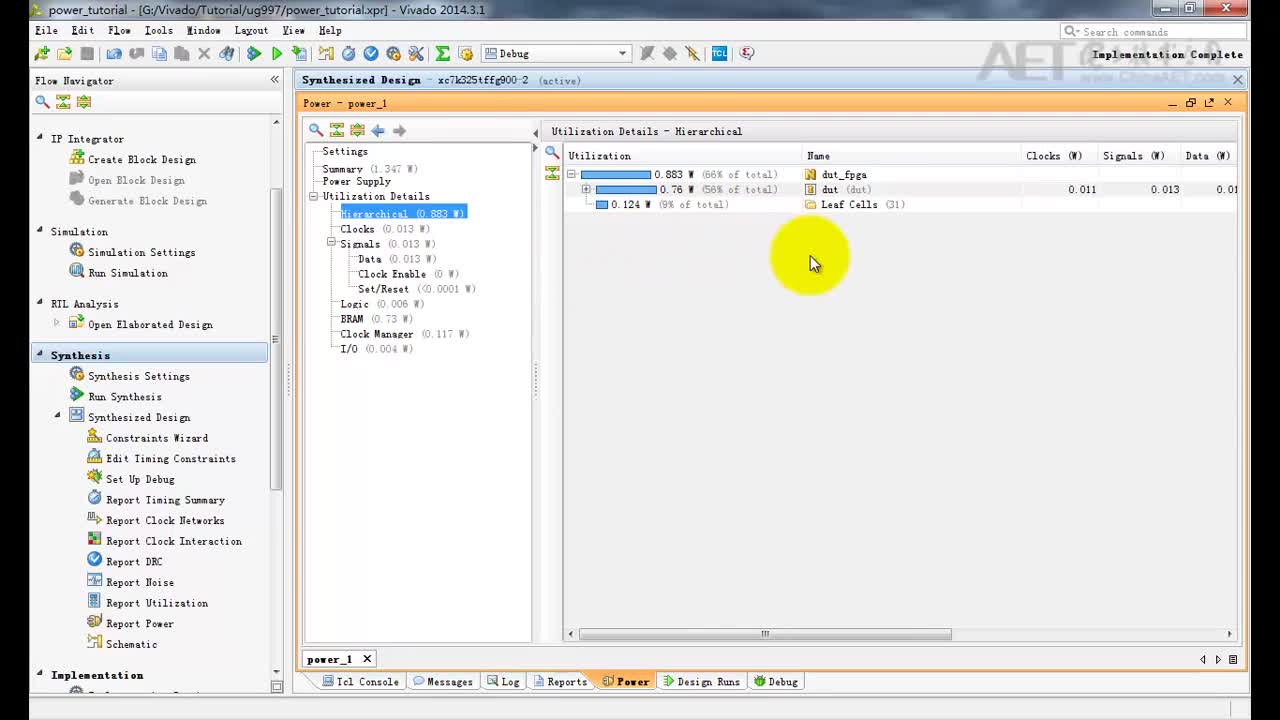

,IP,BUFG的Estimated Utilization,請問表示什么內容?③查到在Vivado下進行功耗估計有兩種方法,一種是向量模式,需要提供SAIF(Switching Activity

2018-02-25 16:03:46

Utilization的圖表,內有LUT,FF,IP,BUFG的Estimated Utilization,請問表示什么內容?③查到在Vivado下進行功耗估計有兩種方法,一種是向量模式,需要提供SAIF

2018-02-25 21:12:01

在做vivado綜合時和FPGA下載程序時,我們碰到以下問題,并找出了對應的解決方案。

1.could not open include file”e203_defines.v”問題

在做

2025-10-24 07:12:12

和多種高速SERDES信道,不僅靜態和動態功耗也隨之增加,對FPGA設計的電源要求也非常復雜,這對系統功耗要求提出更多挑戰,盡可能地估算和優化FPGA的功耗成為應對挑戰的關鍵。 FPGA的主要功耗

2018-10-23 16:33:09

EDA技術具有什么特征?FPGA是什么原理?FPGA設計應用及優化策略基于VHDL的FPGA系統行為級設計

2021-04-15 06:33:58

嗨,在網絡實施期間,當我將用戶ILA端口從3個端口擴展到11個端口時,會生成以下消息:[Vivado_Tcl 4-131] Power Optimization遇到異常:ERROR:[Common

2018-11-08 11:29:12

如上圖所示用的是Vivado2014.4,最后生成完bit文件后,顯示了這個。結溫過高?仔細看report里面電流竟然30+A。。。我想問一下大概是什么原因導致了這種狀況的出現呢,然后解決這個問題那些地方的代碼可以優化呢?剛學FPGA不久,望各位大蝦指教

2015-03-23 17:01:15

轉自:VIVADO時序分析練習時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

優化 FPGA HLS 設計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設計性能。

介紹

高級設計能夠以簡潔的方式捕獲設計,從而

2024-08-16 19:56:07

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

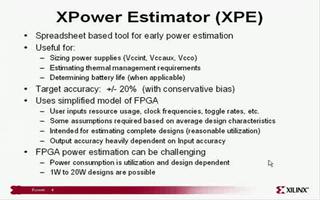

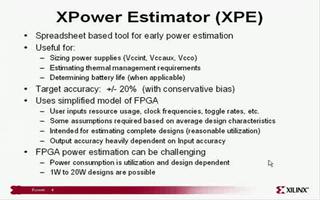

是在映射或布局和布線后設計的基礎上對器件功耗進行估計的。 對于成熟的投產的 FPGA 和 CPLD,XPower 計算出的功耗估計的平均設計批量誤差 (suite error) 小于 10%。它將

2012-01-11 11:59:44

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2022-02-07 08:02:04

基于FPGA vivado 17.2 的數字鐘設計目的:熟悉vivado 的開發流程以及設計方法附件:

2017-12-13 10:16:06

你好ISE的合成與實現,最終資源利用分析報告正常。現在在Vivado中,在實現邏輯優化(opt_design)的第一步(實現)中投入了大量資源來優化模塊(建議邏輯單元不加載),但是當ISE實現沒有被

2018-10-24 15:23:00

怎么實現基于LFSR優化的BIST低功耗設計?

2021-05-13 06:21:01

大家好我是剛剛來這的實習生(拱手)。最近在看 基于FPGA的H264運動估計算法優化與實現 方面的東西,他提出了一個概念:運動矢量。這是如何得到的?如何理解?有什么用?附錄原文中的一些東西:基于塊

2015-04-28 11:51:04

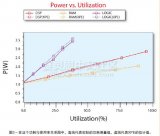

的:1)降低θJA:熱阻抗取決于芯片與環境的熱傳導效率,可通過加散熱片或者風扇減小熱阻抗圖12)減小PD:通過優化FPGA設計,降低總功耗,這也是本文重點講解的部分。2.功耗估計在講解低功耗設計之前,介紹

2014-08-21 15:31:23

您好Xilinx的用戶和員工,我們正在考慮購買Zynq 7000用于機器視覺任務。我們沒有編程FPGA的經驗,并希望使用Vivado HLS來指導和加速我們的工作。關于這種方法的一些問題:您對

2020-03-25 09:04:39

`Hi,我來自一個叫Plunify的工程師團隊,一直致力于使用機器學習來優化時序。把云計算應用到 FPGA 的概念最近剛興起,亞馬遜云的F1實例也受到越來越多的關注。趁著賽靈思和亞馬遜開始合作推出

2017-11-22 10:51:18

給設計F2812電源電路,不知道F2812的功耗如何估計?我知道FPGA芯片廠商有對應的EXCEL表可以估計芯片的功耗,不知道DSP有沒有這樣的工具?大家平時是如何估計DSP的功耗的?

2018-11-22 10:07:12

嗨,我發現Vivado webpack版本v2014.4不支持安裝在NetFPGA SUME板上的eh Virtex-7 690 FPGA。我想知道購買NetFPGA SUME板的任何許可證捆綁

2018-12-18 10:36:47

FPGA怎么選擇?針對功耗和I/O而優化的FPGA介紹

2021-05-06 09:20:34

(1)門級電路的功耗優化綜述 門級電路的功耗優化(Gate Level Power Optimization,簡稱GLPO)是從已經映射的門級網表開始,對設計進行功耗的優化以滿足功耗的約束,同時

2021-11-12 06:14:26

針對色噪聲背景下MIMO塊平坦衰落信道進行了估計和優化,并以信道估計的優化結果為基礎,分析了估計信道的互信息量下限和系統的容量下限,提出了利用注水算法來優化發射端

2009-05-10 11:46:36 17

17 本文將介紹FPGA的功耗、流行的低功耗功能件以及影響功耗的用戶選擇方案,并探討近期的低功耗研究,以洞察高功率效率FPGA的未來趨勢。

功耗的組成部分

2010-08-27 10:57:21 2137

2137

自從Xilinx推出FPGA二十多年來,研發工作大大提高了FPGA的速度和面積效率,縮小了FPGA與ASIC之間的差距,使FPGA成為實現數字電路的優選平臺。今天,功耗日益成為FPGA供應商及其客戶關注的問題。降低FPGA功耗是縮減封裝和散熱成本、提高器件可靠性以及打開移

2011-03-15 14:58:34 31

31 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 改進粒子群優化在壓縮感知DOA估計中的應用_趙宏偉

2017-01-07 18:39:17 0

0 參加 ?FPGA? 功率優化班,將幫助您創建更高電源效率的 ?FPGA? 設計。通過本課程的學習,將有助于您的設計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 320

320 隨著xilinx公司進入20nm工藝,以堆疊的方式在可編程領域一路高歌猛進,與其配套的EDA工具——新一代高端FPGA設計軟件VIVADO也備受關注和飽受爭議。

2017-02-11 19:08:00 5542

5542 有關FPGA——VIVADO15.4開發中IP 的建立

2017-02-28 21:04:35 16

16 有一種新方法可用于測量真實FPGA器件的功耗估計值 現代的FPGA 芯片能夠開發高性能應用,但在這些設計中電源管理通常是一大限制因素。FPGA 器件的資源使用最能決定設計的容量和處理速度,但是增加

2017-11-18 01:14:02 8016

8016

其實Tcl在Vivado中還有很多延展應用,接下來我們就來討論如何利用Tcl語言的靈活性和可擴展性,在Vivado中實現定制化的FPGA設計流程。 基本的FPGA設計實現流程 FPGA的設計流程簡單來講,就是從源代碼到比特流文件的實現過程。大體上跟IC設計流程類似,可以分為前端設計和后端設計。

2017-11-18 01:48:01 4100

4100

Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握

2017-11-18 03:52:01 5363

5363

根據BPSK調制信號調制機理和平方倍頻法原理,在FPGA平臺上設計實現了BPSK調制信號載波頻率估計單元。利用ModelSim仿真環境對載頻估計功能進行仿真,驗證了平方倍頻法對BPSK信號進行載波

2017-11-18 05:13:05 4539

4539

為設計尋找“完美”FPGA 的重要性日漸升級,其中功耗已成為主要考慮因素。功耗管理在大部分應用中都非常關鍵。某些標準已為單卡或者單個系統設定了功耗上限。鑒于此,設計人員必須在設計過程中更早地對功耗

2017-11-22 15:03:01 3826

3826 設計者通過優化自己的設計和注意某些具體情況,可以在FPGA設計中實現低功耗。通過一款具體的FPGA產品了解其低功耗的解決方式,為設計提供了指導。FPGA均可在相應的操作環境下進行仿真,從而了解功耗

2017-11-23 10:37:23 1715

1715 本文首先與實測系統功耗進行對比,驗證了Xilinx公司ISE軟件包中FPGA功耗估算工具XPower的準確性。然后對FPGA設計中影響系統功耗的幾個相互關聯的參數進行取樣,通過軟件估算不同樣點下的系統功耗,找到功耗最低的取樣點,得到最佳設計參數,從而達到優化系統設計的目的。

2017-11-25 09:26:44 2338

2338 本視頻演示了 Xilinx 功耗估計器電子數據表工具

2018-06-05 13:45:00 8589

8589

本演示中,我們將介紹利用 XPower 估計器(XPE)工具精確估計 Virtex?-5 器件的功耗所需的步驟。我們還通過在 ML550 開發板 - 進行詳細的功耗測量的首選平臺 - 上進行測量演示了 Virtex?-5 器件的低功耗特性。

2018-06-06 02:45:00 3952

3952

估計得到為20w左右,有點過高了,功耗過高則會造成發熱量增大,溫度高最常見的問題就是系統重啟,另外對FPGA內部的時序也不利,導致可靠性下降。其它硬件電路的功耗是固定的,只有FPGA的功耗有優化的余地,因此硬件團隊則極力要求筆者所在的FPGA團隊盡量多做些低功

2018-09-07 14:58:01 790

790 Vivado不僅是xlinx公司的FPGA設計工具,用它還可以學習Verilog描述,你造嗎?

2018-09-20 09:29:22 10534

10534 我們以8-bit 的LFSR(線性反饋移位寄存器)做一個流水燈為例,介紹Vivado的基本使用。

2018-09-25 16:16:36 16307

16307

時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習Vivado軟件時序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 7943

7943

單片機是基于FLASH結構的,所以單片機上電直接從本地FLASH中運行。但SRAM 架構的FPGA是基于SRAM結構的,掉電數據就沒了,所以需要借助外部電路來配置運行的數據,其實我們可以借助Vivado來學習FPGA的各種配置模式。

2018-11-05 15:12:57 8477

8477 物理優化是Vivado實現流程中更快時序收斂的重要組成部分。

了解如何在Vivado中應用此功能以交換運行時以獲得更好的設計性能。

2018-11-23 06:06:00 4543

4543 基于FPGA芯片Stratix II EP2S60F672C4設計實現了數字基帶預失真系統中的環路延遲估計模塊。該模塊運用了一種環路延遲估計新方法,易于FPGA實現。同時,在信號失真的情況下也能給

2018-12-19 11:04:26 2192

2192

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:06:00 2845

2845

本文檔的主要內容詳細介紹的是Vivado的安裝生成bit文件及燒錄FPGA的簡要流程教程免費下載。

2019-06-18 08:00:00 25

25 Tcl介紹 Vivado是Xilinx最新的FPGA設計工具,支持7系列以后的FPGA及Zynq 7000的開發。與之前的ISE設計套件相比,Vivado可以說是全新設計的。無論從界面、設置、算法

2020-11-17 17:32:26 3306

3306 ? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 功耗是各大設計不可繞過的話題,在各大設計中,我們應當追求低功耗。為增進大家對低功耗的認識,本文將對FPGA低功耗設計予以介紹。如果你對FPGA低功耗相關內容具有興趣,不妨繼續往下閱讀哦。 FPGA

2020-10-28 15:02:13 3673

3673 功耗是我們關注的設計焦點之一,優秀的器件設計往往具備低功耗特點。在前兩篇文章中,小編對基于Freez技術的低功耗設計以及FPGA低功耗設計有所介紹。為增進大家對低功耗的了解,以及方便大家更好的實現低功耗設計,本文將對FPGA具備的功耗加以詳細闡述。如果你對低功耗具有興趣,不妨繼續往下閱讀哦。

2021-02-14 17:50:00 7165

7165 按鍵是FPGA設計當中最常用也是最簡單的外設,本章通過按鍵檢測實驗,檢測開發板的按鍵功能是否正常,并了解硬件描述語言和FPGA的具體關系,學習Vivado RTL ANALYSIS的使用。

2021-01-25 08:27:38 5

5 基于粒子群優化的電力系統狀態向量估計

2021-06-19 14:35:00 8

8 賽靈思近日宣布推出 Vivado ML 版,這是業內首個基于機器學習(ML )優化算法以及先進的面向團隊協作的設計流程打造的 FPGA EDA 工具套件,可以顯著節省設計時間與成本,與目前

2021-07-02 16:40:13 3410

3410

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 27

27 筆者經歷過一個項目,整個系統的功耗達到了100w,而單片FPGA的功耗估計得到為20w左右,有點過高了,功耗過高則會造成發熱量增大,溫度高最常見的問題就是系統重啟,另外對FPGA內部的時序也不利,導致可靠性下降。

2022-09-19 16:13:21 2205

2205 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-19 16:20:51 2298

2298 XKF3 - 使用慣性和磁感應的 3D 方向的低功耗優化估計

2022-11-14 21:08:29 1

1 對于FPGA來說,設計人員可以充分利用其可編程能力以及相關的工具來準確估算功耗,然后再通過優化技術來使FPGA和相應的硬件設計滿足其功耗方面的要求。

2022-12-29 14:46:14 2379

2379 系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。本次帶來Vivado系列,Vivado開發軟件開發設計流程。話不多說,上貨。

2023-02-21 09:16:44 5063

5063 有一天使用Vivado調用questasim(modelsim估計也一樣),仿真報錯

2023-05-08 17:12:56 5357

5357 本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 6174

6174

點擊上方 藍字 關注我們 ? FPGA 高級設計之實現功耗優化 與ASICs(Application Specific Integrated Circuits)比較,相似的邏輯功能,用FPGA來實現

2023-05-19 13:50:02 2284

2284 電子發燒友網站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費下載

2023-06-15 09:14:49 0

0 FPGA開發過程中,vivado和quartus等開發軟件都會提供時序報告,以方便開發者判斷自己的工程時序是否滿足時序要求。

2023-06-26 15:29:05 2343

2343

電子發燒友網站提供《Vivado設計套件用戶指南之功耗分析和優化.pdf》資料免費下載

2023-09-14 10:25:07 2

2 電子發燒友網站提供《Vivado ML版中基于ML的路由擁塞和延遲估計.pdf》資料免費下載

2023-09-14 11:41:08 0

0 電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 優化FPGA(現場可編程門陣列)設計的性能是一個復雜而多維的任務,涉及多個方面和步驟。以下是一些關鍵的優化策略: 一、明確性能指標 確定需求 :首先,需要明確FPGA設計的性能指標,包括時鐘頻率

2024-10-25 09:23:38 1454

1454 設計、編譯、交付,輕松搞定。更快更高效。 Vivado 設計套件提供經過優化的設計流程,讓傳統 FPGA 開發人員能夠加快完成 Versal 自適應 SoC 設計。 面向硬件開發人員的精簡設計流程

2025-05-07 15:15:09 1172

1172

利用vivado進行設計xilinx FPGA時,寫完設計代碼和仿真代碼后,點擊run simulation(啟動modelsim進行仿真)。

2025-08-30 14:22:17 1157

1157

電子發燒友App

電子發燒友App

評論