vivado提供了DDS IP核可以輸出正余弦波形,配置方法如下

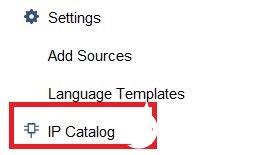

打開VIVADO,選擇IP Catalog

輸入DDS,找到DDS IP核,雙擊打開

打開IP核配置,parameter Selection選擇System Parameters

設置System Parameters參數:

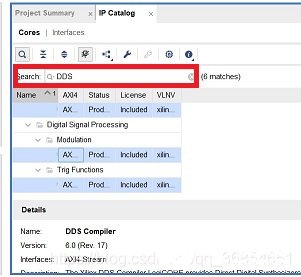

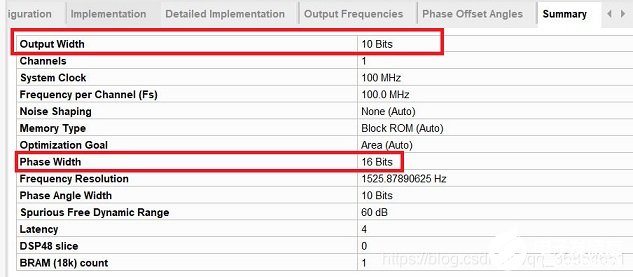

Spurious Free Dynamic Range的設置,這個參數與輸出數據的寬度相關。

我需要位寬為10位的輸出,因此Spurious Free Dynamic Range設置為10*6=60

Frequency Resolution的設置,這個參數與輸出相位數據的寬度相關,如果想要得到16bit的寬度,channels為1,系統輸入時鐘為100MHz

Frequency Resolution = 100000000/2^16 = 1525.8789025

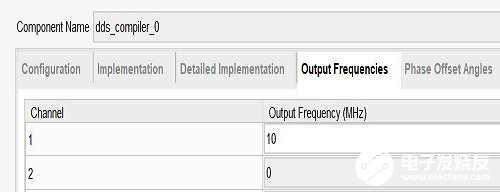

設置如圖:

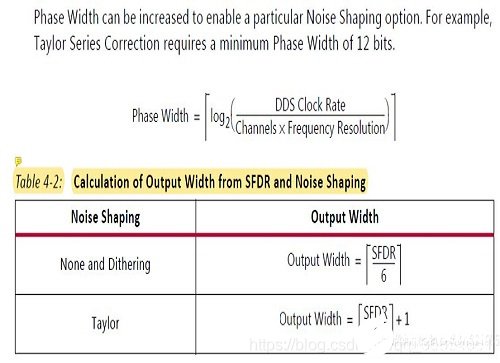

設置Phase Increment Programmability和Phase offset programmability為固定模式,輸出為正弦波

設置輸出頻率10M

查看配置好的DDS參數

頂層程序

`timescale 1ns / 1ps module top( input clk_100m, input rst_n, ///DAC0/ output [9:0]DAC0_D, output DAC0_CLK, output DAC0_PD ); wire [15:0]dac_data; wire phase_tvalid; wire [15:0]phase_data; wire dds_valid; dac dac_ini( .clk_100m(clk_100m), .dac_data(dac_data), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); dds_compiler_0 dds_compiler_0_ini( .aclk(clk_100m), .m_axis_data_tvalid(dds_valid), .m_axis_phase_tvalid(phase_tvalid), .m_axis_phase_tdata(phase_tdata), .m_axis_data_tdata(dac_data) ); endmodule

testbench

`timescale 1ns / 1ps module top_tb( ); reg clk_100m; reg rst_n; wire [9:0]DAC0_D; wire DAC0_CLK; wire DAC0_PD; initial begin clk_100m = 1‘b0; rst_n = 1’b1; #10 rst_n = 1‘b0; #500 rst_n = 1’b1; end always #5 clk_100m = ~clk_100m; top top_ini( .clk_100m(clk_100m), .rst_n(rst_n), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); endmodule

testbench

`timescale 1ns / 1ps module top_tb( ); reg clk_100m; reg rst_n; wire [9:0]DAC0_D; wire DAC0_CLK; wire DAC0_PD; initial begin clk_100m = 1‘b0; rst_n = 1’b1; #10 rst_n = 1‘b0; #500 rst_n = 1’b1; end always #5 clk_100m = ~clk_100m; top top_ini( .clk_100m(clk_100m), .rst_n(rst_n), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); endmodule

仿真時注意DDSIP核輸出的是有符號數,因此需要將DDS輸出的數據設置成有符號數,即將仿真數據radix為signed decimal

注意:因為DDSIP核輸出的是有符號數,因此雖然我們設置的是10位的位寬,但輸出數據共有16位,因為需要高位來作補碼。在使用時只用低10位即可。

編輯:lyn

-

DDS

+關注

關注

22文章

684瀏覽量

156596 -

IP核

+關注

關注

4文章

344瀏覽量

51950 -

Vivado

+關注

關注

19文章

857瀏覽量

71114

發布評論請先 登錄

驅動板PCB布線的注意事項

Vivado浮點數IP核的握手信號

別讓這些細節毀了PCBA!焊接注意事項清單

美國Odyssey奧德賽電池充電注意事項全解析

IGBT器件的防靜電注意事項

SiC MOSFET驅動電路設計注意事項

淺析Vivado的IP核DDS使用方式及注意事項

淺析Vivado的IP核DDS使用方式及注意事項

評論