這篇文章在開發者分享|AMD Vitis HLS 系列 1 - AMD Vivado IP 流程(Vitis 傳統 IDE) 的基礎上撰寫,但使用的是 AMD Vitis Unified IDE,而不是之前傳統版本的 Vitis HLS。

2025-06-20 10:06:15 2068

2068

Vivado IP 流程(Vitis Unified),在這篇 AMD Vitis HLS 系列 3 中,我們將介紹如何使用 Unified IDE 創建 HLS 組件。這里采用“自下而上”的流程,從 HLS

2025-07-02 10:55:32 1263

1263

在本篇文章我們將學習如何在 AMD Vitis Unified 2024.2 中連接到 QEMU。 這是本系列的第 2 篇博文。要了解如何設置和使用 QEMU + 協同仿真,請參閱開發者分享|在 AMD Versal 自適應 SoC 上使用簡單的 QEMU + 協同仿真示例。

2025-08-06 17:24:19 1643

1643

您將在這篇博客中了解系統設備樹 (SDT) 以及如何在 AMD Vitis Unified IDE 中使用 SDT 維護來自 XSA 的硬件元數據。本文還講述了如何對 SDT 進行操作,以便在 Vitis Unified IDE 中實現更靈活的使用場景。

2025-11-18 11:13:53 2961

2961

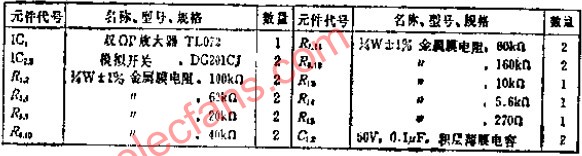

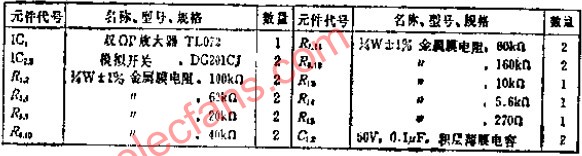

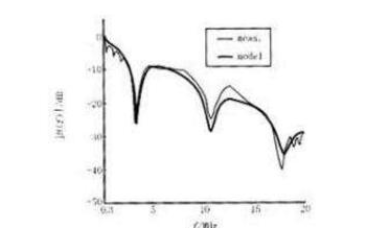

可由數字設定截止頻率的可編程低通濾波器

電路的功能

2010-05-13 15:19:50 3279

3279

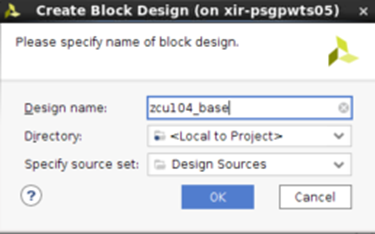

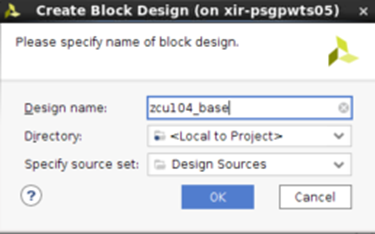

裝加速平臺 ;第 4 部分: 在 Vitis 中測試定制加速平臺 )。 在本文中,我們將講解如何在 Vivado Design Suite 中完成平臺準備工作,以便將其用作為 Vitis 中的加速平臺

2020-09-26 11:29:43 4310

4310

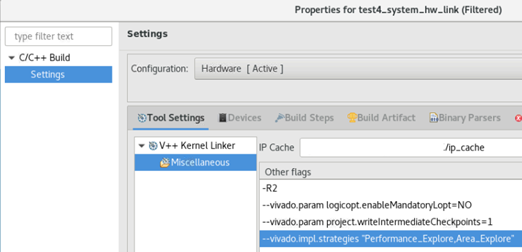

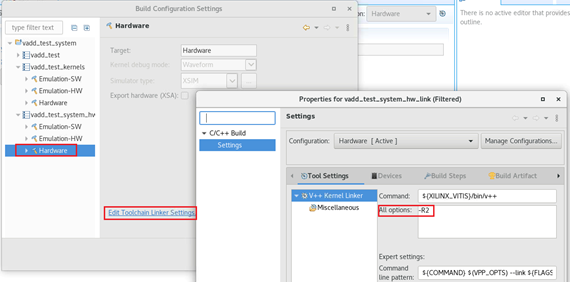

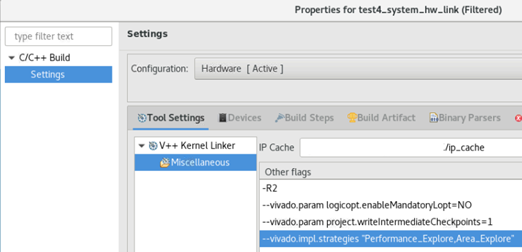

在Vitis完成這個過程的底層,實際調用的是Vivado。Vitis會指定默認的Vivado策略來執行綜合和實現的步驟。當默認的Vivado策略無法達到預期的時序要求時,我們需要在Vivado中分

2022-08-02 08:03:38 1821

1821

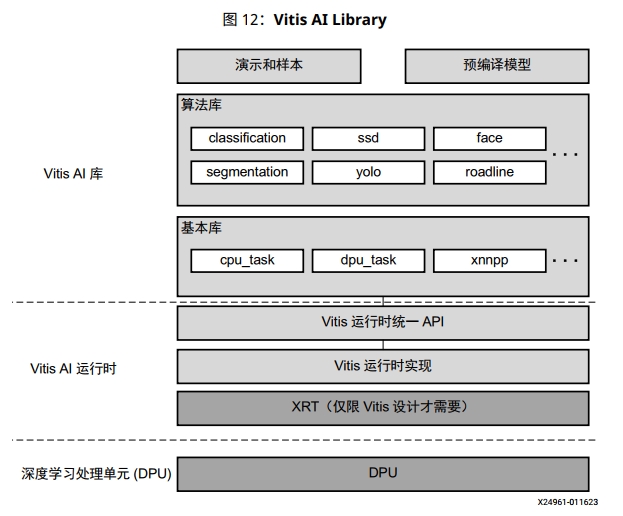

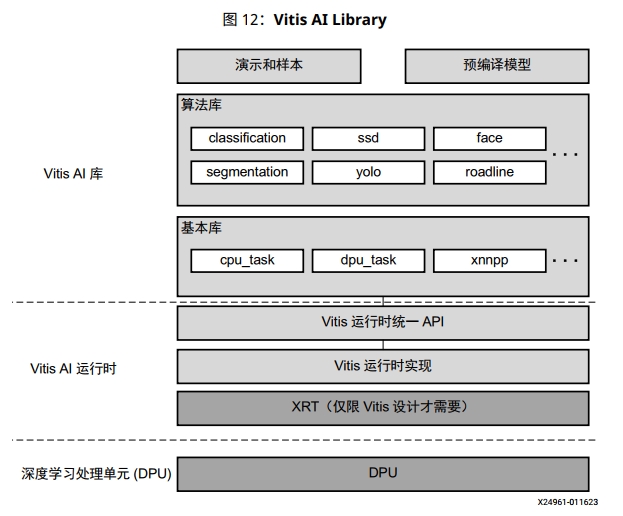

Vitis AI Library是一組高層次庫和 API,專為利用 DPU 高效執行 AI 推斷而構建。它是基于 Vitis AI運行時利用 Vitis運行時統一 API 來構建的,能夠為 XRT 提供完整支持。

2023-10-17 08:23:20 1831

1831

Vitis AI Model Zone軟件平臺具備哪些功能?Vitis AI Model Zone軟件平臺的應用范圍包括哪些?

2021-07-09 06:44:28

Vitis 已經更新到2023.2了,新版本相較于舊版本更新了嵌入式平臺,新版平臺增加了Versal? AI 引擎 DSP 設計的增強功能,全新的獨立 Vitis 嵌入式軟件,最新 Vitis 統一

2024-03-24 16:15:14

上一章聊了一下vitis2023.2怎樣使用classic Vitis IDE,這章我們來說一說基于classic Vitis

IDE的工程怎么樣更新到新版本的Vitis Unified IDE

2024-03-24 17:14:43

Vitis準備工程及注意事項

2021-01-25 06:26:20

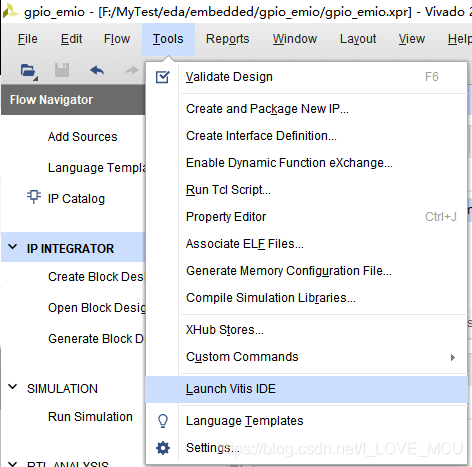

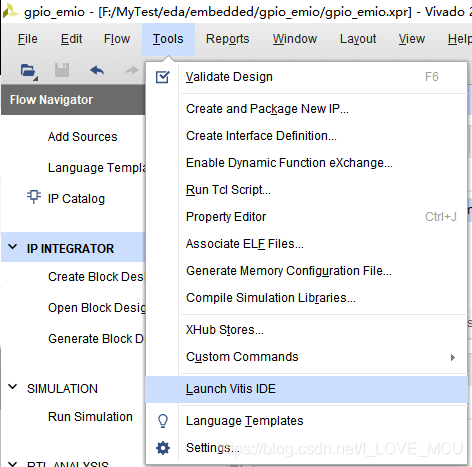

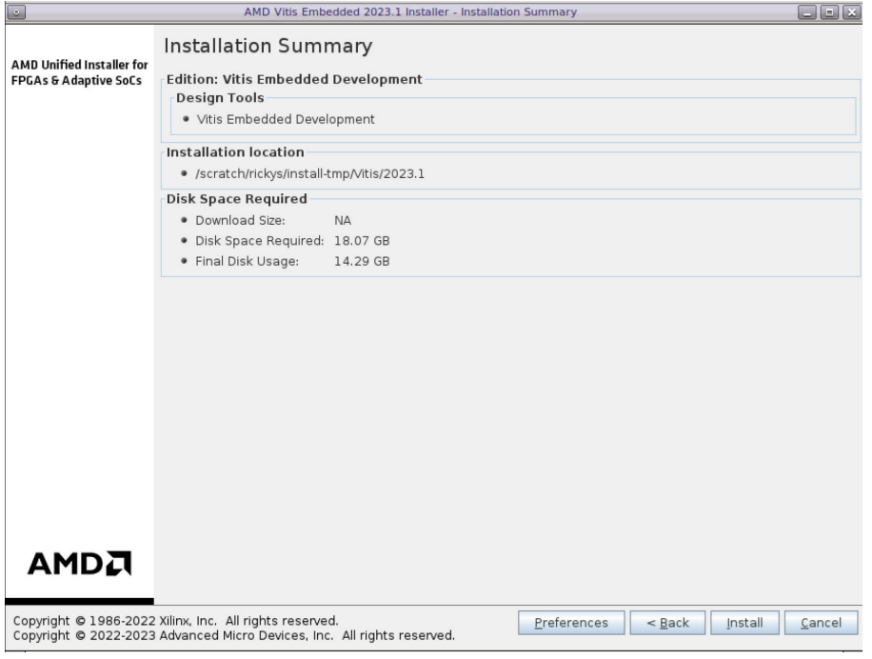

找到vitisvivado->tools->launch vitis ide如果打開失敗,說明沒有安裝vitis,先進行安裝安裝vitisvivado->help->Add

2020-12-23 17:10:37

在學習ZYNQ嵌入式開發的過程中,正點原子的教程是采用SDK,而我下載的vivado2020.1已經變成了vitis,所以寫一這篇博客,方便后續查閱。

2021-02-04 07:09:50

RTC介紹中斷介紹Vitis程序編寫

2021-02-25 07:39:08

vitis和vivado有什么區別和聯系呢

2023-10-16 07:55:35

,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI

2022-09-07 15:21:54

求助各位高手:如何在OrCAD 16.3中, 設定Wire的寬度和顏色?而不是Line的顏色和寬度.

2012-07-20 20:32:08

指針地址調用entry函數,但asm文件指向重啟函數。需求:請簡要說明如何在移植的main.c中初始化kernel和系統

2020-11-19 12:03:44

linux kernel通過修改鏈接腳本lds文件實現,請問如何在esp32的linker.lf文件中實現?

linux kernel實現過程:

鏈接腳本:

. = ALIGN(4

2024-06-26 06:19:15

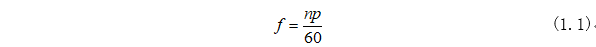

:在CentOS 7 和CentOS 8中的操作方式有些差異,需要在配置前注意系統版本,此處以CentOS-7.9為例進行說明。

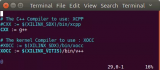

1. 系統軟件安裝

Vitis需要一些軟件或者依賴庫,優先解決該

2023-08-27 21:22:34

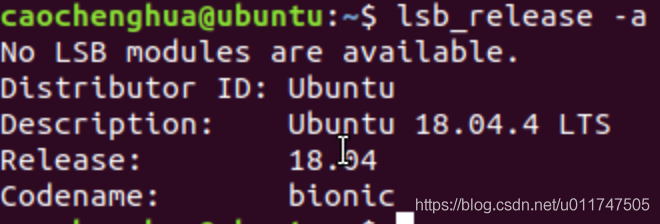

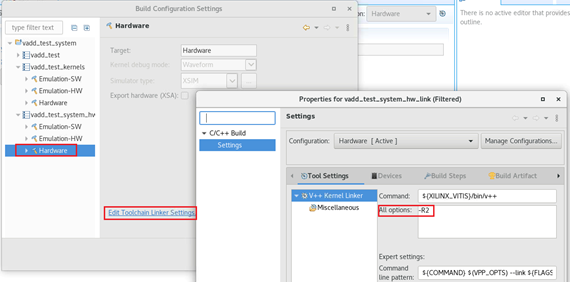

一、基礎環境

硬件:KV260視覺入門套件

攝像頭:海康720P USB攝像頭(因為部署Vitis AI之后懶得poweroff插MIPI camera了,直接USB上)

軟件:Ubuntu

2023-09-10 13:15:24

量化

七、Vitis AI 通過遷移學習訓練自定義模型

八、Vitis AI 將自定義模型編譯并部署到KV260中

鋪墊

Vitis AI 是什么?

Vitis AI 是賽靈思公司推出的一款綜合 AI

2023-10-14 15:34:26

本文將介紹如何使用Vitis-AI加速YOLOX模型實現視頻中的目標檢測,并對相關源碼進行解讀。由于演示的示例程序源碼是Vitis-AI開源項目提供的,本文演示之前會介紹所需要的準備工作。演示之后

2023-10-06 23:32:47

都已編譯到預構建的 Vitis AI 開發板鏡像中。您可直接運行示例。如有新程序,請在主機側對其進行編譯并將可執行程序復制到目標。

1. 使用 scp 命令將

2023-09-26 16:22:43

%BD-Vitis-AI-Library

從步驟3下載

vitis-ai-runtime-3.0.0.tar.gz

安裝位置為/usr/lib 和 /usr/include

這里面包含了所有需要的庫。在/usr/bin中還有

2023-08-27 23:35:48

本文首先將會對Vitis統一軟件平臺和Vitsi AI進行簡單介紹,然后介紹如何在KV260上部署DPU鏡像,最后在KV260 DPU鏡像上運行Vitis AI自帶的圖像分類示例。通過本文,你將會

2023-09-10 23:01:02

1、使用Vitis HLS創建屬于自己的IP高層次綜合(High-level Synthesis)簡稱HLS,指的是將高層次語言描述的邏輯結構,自動轉換成低抽象級語言描述的電路模型的過程。對于AMD

2022-09-09 16:45:27

。3.Vitsi 開始調試在 Vivado 2019.2 中啟動 Vitis 的方式 與我現在用的 vivado 2017.4 有些不一樣,當然這一點也不清楚是在 2019.2 版本中做的改變還是在2018版本

2020-03-06 22:59:12

里面U-BOOT的版本為“u-boot-2013.01.01-psp06.00.00.00”,看U-BOOT里面設定MPU和DDR的頻率的時候,有幾點疑問:

1. 在clock.c的文件中(路徑

2018-06-21 05:06:58

如何在VMware中安裝ubuntu 16.04如何安裝Vitis AI幾個常見的docker指令

2021-02-24 06:24:00

我嘗試將RTT移植到Vitis2019.2工程中,硬件平臺為Zynq Ultrascale+ MPSoC ZU3EG 的自制板子。我已經移植了RTT源碼/bsp/zynqmp-r5-axu4ev

2022-09-15 14:11:28

Vivado硬件平臺更新后Vitis工程如何快捷更新

2021-03-08 08:00:55

如何在編程過程中修改NuMicro?系列芯片的外部晶體(H XT)的設定值?

2020-11-27 06:00:02

實時操作系統T-Kernel的源代碼已在T-Engine Forum開放,它在嵌入式系統中的應用也逐漸增多。本文檔總結了在新硬件中實施T-Kernel時必須探討的事項以及實施要點等,目的是使那些對RTOS并不

2011-04-05 23:22:48 15

15 如何在PCB下設定不同的鋪銅區域安全間距及切銅,有借鑒意義。

2016-12-16 21:54:48 0

0 在這個簡短的視頻中,您將學習如何在OpenCL 2.0中實現Sierpinski Carpet Kernel。

2018-11-07 06:20:00 3907

3907 Kernel 一般來說適用于任何機器學習算法,你可能會問為什么

2019-06-19 09:54:30 4379

4379 Vitis 2019.2 使用 gcc 編譯 C 語言源代碼,使用 Vivado HLS 編譯與 SDAccel 流匹配的加速內核。此外,Vitis 也使用與 SDAccel 相同的目標平臺和賽靈思

2020-06-28 10:05:51 2658

2658

在實際使用中不少用戶只是按照變頻器制造單位原有的設定值,并沒有根據現場的實際情況進行調整,因而造成因載波頻率值選擇不當,而影響正確,感覺的有效工作狀態,因此在變頻器使用過程中如何來正確選擇變頻器的載波頻率值亦是重要的事。本文就此提供應該從以下諸方面來考慮,并正確選擇載波頻率值的依據。

2020-07-26 11:47:32 11323

11323

在本教程中,我們將來聊一聊有關如何在 Vitis HLS 中使用 AXI4-Lite 接口創建定制 IP 的基礎知識。

2020-09-13 10:04:19 7395

7395

Linux嵌入式設計中最基本的任務之一是創建用戶應用程序。 在本篇博文中,我們將探討如何在 Vitis 中使用 UIO 驅動框架創建簡單的 Linux 用戶應用。 1 硬件設計 本次

2020-11-20 14:05:34 5335

5335 Vitis迎來了版本更新,Vitis 2020.2 帶來更加快捷智能的使用體驗。首次引入Vitis?AI Engine( AI引擎)編譯器,并提供多個加速功能。

2020-12-09 09:10:25 1782

1782 這是《創建 Vitis 加速平臺》系列的第 3 篇博文。在前文中,我們講解了如何創建硬件和軟件工程。在本文中,我們將講解如何在 Vitis 中將所有這些工程封裝在一起。 在 Vitis 中加速軟件

2020-12-26 10:20:54 3443

3443

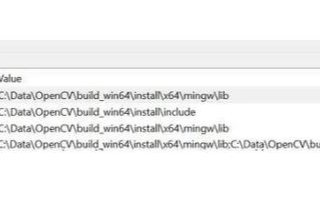

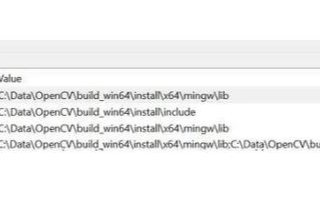

高層次綜合工具中調用視覺庫遇到的大多數問題都和 opencv 庫以及Xilinx Vision 庫的安裝路徑有關,如今 Vitis HLS 2020.1 之后的版本都不再提供OpenCV 的預編譯庫

2020-12-29 11:12:19 4272

4272

賽靈思公司(Xilinx)推出Vitis——這是一款統一軟件平臺,可以讓包括軟件工程師和AI科學家在內的廣大開發者都能受益于硬件靈活應變的優勢。歷經5年、投入總計1000人打造而成,Vitis統一軟件平臺無需用戶深入掌握硬件專業知識,即可根據軟件或算法代碼自動適配和使用賽靈思硬件架構。

2022-07-25 18:07:14 18858

18858

在學習ZYNQ嵌入式開發的過程中,正點原子的教程是采用SDK,而我下載的vivado2020.1已經變成了vitis,所以寫一這篇博客,方便后續查閱。

2022-07-25 18:03:30 6190

6190

第一個Xilinx Vitis IDE入門helloworld程序

2022-07-25 17:37:23 1775

1775

在論壇上遇到在高層次綜合工具中調用視覺庫遇到的大多數問題都和 opencv 庫以及Xilinx Vision 庫的安裝路徑有關,如今 Vitis HLS 2020.1 之后的版本都不再提供

2021-01-27 06:17:45 6

6 賽靈思公司(Xilinx)推出Vitis——這是一款統一軟件平臺,可以讓包括軟件工程師和AI科學家在內的廣大開發者都能受益于硬件靈活應變的優勢。歷經5年、投入總計1000人打造而成,Vitis統一軟件平臺無需用戶深入掌握硬件專業知識,即可根據軟件或算法代碼自動適配和使用賽靈思硬件架構。

2021-01-31 07:49:37 16

16 在學習ZYNQ嵌入式開發的過程中,正點原子的教程是采用SDK,而我下載的vivado2020.1已經變成了vitis,所以寫一這篇博客,方便后續查閱。

2021-02-21 06:48:51 20

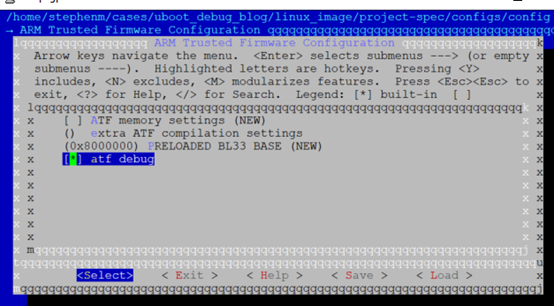

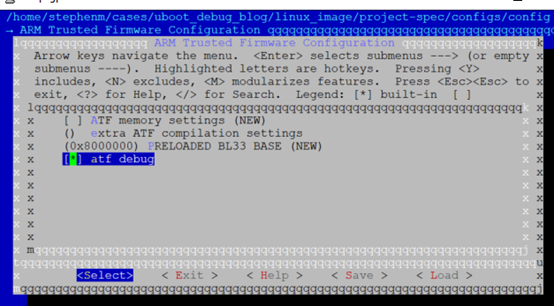

20 在本篇博文中,我們將探討如何在 Vitis 中調試 Zynq UltraScale 器件啟動鏡像。這些啟動鏡像包括 ARM 可信固件 (ATF) 和 U-boot。 本篇博文乃是系列博文中的一篇,此

2021-06-01 15:35:45 4265

4265

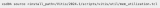

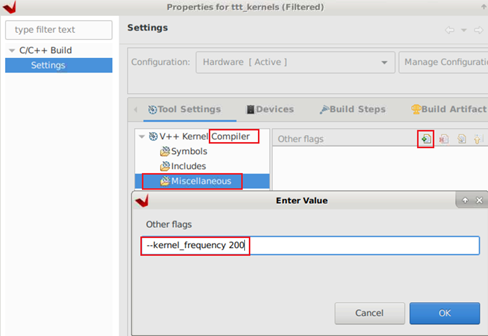

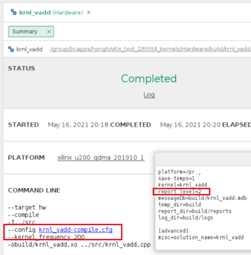

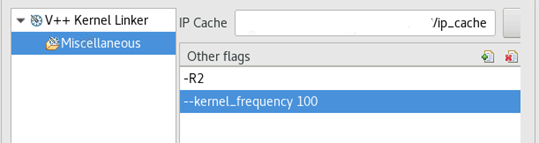

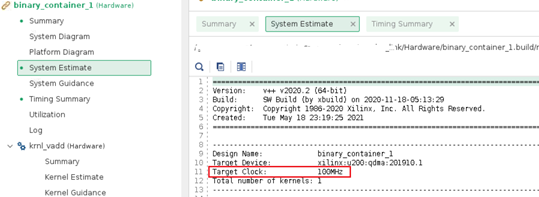

在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel時,系統會自動為Kernel的時鐘設置默認頻率。 以 xilinx_u200_qdma_201910_1 平臺為例,在

2021-06-12 14:19:00 37580

37580 本文來自賽靈思高級產品應用工程師 Hong Han Alveo系列開發板上的平臺其實是一個DFX設計的靜態部分,在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel, 最終這些

2021-06-18 10:15:14 37454

37454 在Vitis 統一軟件平臺中使用v++ -link命令,可以把各種類型Kernel(C, C++, OpenCL C, 以及 RTL)的對象文件(.XO)整合到目標平臺中,最終生成器件的二進制文件

2021-07-28 10:12:47 2858

2858

當 U-Boot 將設備樹加載到內存指定位置后,ARM 內核的 SoC 以通用寄存器 r2 來傳遞 dtb 在內存中的地址。kernel 獲取到該地址后對 dtb 文件做進一步的處理。 設備樹的傳遞

2021-07-29 11:19:45 3042

3042

Q1 HLS導出的.xo文件如何導入到Vitis里面?需要把.xo文件解壓,然后把文件夾導入到Vitis Kernel/src文件夾下嗎? 這下圖中,將xo文件作為源文件import時,xo文件顯示

2021-08-26 17:03:52 3410

3410 Vitis Vision庫是OpenCV和Vision功能的加速庫,可在Vitis環境中使用,這些庫的L1目錄是示例設計。為了適應各種用戶環境,從2020.1版本開始,Xilinx不再

2022-02-16 16:21:38 3239

3239

對Kernel進行性能分析需要對其進行仿真,同時還要用到Vitis Analyzer。為便于說明,我們以一個簡單的Vitis工程為例。這個工程中有兩個kernel,相應的代碼如下圖所示

2022-03-15 15:30:23 2503

2503 Vitis HLS 是一種高層次綜合工具,支持將 C、C++ 和 OpenCL 函數硬連線到器件邏輯互連結構和 RAM/DSP 塊上。Vitis HLS 可在Vitis 應用加速開發流程中實現硬件

2022-05-25 09:43:36 3450

3450 生成的 device tree 里 axigpio core 的 driver 是 xilinx driver,我們需要把它替換為我們生成的 kernel module 的 drivername

2022-06-30 09:48:49 1144

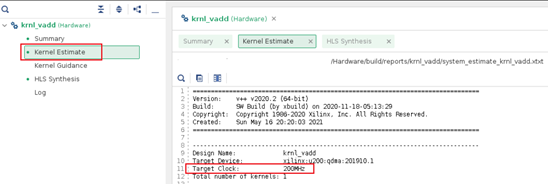

1144 在Kernel Estimate報告中,可以看到,Target Clock已經按要求設置成200Mhz. 說明 Vitis_HLS是按照200Mhz的要求來綜合Kernel的代碼的.

2022-07-01 09:52:53 37149

37149 您是否想創建自己帶有 AXI4-Lite 接口的 IP 卻感覺無從著手?本文將為您講解有關如何在 Vitis HLS 中使用 C 語言代碼創建 AXI4-Lite 接口的基礎知識。

2022-07-08 09:40:43 2808

2808 HLS導出的.xo文件如何導入到Vitis里面?需要把.xo文件解壓,然后把文件夾導入到Vitis Kernel/src文件夾下嗎?

2022-08-03 11:20:26 3933

3933

本篇博文將繼續介紹在Vitis中把Settings信息傳遞到底層的Vivado。

2022-08-02 10:26:41 1517

1517

Alveo系列開發板上的平臺其實是一個DFX設計的靜態部分,在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel, 最終這些Kernel的邏輯會在分布在DFX設計的動態區域。

2022-08-02 09:38:37 37376

37376

在本篇博文中,我們將探討如何在 Vitis 中調試 Zynq UltraScale 器件啟動鏡像。這些啟動鏡像包括 ARM 可信固件 (ATF) 和 U-boot。

2022-08-02 10:14:59 5052

5052

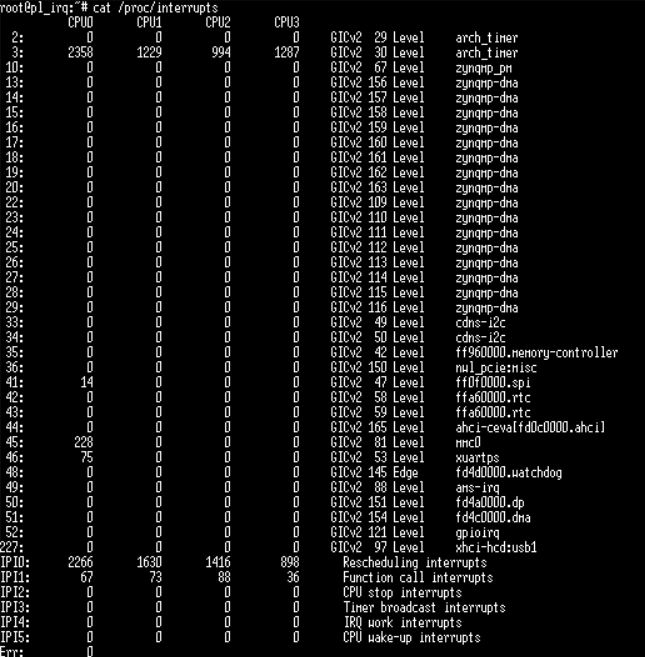

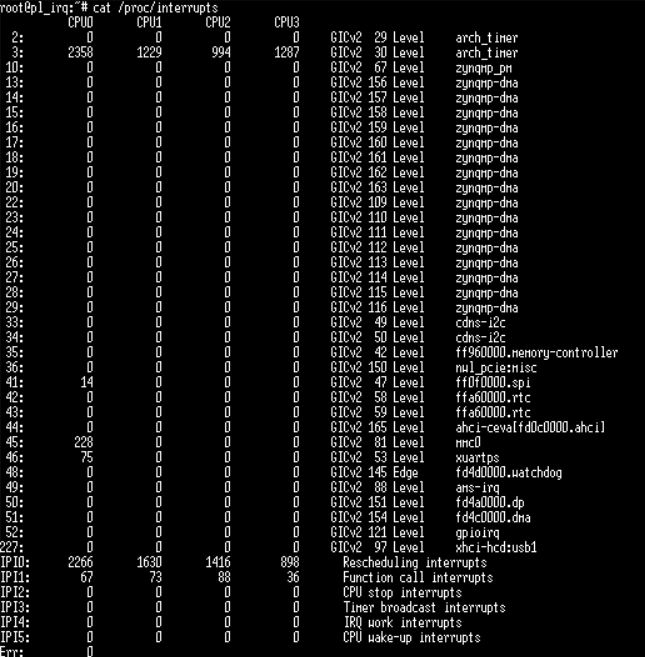

有時我們需要為官方 IP 或者自己創建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 來控制這個 IP。如果要使用 IP 中斷,我們需要在 kernel module 代碼里獲取設備中斷并建立中斷服務程序。

2022-08-02 11:35:23 963

963

在 AXI 基礎第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學習如何導出 IP

2022-08-02 09:43:05 1247

1247

Vitis HLS 工具能夠將 C++ 和 OpenCL 功能部署到器件的邏輯結構和 RAM/DSP 塊上。在 GitHub 上提供 Vitis HLS 前端為研究人員、開發人員和編譯器愛好者開啟了無限可能的新世界,使他們可以利用 Vitis HLS 技術并根據其應用的特定需求進行修改。

2022-08-03 09:53:58 1602

1602 對于AMD Xilinx而言,Vivado 2019.1之前(包括),HLS工具叫Vivado HLS,之后為了統一將HLS集成到Vitis里了,集成之后增加了一些功能,同時將這部分開源出來了。Vitis HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。

2022-09-02 09:06:23 4612

4612 電源技巧:如何在隔離式電源中測量頻率響應

2022-11-04 09:51:39 0

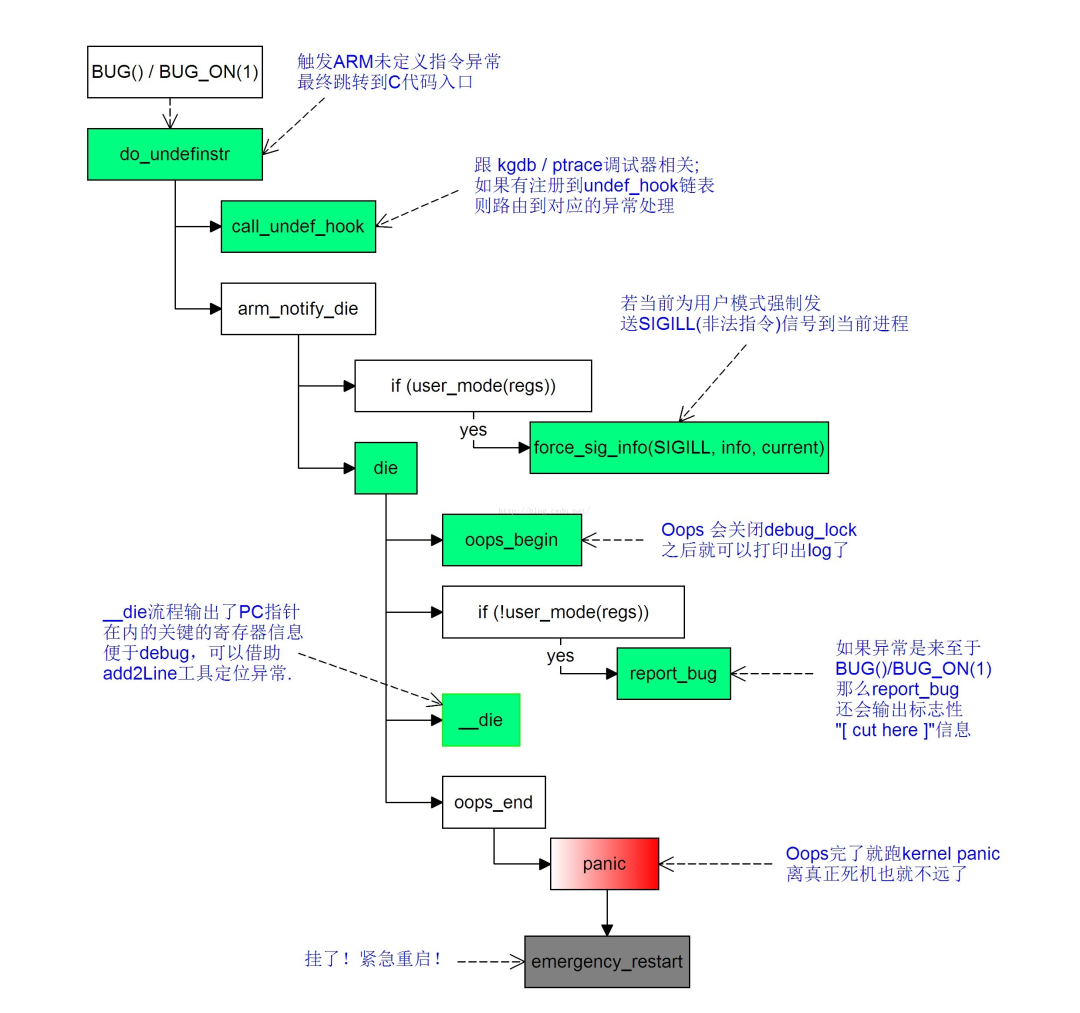

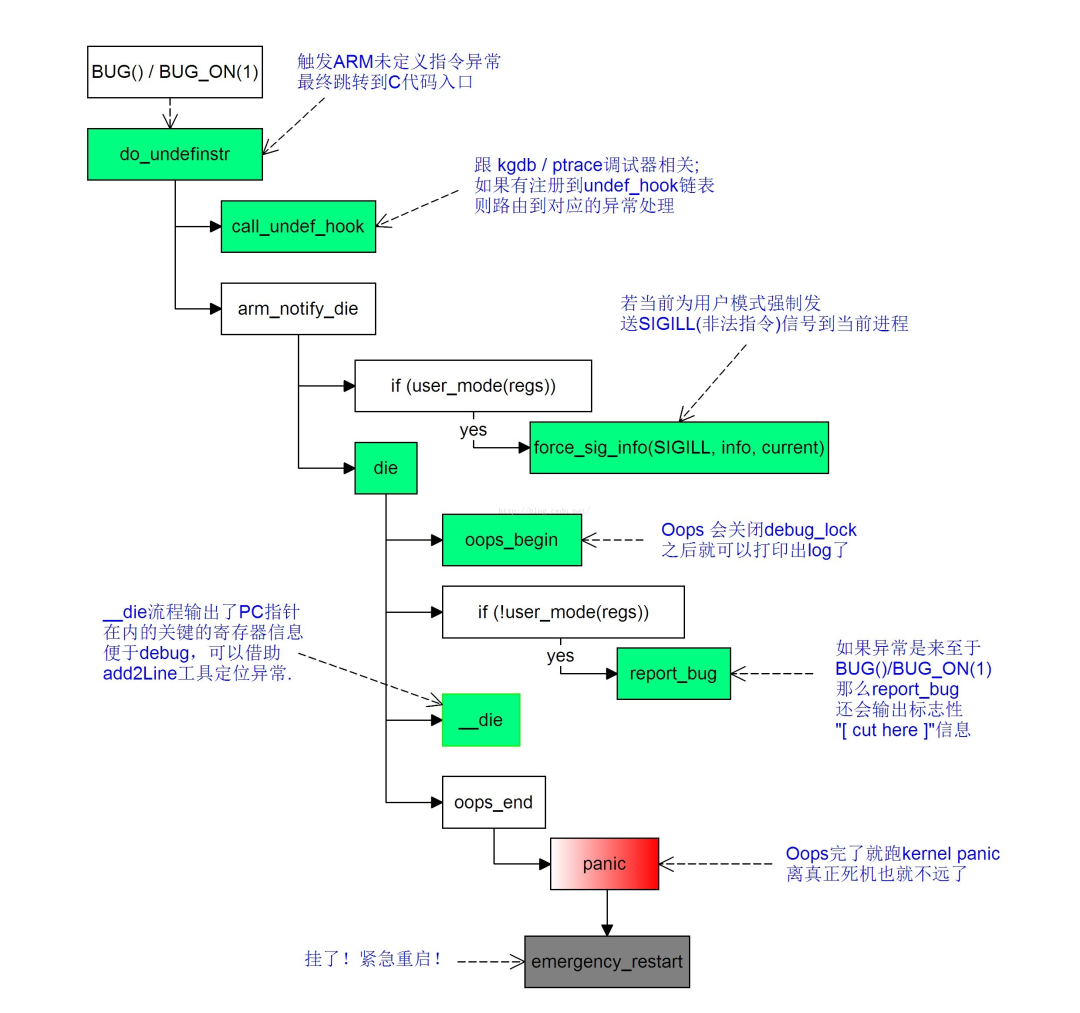

0 我們在項目開發過程中,很多時候會出現由于某種原因經常會導致手機系統死機重啟的情況(重啟分Android重啟跟kernel重啟,而我們這里只討論kernel重啟也就是 kernel panic 的情況

2023-01-19 16:14:00 1931

1931

電機控制中載波頻率是非常重要的因素,其值不能設定太高,同樣也不能設定太低,通常載波頻率設定與五個因素有關:基波頻率、硬件限制、諧波電流、內部軟件的實現、功率模塊溫升,這期主要講講與這幾個因素有關的原因。

2023-01-13 14:58:50 16584

16584

AMD Vitis HLS 工具允許用戶通過將 C/C++ 函數綜合成 RTL,輕松創建復雜的 FPGA 算法。Vitis HLS 工具與 Vivado Design Suite(用于綜合、布置和布線)及 Vitis 統一軟件平臺(用于所有異構系統設計和應用)高度集成。

2023-04-23 10:41:01 1730

1730

在本快速入門演示中,將探討如何在 Vitis 中使用 Git 集成以及如何使用團隊操作來共享 Vitis 工程。

2023-05-12 15:01:00 1889

1889

本文演示了在Vitis? 中對 Linux 應用程序開發的過程中如何使用外部庫

2023-07-07 14:14:51 1792

1792

Vitis? HLS 2023.1 支持新的 L1 庫向導,本文將講解如何下載 L1 庫、查看所有可用功能以及如何在 Vitis HLS GUI 中使用庫函數。

2023-08-16 10:26:16 2123

2123

本文首先將會對Vitis統一軟件平臺和Vitsi AI進行簡單介紹,然后介紹如何在KV260上部署DPU鏡像,最后在KV260 DPU鏡像上運行Vitis AI自帶的圖像分類示例。通過本文,你將會

2023-09-12 10:02:08 3326

3326

電子發燒友網站提供《Vitis AI優化器指南.pdf》資料免費下載

2023-09-14 11:04:38 2

2 電子發燒友網站提供《Vitis Model Composer教程.pdf》資料免費下載

2023-09-14 09:52:29 7

7 檔旨在逐步指導您熟悉各種 Vitis 工具,這些工具采用自下而上的設計流程來開發系統組件,隨后將其集成到頂層系統工程中。 如果您希望獲取完整版用戶指

2023-09-13 08:15:02 1792

1792

電子發燒友網站提供《Vitis AI用戶指南.pdf》資料免費下載

2023-09-13 15:00:21 3

3 電子發燒友網站提供《Vitis HLS移植指南.pdf》資料免費下載

2023-09-13 09:21:12 1

1 本文將介紹如何使用Vitis-AI加速YOLOX模型實現視頻中的目標檢測,并對相關源碼進行解讀。由于演示的示例程序源碼是Vitis-AI開源項目提供的,本文演示之前會介紹所需要的準備工作。演示之后會對關鍵源碼進行解析。

2023-10-16 15:43:25 2612

2612

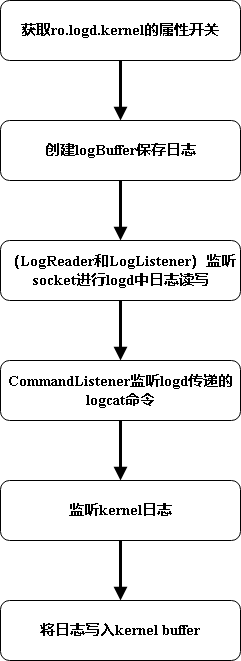

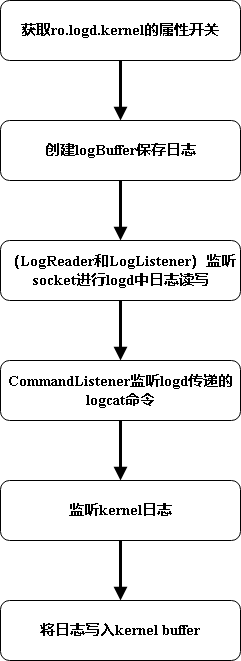

kernel日志寫入logd介紹 通過logcat命令獲取kernel日志比較特殊,故作為一個例子進行梳理。 2.3.1 整體流程 2.3.2 命令打印kernel日志 通過logcat -b

2023-11-23 17:11:17 1435

1435

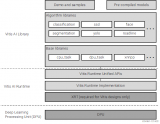

AMD Vitis 軟件平臺是一款開發環境,主要用于開發包括 FPGA 架構、Arm 處理器子系統和 AI 引擎在內的設計。Vitis 工具與 AMD Vivado ML 設計套件相結合,可為

2023-12-20 10:00:02 1414

1414

電子發燒友網站提供《Vitis AI用戶指南.pdf》資料免費下載

2024-01-03 10:51:52 5

5 本篇文章將演示創建一個使用 AMD Vitis? 視覺庫的 Vitis HLS 組件的全過程。此處使用的是 Vitis Unified IDE。如果您使用的是舊版 AMD Vitis Software Platform,大多數步驟相同。

2024-05-08 14:02:52 1743

1743

AMD Vitis? 2023.2 設計工具是 Vitis 設計工具變化較大的一個版本,設計流程和界面都發生了變化。

2024-05-29 09:50:26 1465

1465

,并在 Unified IDE 中仍可使用。本文涵蓋了如何在 Vitis 中使用分析工具在應用程序調試期間對棧和堆進行監控。

2025-10-24 16:54:06 708

708

與電機匹配問題 當電機負載慣性過大或存在機械卡阻時,變頻器可能自動降低輸出頻率以保護系統。例如離心泵負載若葉輪變形,會導致實際運行頻率始終低于設定值5-10Hz。此時需檢查: 1. 機械傳動系統潤滑狀態。 2. 聯軸器對中精度

2026-01-05 07:39:41 26

26

電子發燒友App

電子發燒友App

評論