在本篇文章我們將學習如何在 AMD VitisUnified 2024.2 中連接到 QEMU。 這是本系列的第 2 篇博文。要了解如何設置和使用 QEMU + 協同仿真,請參閱開發者分享|在 AMD Versal 自適應 SoC 上使用簡單的 QEMU + 協同仿真示例。

創建 Vitis 工作空間

本篇文章使用的是 Vitis Unified 2024.2 來生成工作空間。此處使用的 XSA 與上一篇博客使用的相同。本文將創建一個“Empty Application”模板,并導入簡單代碼以測試 AXI GPIO。

您可遵循此處的教程,這些教程有助于您在 Vitis Unified IDE 中使用嵌入式流程:

https://github.com/Xilinx/Vitis-Tutorials/tree/2024.1/Embedded_Software/Getting_Started

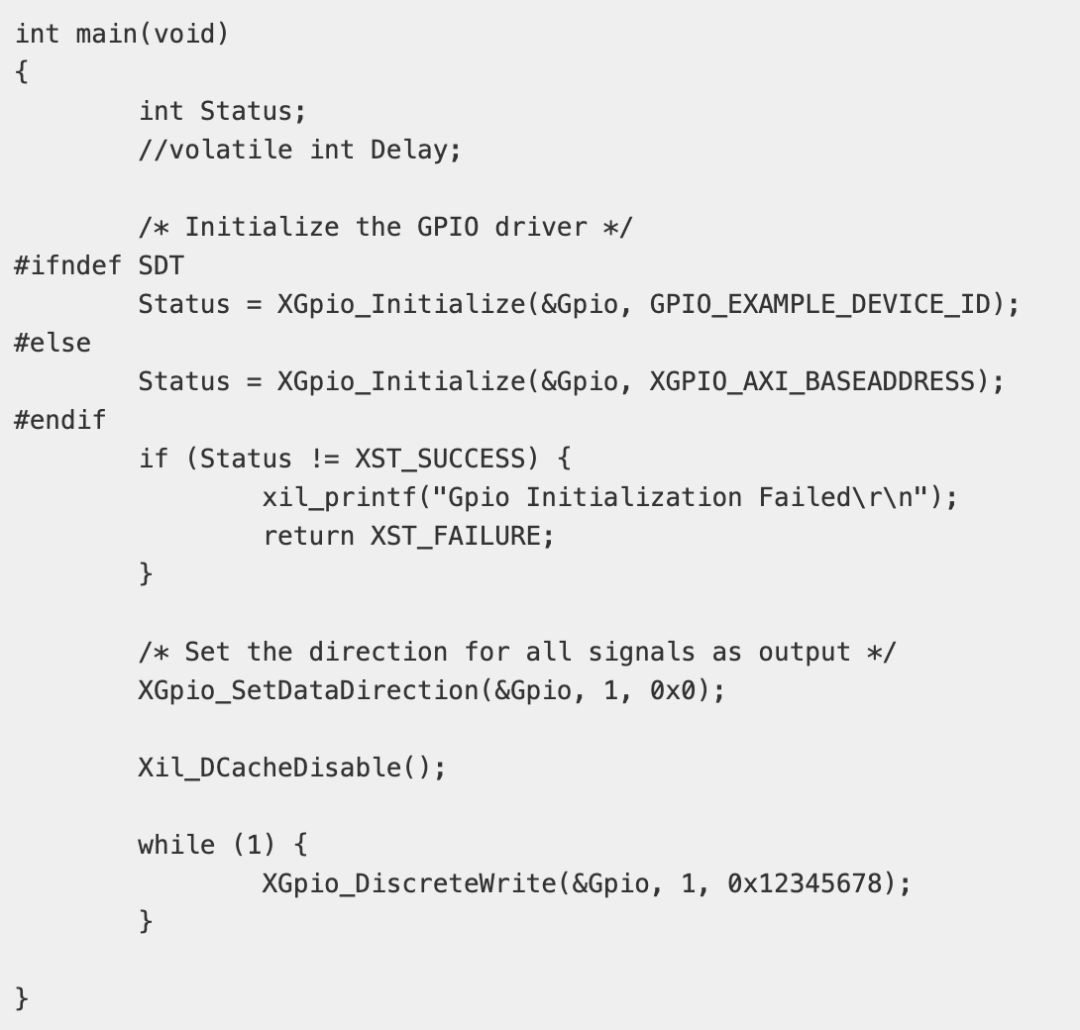

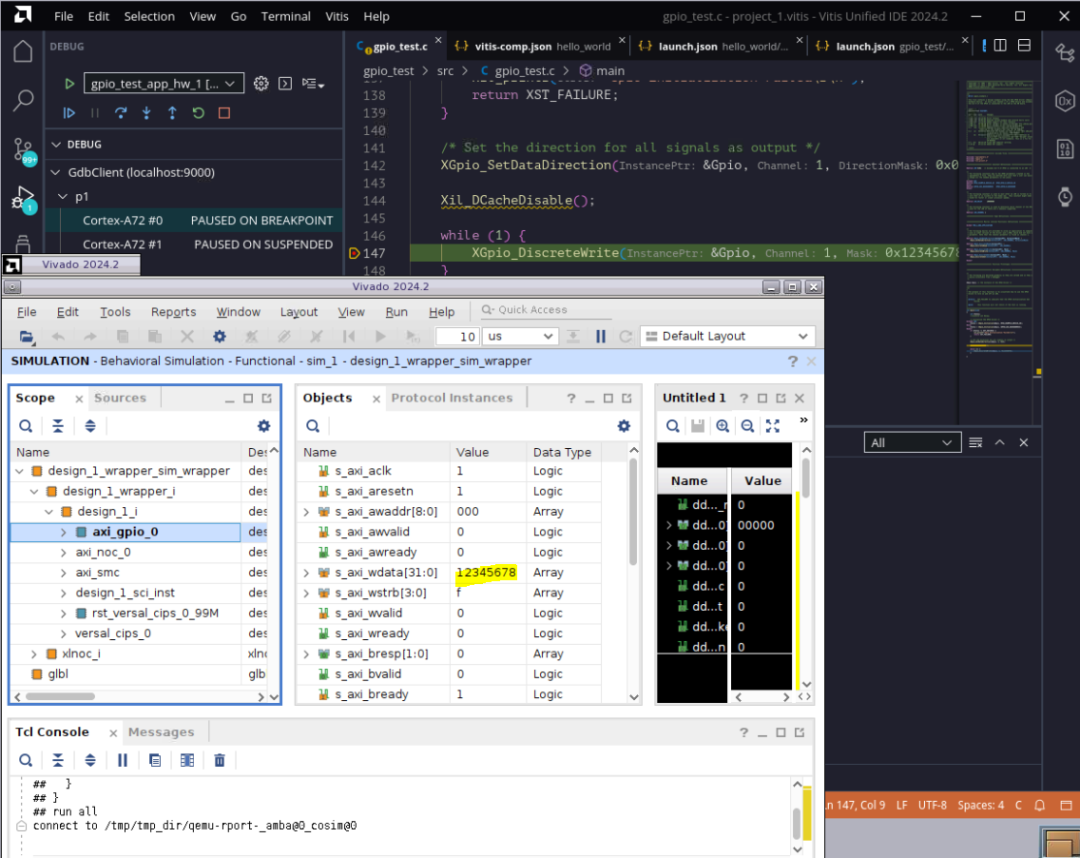

在本博客中已附上此處使用的代碼。以下顯示一段片段用于演示:

如您所見,只將 32 位值 0x12345678 寫入 AXI GPIO 的數據寄存器。

連接 QEMU

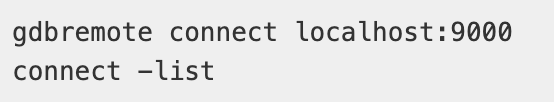

使用上一篇博客中的步驟啟動 QEMU。用戶可以留意 QEMU 中的 TCF 連接:

此處可以連接到 localhost 的端口 9000。

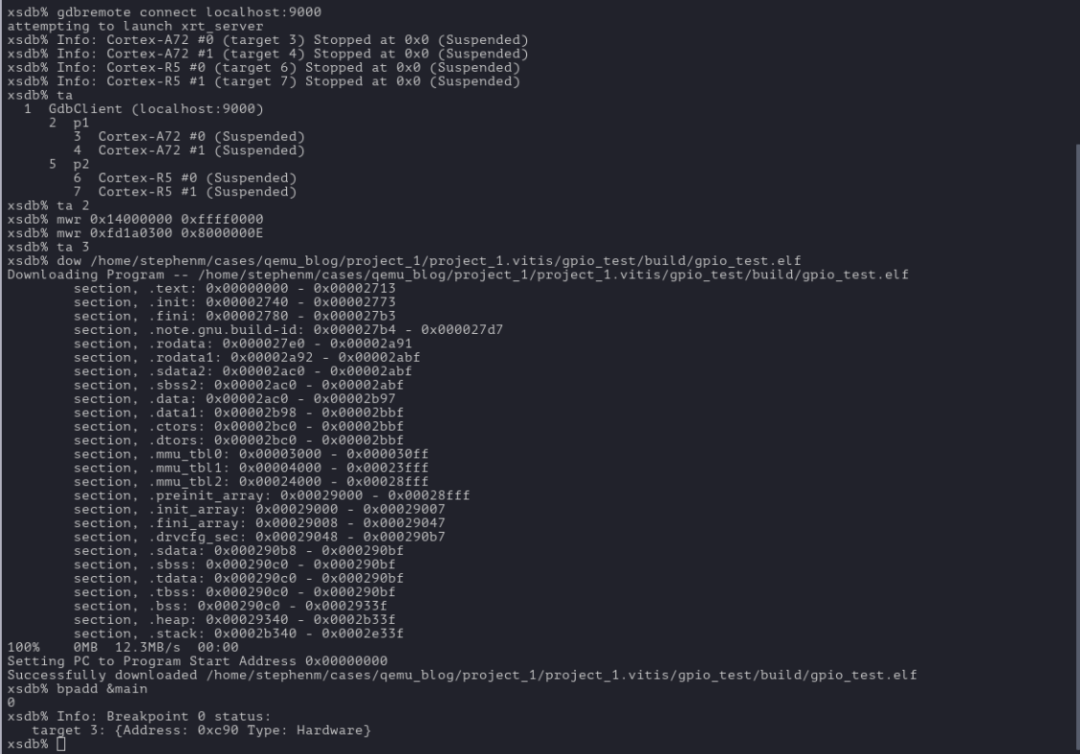

選擇“Vitis -> XSDB Console”打開 XSDB 控制臺,連接到 QEMU,并確保目標可見。

? ? ?

? ? ?

使用“connect -list”獲取連接。我們需要使用此元數據連接到目標連接。

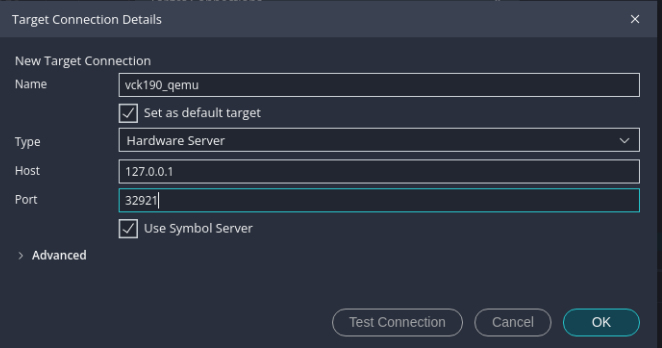

設置目標連接

使用以上 connect -list 命令獲取的端口搭配“Vitis -> Target Connections”中的 localhost (127.0.0.1)。

下載用戶應用 ELF 文件

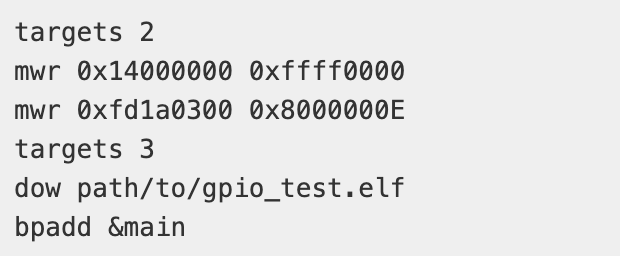

我們將連接到啟動配置中運行中的目標。因此,需要手動下載 ELF,并將斷點設置在 main() 處。并且,由于當前使用 PLM 來燒錄器件,因此不存在對應 Cortex A72 的分區。因此,此處理器將保持置于復位。

我們需要使其解復位。在 OCM 中放置一個啟動循環 (0x14)。

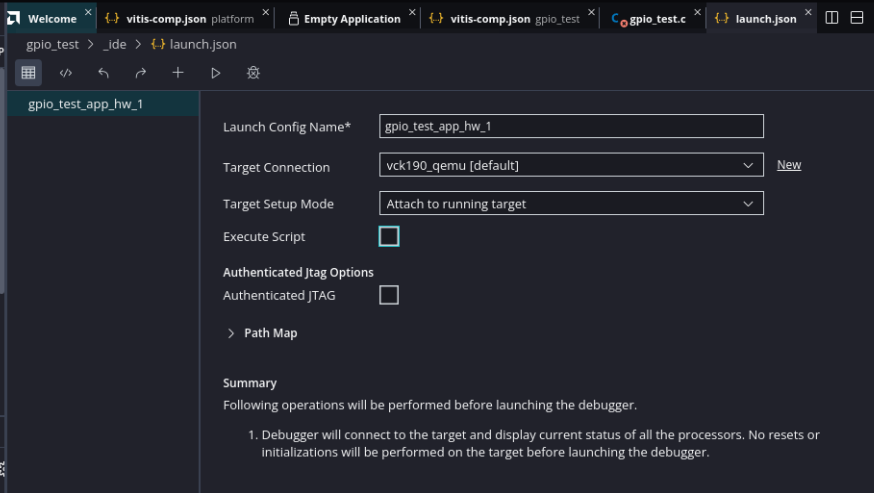

設置啟動配置

我將連接到以上創建的目標連接,并將“Target Setup Mode”設置為“Attach to running target”。

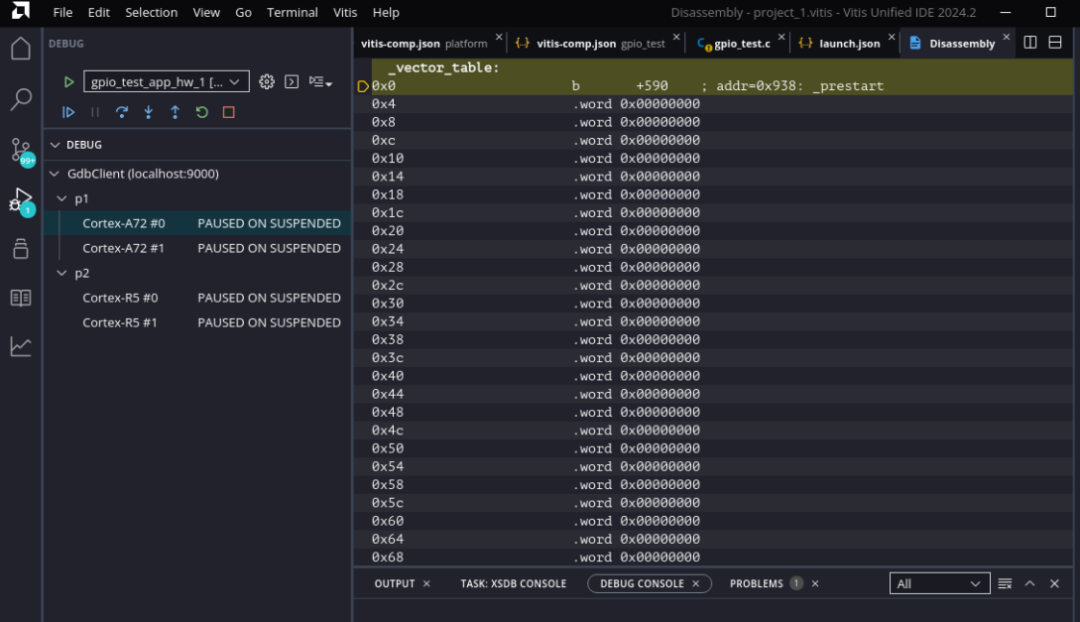

這將跳轉至調試透視圖。由于我們尚未命中位于 Main 處的斷點,因此您將看到啟動代碼。

注釋:請確保您高亮正確的目標,因為它可能已切換到不同的處理器目標。

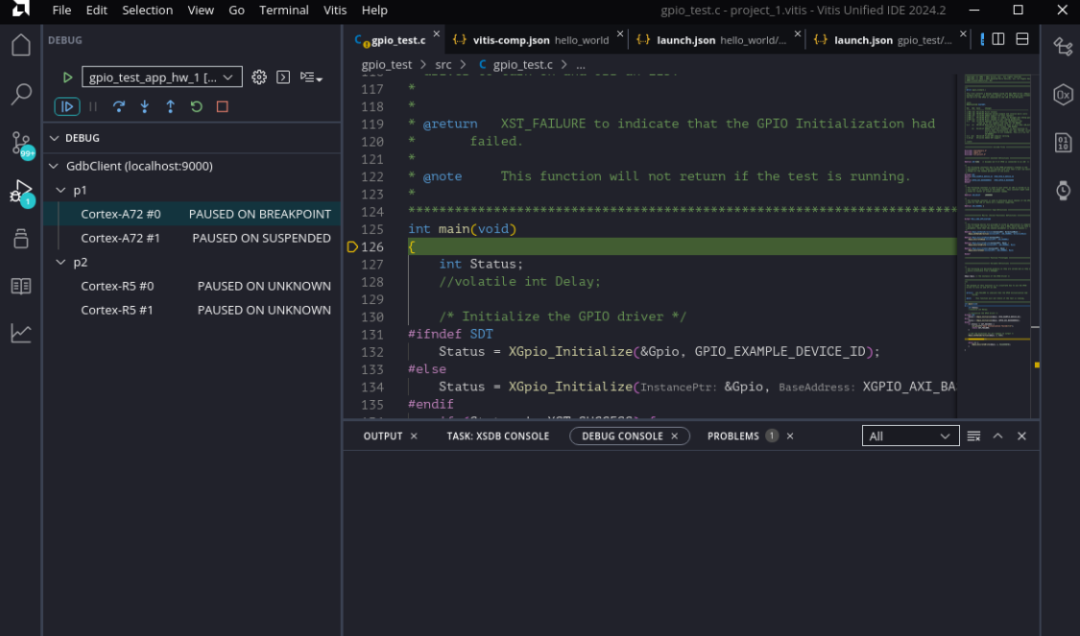

如果您點擊“Continue”,那么應該會命中位于 main() 處的斷點。

如果在 While 循環中設置斷點以寫入 AXI GPIO,即可在 AMD VivadoDesign Suite 仿真器中的 WDATA 管腳上看到傳輸事務:

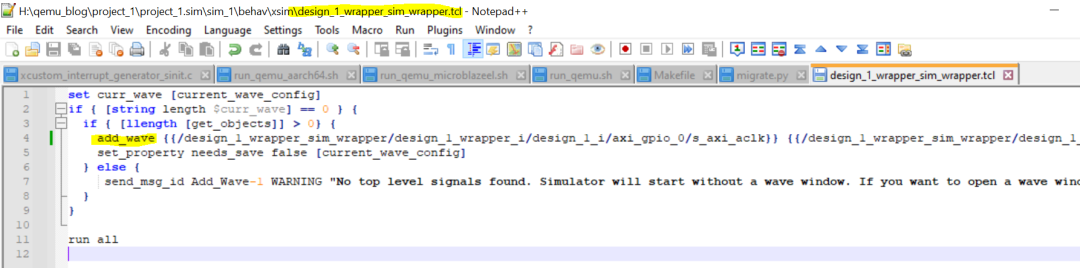

注釋:如果您想要將更多其他信號添加到波形圖中,可以更新仿真目錄中的 Tcl 文件。

例如,在此處添加了 AXI GPIO 接口信號:

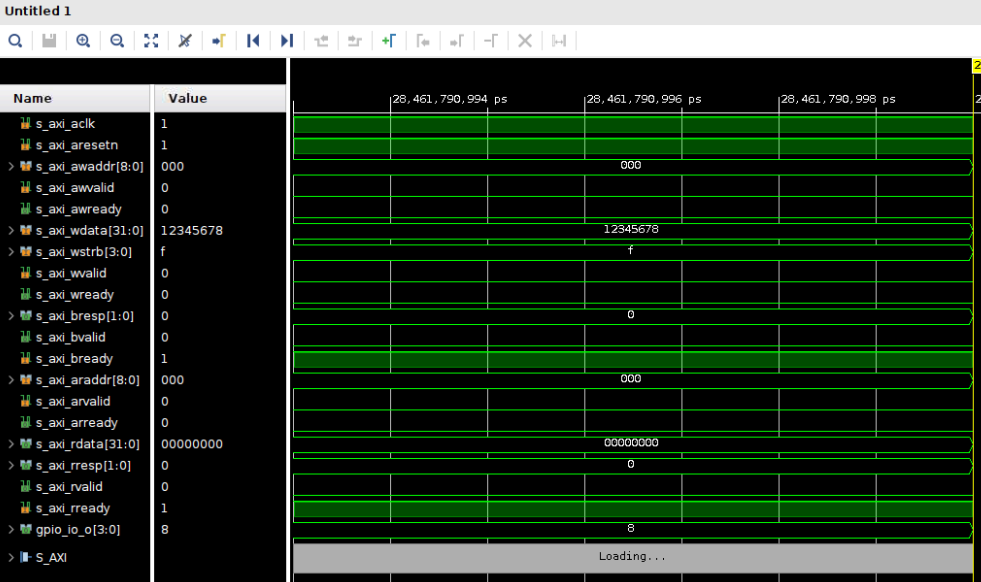

如果重新運行應用代碼,即可在這些端口上看到所期望的如下輸出:

-

amd

+關注

關注

25文章

5699瀏覽量

140308 -

仿真

+關注

關注

55文章

4527瀏覽量

138592 -

Unified

+關注

關注

0文章

3瀏覽量

8621 -

Vitis

+關注

關注

0文章

158瀏覽量

8421

原文標題:開發者分享|在 AMD Vitis? Unified 中連接到 QEMU

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用AMD Vitis Unified IDE創建HLS組件

在AMD Versal自適應SoC上使用QEMU+協同仿真示例

如何在AMD Vitis Unified IDE中使用系統設備樹

Vitis2023.2使用之—— classic Vitis IDE

Vitis2023.2使用之—— updata to Vitis Unified IDE

如何在Vitis中封裝加速平臺?

使用AXI4-Lite將Vitis HLS創建的IP連接到PS

Vitis 統一軟件平臺文檔

在Windows 10上創建并運行AMD Vitis?視覺庫示例

如何在AMD Vitis Unified 2024.2中連接到QEMU

如何在AMD Vitis Unified 2024.2中連接到QEMU

評論