在本篇博文中,我們將探討如何在 Vitis 中調試 Zynq UltraScale 器件啟動鏡像。這些啟動鏡像包括 ARM 可信固件 (ATF) 和 U-boot。

本篇博文乃是系列博文中的一篇,此系列博文旨在探討如何在 Petalinux 鏡像中調試各種組件。

啟動鏡像調試是任何定制板啟動過程中不可或缺的一環,希望本篇博文能夠幫助用戶完整完成定制板啟動鏡像的調試工作。即使您使用的是開發板,本篇博文也將能夠提供有關啟動鏡像在 Zynq UltraScale 器件上的工作方式方面的諸多實用見解。

啟動鏡像的生成途徑多種多樣。用戶可以使用 PetaLinux/Yocto,或者也可以從 GiT 源代碼手動構建鏡像。本文將演示如何使用 PetaLinux 2020.1 來為 Zynq UltraScale 器件創建啟用調試功能的啟動鏡像。

PetaLinux 流程:

在此次演示中使用的是 ZCU104 板,但其中步驟應適用于所有 Zynq UltraScale 器件。

在 images/Linux 文件夾中提供的 u-boot.elf 不具有在 Vitis 中進行調試所需的符號信息。因此,我們將使用 PetaLinux 內的工作目錄下的 u-boot 二進制文件。

并且 PetaLinux 移除了其中間文件以節省磁盤空間,因此我們需要在 PetaLinux 工程中禁用此功能。

下列步驟演示了用戶如何獲取啟用調試功能的 ATF 和 U-boot:

petalinux-create -t project --template zynqMP -n linux_image

cd linux_image

注: 很遺憾,在 PetaLinux 存在 1 個已知問題,即無法將 debug=1 傳遞到此處的 makefile。用戶可以使用此處所述的變通方法來手動添加該值。

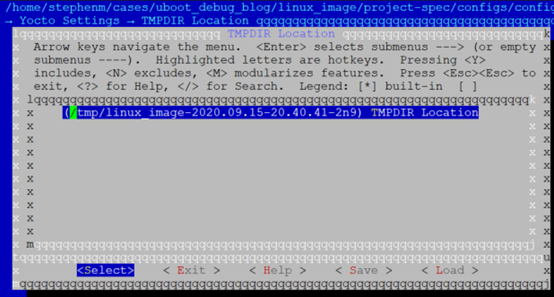

用戶還應注意 TMP 目錄:

退出“配置 (Config)”屏幕并單擊“Save”以保存。

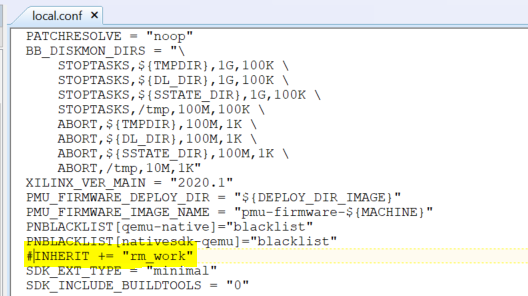

如上所述,PetaLinux 提供的 u-boot 可執行文件不具有調試所需的符號信息。用戶可以通過修改 build/conf 文件夾下的 local.conf 文件來阻止 PetaLinux 移除中間構建文件。

創建任何構建時都會創建 build 文件夾,因此我們可以執行 petalinux-build,隨后使用 Ctrl + c 在創建此文件時停止操作。打開 local.conf 文件并注釋掉以下行:

現在,只需構建啟動鏡像并使用 PetaLinux 創建可啟動鏡像 (BOOT.BIN) 即可

petalinux-build -c bootloader

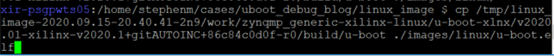

完成構建后,將 u-boot 重命名為 u-boot.elf 并從 tmp 文件夾復制到 images/linux 文件夾中:

下一步,使用 PetaLinux 創建可啟動鏡像 (BOOT.BIN)

cd images/linux

petalinux-package --boot --u-boot

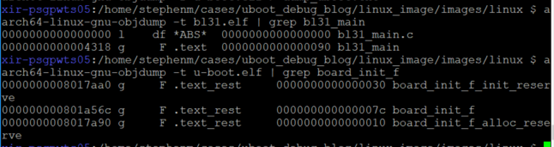

作為完整性檢查,我們還可測試可執行文件以確認其中包含符號信息:

在 Vitis 中執行調試:

我發現調試啟動鏡像最簡單的方法是將啟動鏡像加載到 SD/QSPI 上,并在運行目標上執行調試。

啟動 Vitis 并關閉歡迎屏幕。

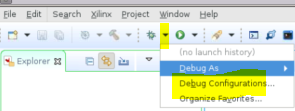

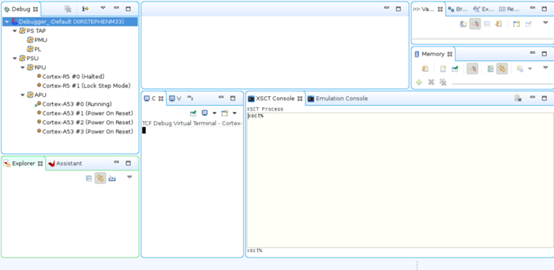

創建新的“調試配置 (Debug Configuration)”:

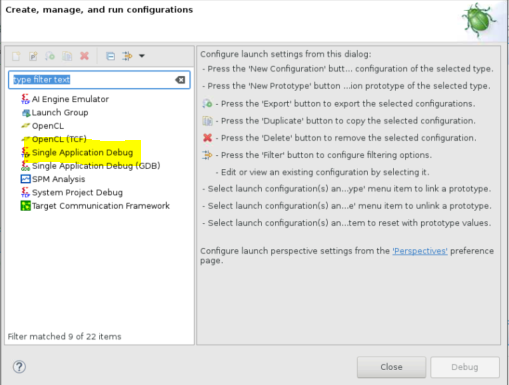

雙擊“單應用調試 (Single Application Debug)”:

將“調試類型 (Debug Type)”設置為“連接到運行目標 (Attach to Running Target)”:

注: 由于我當前使用遠程連接,因此還需一并設置遠程連接。

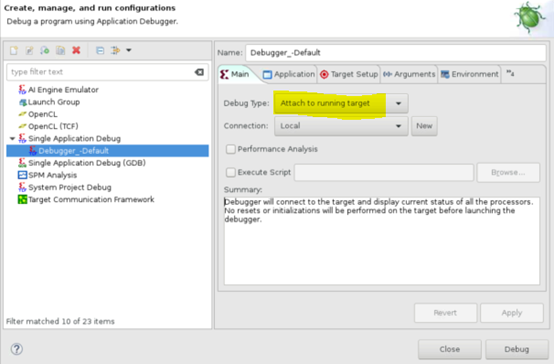

選擇“應用并調試 (Apply and Debug)”。這樣即可打開調試透視圖。

您可以看到其中 Cortex A53 正在運行(我們的啟動鏡像)。

重定位前的調試:

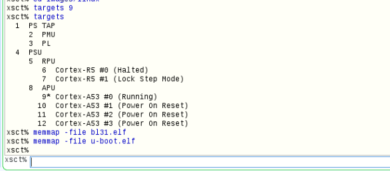

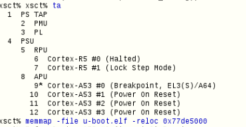

展開賽靈思軟件命令行工具 (XSCT) 窗口。

我們要在其中將符號文件傳遞給 Cortex A53 #0 以供 ATF 和 U-Boot 使用。

在 XSCT 中使用 memmap 命令設置符號文件:

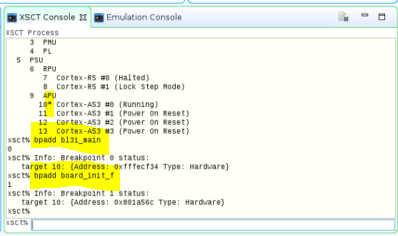

然后即可在 ATF 和 U-Boot 中添加中斷點。

我將 ATF 中的中斷點設置在 bl31_main,將 U-boot 中的中斷點設置在 board_init_f:

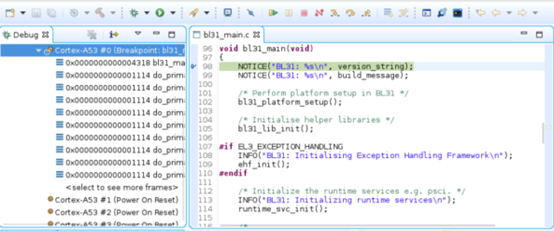

如果將板掉電并重新上電,則會在 ATF 中看到中斷點被命中。

隨后,用戶可以執行恢復 (resume)、單步進入 (step into)、單步跳過 (step over) 等:

用戶可以單步執行此處代碼。例如,用戶可以使用其中的 setup_reloc 功能來查找 uboot 重定位地址(或者使用 bdinfo)。

重定位地址因用戶而異,我這里的重定位地址為 0x77DE5000。

重定位后的調試:

uboot 代碼將對自身進行重定位,由于我們已映射符號文件存儲器,因此,該重定位地址是錯誤的。

由此導致我們需要傳遞重定位地址以便調試器能夠對此進行補償:

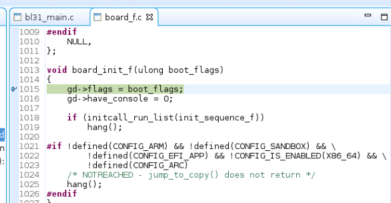

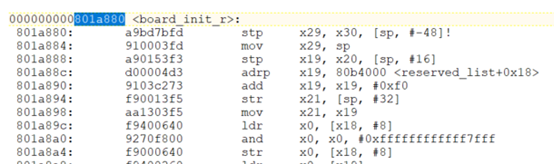

讓我們使用 board_init_r 功能。

這是重定位后處理功能:

重定位后,board_init_r 地址將變為 0x77DE5000 + 0x801A880 = 0x7FDFF880。

如果我在 board_init_r 處添加中斷點,即可看到實際地址符合預期:

如果此時掉電并重新上電,則將命中 ATF 中的中斷點,并且此時還會命中重定位后的 U-boot。

編輯:jq

-

Linux

+關注

關注

88文章

11798瀏覽量

219403 -

u-boot

+關注

關注

0文章

135瀏覽量

39882 -

Vitis

+關注

關注

0文章

158瀏覽量

8421

原文標題:PetaLinux 鏡像調試系列-在 Vitis 中調試 ARM 可信固件和 U-boot

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

visionfive如何使用uart傳鏡像到內存,然后啟動它呢?

AMD Versal自適應SoC中eMMC燒錄/啟動調試檢查表(下)

AMD Versal自適應SoC中eMMC燒錄/啟動調試檢查表(上)

深入解析U-Boot image.c:RK平臺鏡像處理核心邏輯

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

如何在AMD Vitis Unified IDE中使用系統設備樹

如何在AMD Vitis Unified 2024.2中連接到QEMU

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構架構下的智能邊緣計算標桿

如何在Unified IDE中創建視覺庫HLS組件

使用AMD Vitis Unified IDE創建HLS組件

如何在 Vitis 中調試 Zynq UltraScale 器件啟動鏡像

如何在 Vitis 中調試 Zynq UltraScale 器件啟動鏡像

評論