介紹

DesignLinx 及其客戶是賽靈思 SDAccel 開發環境的早期用戶。他們使用 SDAccel 開發環境,針對搭載加速軟件的亞馬遜 AWS F1 和賽靈思 Alveo 數據中心加速器卡,開發云端應用和本地應用。

結合 SDSoC 和賽靈思 SDK,SDAccel 流現在是 2019.2 Vitis 統一軟件平臺的組成部分,便于開發者針對賽靈思器件上的所有軟件任務使用統一平臺。下面分享來自 DesignLinx 公司高級嵌入式軟件工程師 Nathan Sullivan 所撰寫的技巧:

1. Vitis 的優勢

Vitis 2019.2 采用經過更新的 v++ 編譯器,強化 IDE 項目組織,為嵌入式應用和數據中心應用提供統一的工具流。因為全部三種流程現在都集成在 Vitis 內部,所以無需針對不同類型的應用在 SDAccel、SDK 和 SDSoC 之間進行切換。除了 Vitis IDE 以外,通過 v++ 工具和 SDAccel 提供的 xocc/xcpp 流等生成文件,也為構建軟件提供完整的命令行流程。

2. 易于遷移

Vitis 2019.2 使用 gcc 編譯 C 語言源代碼,使用 Vivado HLS 編譯與 SDAccel 流匹配的加速內核。此外,Vitis 也使用與 SDAccel 相同的目標平臺和賽靈思運行時。這意味著新環境能夠兼容源代碼,SDAccel 項目只需少量修改或完全無需任何修改就能在 Vitis 內完成構建。在遷移源代碼時,用戶能夠使用 Vitis IDE 或 v++ 命令行工具鏈選擇性構建新項目。

3. IDE 遷移

使用 Vitis IDE 遷移項目時,只需將所有源代碼文件從 SDAccel 項目添加到新的 Vitis 項目中,最好是指向同一器件。使用右鍵菜單上的“import sources”選項能夠輕松完成這一操作。一旦源文件導入完成,必須向二進制容器添加內核函數(如同它們在原始項目中那樣),并且任何定制構建設置也需要手動復制。

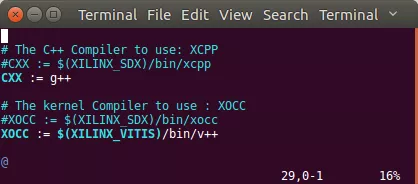

4. 命令行遷移

要對使用命令行(通常是通過生成文件)構建的項目進行遷移,必須用 v++ 調用替換 xocc 調用。類似地,必須用 g++ 調用替換 xcpp 調用,即直接調用主機 c++ 編譯器。新的 v++ 工具提供的命令行選項與 SDAccel 下的 xocc 工具一樣,因此無需做其他修改。請參閱 UG1393 進一步了解 Vitis 2019.2 有關工具變化的詳細說明。

在 SDAccel 樣例生成文件中替換 XOCC 和 CXX

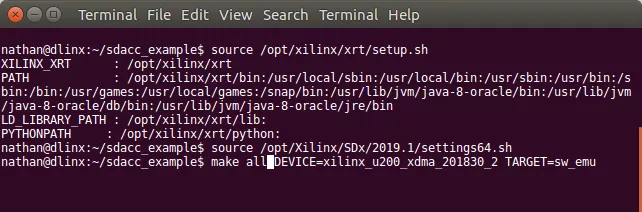

修改完成后,就可以使用 Vitis 工具構建之前的 SDAccel 項目:

和以往一樣構建 SDAccel 示例,但這次使用 Vitis 路徑和工具

5.結論

雖然 Vitis 2019.2 將所有賽靈思軟件工具集成在統一平臺上,但 SDAccel 流并沒有顯著變化,這使得遷移工作簡單易行。現有項目在源代碼上兼容新工具鏈,因此基本無需修改,它們就能直接獲得 Vitis 2019.2 統一軟件平臺提供的優勢。

賽靈思高級合作伙伴 DesignLinx 為運行在 Vitis 和 SDAccel 平臺上的加速應用提供開發服務,同時提供云端和本地硬件部署服務。

-

賽靈思

+關注

關注

33文章

1798瀏覽量

133426 -

數據中心

+關注

關注

18文章

5649瀏覽量

75012

原文標題:將 SDAccel 項目遷移到 Vitis 2019.2 的技巧

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于Vitis Model Composer完成全流程AI Engine開發

急急急!我正在使用vivado2019.2,請幫忙生成一個項目。

電子材料抗離子遷移方案!東亞合成 IXE/IXEPLAS,智美行科技免費試樣

無質量損失的數據遷移:Nikon SLM Solutions信賴3Dfindit企業版

如何在AMD Vitis Unified IDE中使用系統設備樹

AMD Vitis AI 5.1測試版現已開放下載

AMD Vitis AI 5.1測試版發布

求助,關于Cysub.dll 在 dotnet8 上的兼容性問題求解

如何在AMD Vitis Unified 2024.2中連接到QEMU

全新AMD Vitis統一軟件平臺2025.1版本發布

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

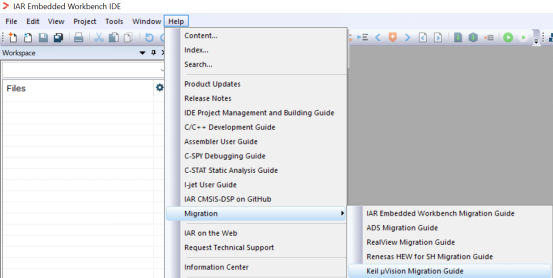

從Keil MDK到IAR EWARM:通過工程遷移實現項目資產的更好管理

將SDAccel項目遷移到Vitis 2019.2的技巧

將SDAccel項目遷移到Vitis 2019.2的技巧

評論