Alveo系列開發板上的平臺其實是一個DFX設計的靜態部分,在Vitis 統一軟件平臺中使用Alveo系列開發板設計加速Kernel, 最終這些Kernel的邏輯會在分布在DFX設計的動態區域。

本篇將介紹如何為Kernel的邏輯做floorplan(畫Pblock),人為控制Kernel邏輯的布局。

我們以經典Example design“Vector Addition” 為例:

1. 打開Vitis 2020.2,創建新的 Application Project

File -> New -> Application project

2. 選擇xilinx_u200_qdma_201910_1平臺 (本篇討論的方法不局限于某個具體平臺)

3. 選擇打開Example Design "Vector Addition"

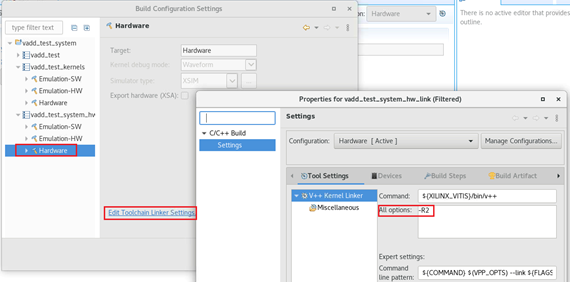

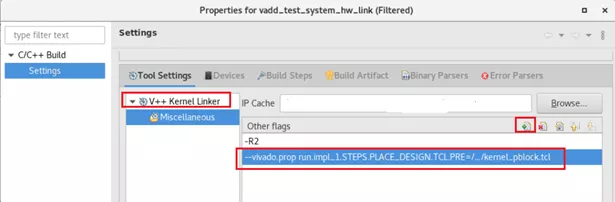

4. 對Hardware Flow 在Link階段設置 "-R2",然后Build

此處report level 選擇-R2:VPL(Vitis Platform link) 過程輸出更多中間文件, 后續我們會用到畫Kernel Pblock所需要的opt.dcp

5. 不用等到生成xclbin文件,VPL完成opt_design步驟之后我們就能看到XX_opt.dcp 文件.

XX_opt .dcp 所在目錄及文件名:

vitis_pblock_u200/vadd_test_system_hw_link/Hardware/binary_container_1.build/link/vivado/vpl/prj/prj.runs/impl_1 pfm_top_wrapper_opt.dcp

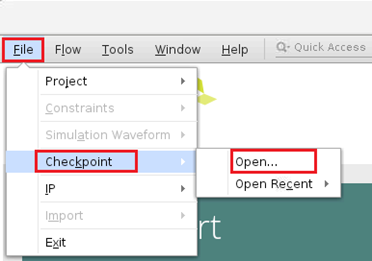

6. 把這個XX_opt.dcp拷貝到另外的目錄,并用Vivado打開這個dcp 文件

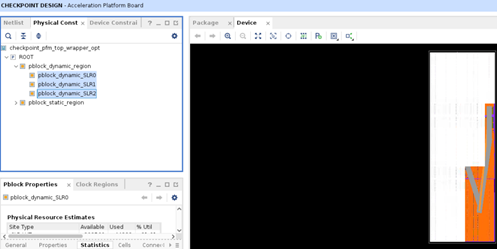

7. 查看已有的Pblock。主菜單 Window -> Physical Constraints

在這個視圖可以看到平臺已經為動態區域在各個SLR中設置了相應的Pblock, 而且需要注意的是,設計中已有的Pblock是有層級關系的

例如:pblock_dynamic_region 包含三個下級pblock:

pblock_dynamic_SLR0,

pblock_dynamic_SLR1,

pblock_dynamic_SLR2,

提醒:不同平臺SLR的數目也可能是不同的. 不同平臺中自帶pblock的名字有差異是正常的. 需要用戶自己觀察.

為Kernel模塊生成的Pblock應該是pblock_dynamic_SLR0 這一級Pblock 的子模塊, 工具支持把同一個Kernel的不同部分放置到多個SLR中,用戶需要保證跨SLR路徑的時序.

8. 為Kernel模塊畫Pblock

在這里嘗試把Kernel 放置在pblock_dynamic_SLR0所屬的中心區域

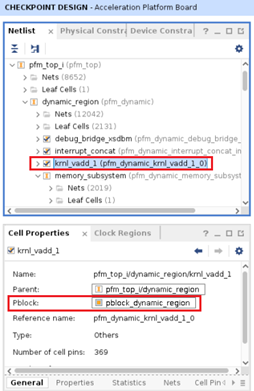

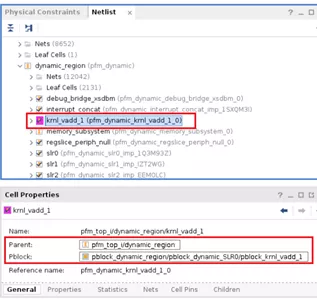

. 在Vivado的Netlist View中選中Kernel 模塊

例子中的模塊名是 pfm_top_i/dynamic_region/krnl_vadd_1

. 可以在Cells properties 窗口看到這個模塊當前所屬的Pblock是pblock_dynamic_region

. 點擊Device 視圖中的"Draw Pblock" 按鈕, 在Device視圖上原有pblock_dynamic_SLR0的范圍內畫一個方框,新畫的Pblock所覆蓋面積要被原Pblock完全包含. 畫完之后還可以選中Pblock微調Pblock的邊界,同時為了不影響原來Pblock的結構,在TCL CONSOLE中用以下命令把新Pblock的Parent Pblock設置成pblock_dynamic_SLR0:

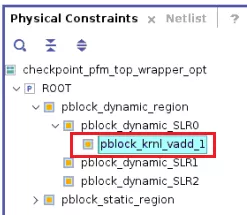

set_property PARENT pblock_dynamic_SLR0 [get_pblocks pblock_krnl_vadd_1]

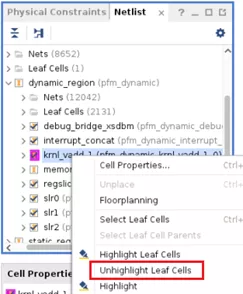

. 再看Kernel 模塊的Pblock屬性,已經變為pblock_krnl_vadd_1

在TCL CONSOLE中會打印出了畫pblock相應的約束,我們可以將這些約束拷貝到一個新的tcl文件中保存.

(在這里保存到kernel_pblock.tcl)

看下更新的Pblock結構,新生成的pblock_krnl_vadd_1 是pblock_dynamic_SLR0的Child Pblock

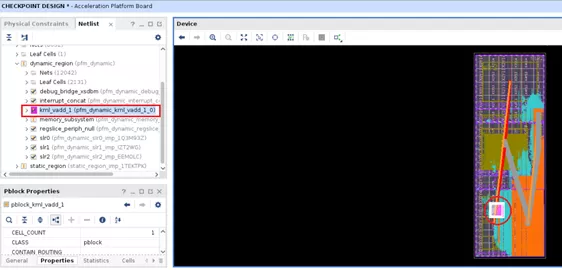

繼續在TCL CONSOLE執行 place_design 命令完成布局

理論上這一步可以跳過,如果你確信你畫的Pblock沒有問題的話。

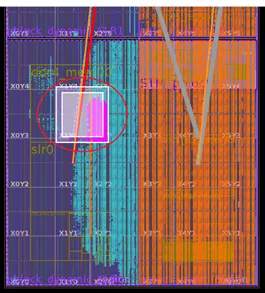

完成place_design之后,可以觀察一下Kernel 的資源在Device 上的實際分布情況

可以看到Kernel的邏輯全部都分布在剛才所畫的Pblock 區域內

9. 在Vitis的link階段做以下設置,使之前保存的畫Pblock的命令在VPL(Vitis Platform link) 的place_design步驟執行之前生效

--vivado.prop run.impl_1.STEPS.PLACE_DESIGN.TCL.PRE=XX/kernel_pblock.tcl

10. 重新build Vitis 的Hardware flow, 之前加入的命令就會生效。

總結: 這就是一個簡單的為Kernel邏輯創建面積約束(Pblock)的過程, 實際用戶也可以為Kernel的子模塊創建Pblock,這方面工具沒有限制。

審核編輯:劉清

-

開發板

+關注

關注

26文章

6290瀏覽量

118074 -

Kernel

+關注

關注

0文章

50瀏覽量

12076

發布評論請先 登錄

Vivado時序約束中invert參數的作用和應用場景

如何在AMD Vitis Unified IDE中使用系統設備樹

AMD Vitis AI 5.1測試版現已開放下載

AMD Vitis AI 5.1測試版發布

如何在AMD Vitis Unified 2024.2中連接到QEMU

如何在Unified IDE中創建視覺庫HLS組件

全新AMD Vitis統一軟件平臺2025.1版本發布

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

如何在Vitis加速設計中為Kernel創建面積約束

如何在Vitis加速設計中為Kernel創建面積約束

評論