第一章 FPGA設計之時序約束四大步驟

作者:潘文明

本文章探討一下FPGA的時序約束步驟,本文章內容,來源于配置的明德揚時序約束專題課視頻。

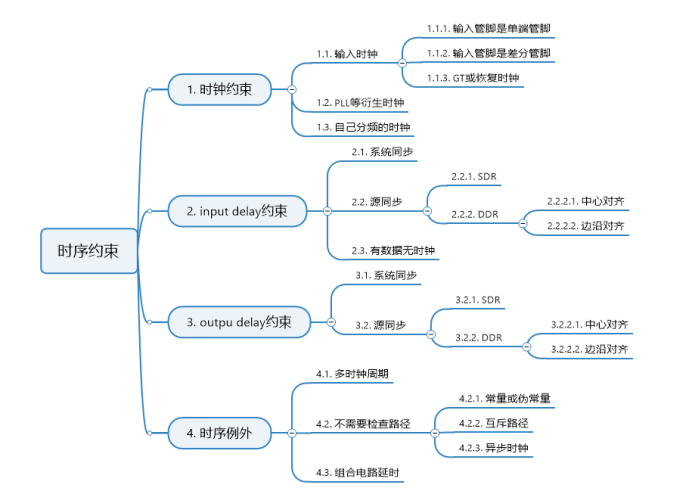

時序約束是一個非常重要的內容,而且內容比較多,比較雜。因此,很多讀者對于怎么進行約束,約束的步驟過程有哪些等,不是很清楚。明德揚根據以往項目的經驗,把時序約束的步驟,概括分成四大步,分別是時鐘的約束、input delays的約束、output delays的約束和時序例外。

時序約束是有先后的,首先要做時鐘約束、其次是input delays約束、再次是output delays約束,最后才是時序例外的約束。這是一個完整的大步驟,也就是說我們在項目開始階段就可以約束我們的時鐘,把我們時鐘的頻率、周期、來源等等定義好。這一步做完之后,先不要做二三四步。這時候我們要完成我們的設計,要把我們內部的時序都完成之后才做第二步設置“input delays”,比如說我們從外部進來的一個情況。第三步output delays,也就是說要往下游器件發送的一個時序情況。當這一二三步都做完之后,我們在最后項目的階段才做一個時序例外的情況。時序例外也就是說哪些時序是不需要分析的,這種情況要設置好。最后我們才能把整個時序約束完成。

以上是大的步驟,但事實上每一個步驟又可以細分成很多種情況。例如時鐘約束,時鐘可以分很多種,一種是差分時鐘,一種是管腳進來的時鐘、還有我們PLL產生時鐘等等。還有一種是有數據但沒有時鐘的情況。input delays、output delays 也有很多種,我們到底要怎么樣去分析,怎么去看。明德揚就把這四個步驟再進行細化,就是根據情況來分別列出來。

下面分別展開描述。

第1節 時鐘

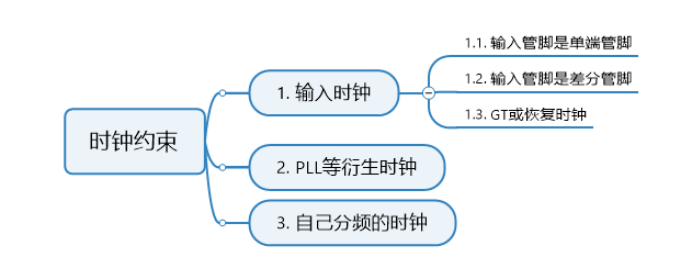

時鐘約束可以分成很多種情況,不同的情況就有不同的約束方法,一般有哪幾種情況呢?

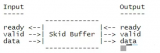

如上圖,時鐘約束概括地,可以分成三種情況,分別是輸入時鐘、PLL等衍生時鐘以及自己分步的時鐘。

1.1 輸入時鐘

輸入時鐘是指時鐘從FPGA管腳進來的情形,這也是最常見的情況。根據輸入的管腳的不同,輸入時鐘情況又可以分成:輸入管腳是單端的、輸入管腳是差分的,以及GT或者恢復時鐘三種情況。

第一種:輸入管腳是單端的,即時鐘直接從管腳進來、并且是單端信號。例如普通低速晶振,大部分是這種情況,明德揚的FPGA ALTERA學習板,如MP801、MP603,其時鐘均是由晶振產生,送到FPGA,并且是單端的信號。

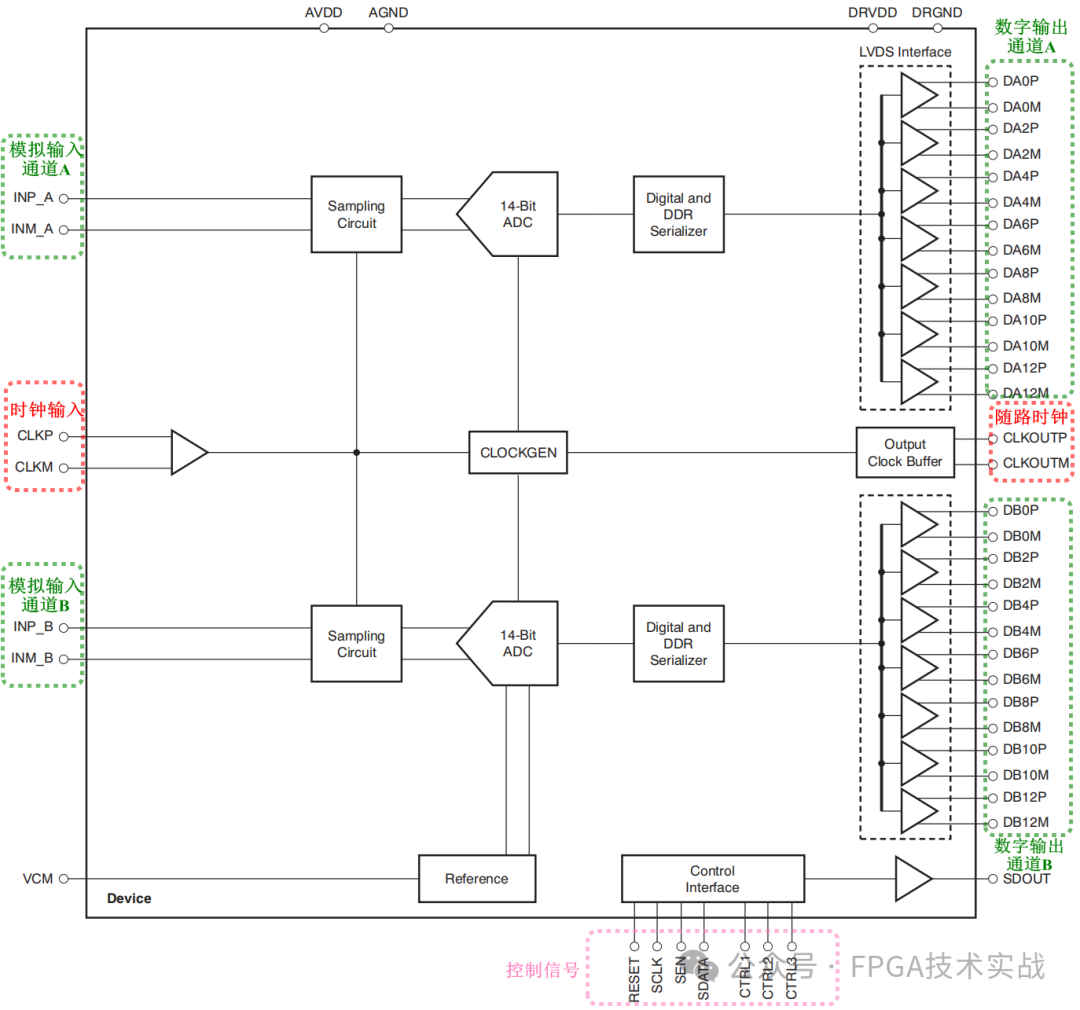

第二種:輸入管腳是差分的,即時鐘直接從管腳進來,并且是差分信號。大部分高速晶振、LVDS接口等,屬于此情形。例如明德揚FPGA XILINX學習板,如MP802,其包含了PCIE管腳,其輸入的時鐘就是差分的;這個板子的DDR的驅動時鐘,時鐘頻率在200M左右,也是屬于此種以情形。

第三種:GT或者恢復時鐘,即使用了高速收發器的情形。在高速收發器管腳中,是沒有時鐘的,時鐘已經嵌入到數據里面,使用FPGA的GTX IP核接收數據,并且從數據恢復出時鐘。這個恢復出來的時鐘就是此種情形。最常見的就是光纖接口。

1.2 PLL等衍生時鐘

那假如說我不是輸入管腳,而是PLL產生的輸出時鐘,這個 就是PLL等衍生時鐘。這種時鐘,FPGA的工具,會自行推導,一般無需約束,但實質應用中,強烈建議約束,會有好處的,好處在下一篇文章中說明。

1.3 自己分頻的時鐘

還有一種情況是自己分頻的時鐘,假如說我們自己寫了一個計數器,把它二分頻、四分頻、八分頻等,分頻出來的信號當為時鐘,這種情況就是自己分頻的時鐘。

首先說明,明德揚不推薦使用此方法來產生時鐘。但確實要用到分頻時鐘時,那就要記得做時鐘約束。這種情況下要怎么進行約束呢?

以上概括了說明了時鐘的幾種情況,每種情況下,其約束方法都有些不同以及注意點。具體約束方法,可以看后續文章的內容。

第2節 input delays

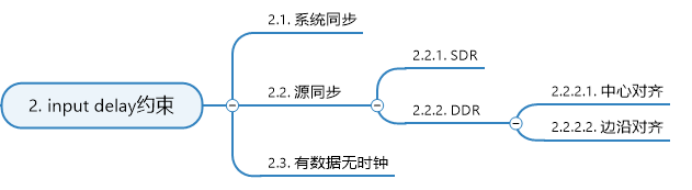

input delay約束,即輸入延時約束,是時序約束的重點,input delay 又分幾種呢?

如上圖,input delay約束概括地,可以分成三種情況,分別是系統同步、源同步和有數據無時鐘。

2.1 系統同步

第一個是系統同步方式,也就是說整個電路板上FPGA以及上游器件都共用一個時鐘,并且相位嚴格相同,這個就是系統同步的方式。

2.2 源同步

第二種是源同步的方式,源同步是怎么樣?就是上游器件,把數據和時鐘信號一起送到FPGA上來的,那這種就是源同步。

源同步是更常用的一種方式,系統同步比較少用,為什么呢?因為要做到上游器件跟FPGA的相位差為0,沒有一點時鐘差,這種要求非常高。而源同步是數據跟時鐘都是從上游器件一起輸送過來給FPGA,這是一種更常用的方式。

這個源同步,又有很多種,具體SDR、DDR和有數據無時鐘三種情況。

第一種:SDR。SDR是指時鐘是單沿有效的方式,比如說我只用上升延或者下降延的一個方式,SDR約束的參數,其獲取的方法有兩種:查看上游器件手冊(通過查看上游器的數據手冊,獲取參數)以及通過示波器測量(通過示波器測量信號的相位差,獲取參數)。

第二種:DDR。DDR是另一種方式,它是一種時鐘雙沿有效的一個方式。也就說即用它的上升延,也用它的下降延。例如說我們的DDR2、DDR3的時鐘,都是上下降沿一直采數據的;包括千兆網的RGMII接口,也是通過雙沿的方式。

DDR的這種情況,我們還可以繼續劃分成中心對齊和邊沿對齊兩種情況。

中心對齊是指:時鐘邊沿始終在數據的中間,時鐘上升沿的左右兩邊,數據都是穩定的。邊沿對齊是指:時鐘和數據邊沿對齊的,在時鐘變化沿兩邊,其數據是不穩定的。

第三種:有數據無時鐘。第三種就是有數據無時鐘的情況。例如說常見的串口。串口是直接數據過來的,它是沒有隨路時鐘過來的。而我們用本地時鐘去采樣,就會出現有數據無時鐘。那對于這種我們應該怎么去約束,又是另一種情況。

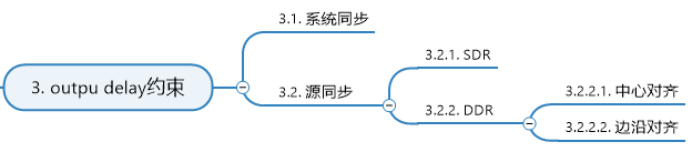

第3節 output delays

輸出延時約束和輸入延時一樣,也是約束的重點。output delay 我們主要分兩種,系統同步和源同步。

3.1 系統同步

整個電路板上FPGA以及下游器件都共用一個時鐘,并且相位嚴格相同,這個就是系統同步的方式。此時FPGA往下游器件發送數據,這時候只傳送數據線就可以了。而時鐘跟FPGA共用一個的,不需要傳時鐘。

3.2 源同步

源同步就是FPGA往這個器件發數據,在發數據過程中也發一個時鐘過去,這是一個隨路時鐘的一個方式,是源同步。

源同步我們還分SDR和DDR。

第一種:SDR。SDR是指時鐘是單沿有效的方式,比如說我只用上升延或者下降延的一個方式,SDR約束的參數,其獲取的方法有兩種:查看上游器件手冊(通過查看上游器的數據手冊,獲取參數)以及通過示波器測量(通過示波器測量信號的相位差,獲取參數)。示波器測量比較少用。

第二種:DDR。DDR是另一種方式,它是一種時鐘雙沿有效的一個方式。也就說即用它的上升延,也用它的下降延。例如說我們的DDR2、DDR3的時鐘,都是上下降沿一直采數據的;包括千兆網的RGMII接口,也是通過雙沿的方式。

DDR的這種情況,我們還可以繼續劃分成中心對齊和邊沿對齊兩種情況。

中心對齊是指:時鐘邊沿始終在數據的中間,時鐘上升沿的左右兩邊,數據都是穩定的。邊沿對齊是指:時鐘和數據邊沿對齊的,在時鐘變化沿兩邊,其數據是不穩定的。

第4節 時序例外

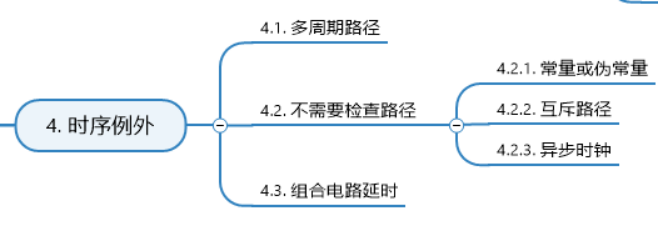

時序例外一般用在clock與IO都約束后,還是不滿足時序要求的情況下。主要包括多周期路徑、不需要檢查的路徑和組合電路延時等三種情況,如下圖。

4.1 多周期路徑

多周期路徑是指完成一個運算需要超過1個時鐘周期的情形,多周期路徑在IC設計領域運用較多,但在FPGA里應用較少。

4.2 不需要檢查的路徑

有一些路徑是不需要分析的,具體可以分成三種:常量或偽常量信號、互斥路徑和異步時鐘。

第一種:常量或偽常量信號。某些信號雖然不滿足時序要求,但實質上該信號在應用場景中,是不會改變的,例如某個開關信號,它在上電時打開后,就一直保持打開狀態,不會變來變去。那么這個信號就可以認為是偽常量信號。假設它不滿足時序要求,也是無所謂的,因為不會變,不會變就意味著建立時間和保持時間肯定滿足,所以不存在問題。這種信號是不需要檢查 的。

第二種:互斥的路徑。可以簡單認為是雙向端口,即代碼中,使用inout定義的信號。

第三種:異步時鐘。即信號從一個時鐘域,跨到另一個時鐘域的情況。這也是不需要檢查 的。注意,這里說不用檢查,是指完成異步信號同步化后,不用檢查的意思。

4.3 組合電路延時

還有一種是組合電路的延時。組合電路延時就是說我從這個管腳到另一個管腳之間,另一個管腳進來,這個管腳出去中間沒有任何一個時鐘,這是組合電路給延時的一種情況。

第5節 總結與建議

前面我們講了時鐘約束、輸入延時、輸出延時還時序例外的情況。每一種情況又分了很多種,根據它的不同類型來區分,每次約束的時候都是其中的一種情況。比如說CLK差分,就去找時鐘,然后根據差分管腳怎么約束,來找到對應情況,按照要求進行約束。這相當于我已經提供一個表給你,你按照這個表去核對。找到對應的情況,按要求進行約束就可以了。

記住:開始的時候,只是配置時鐘,不配置input delay 、 output delays和持續例外。因為我們開始的時候是專心于內部電路,我們時序的一個設計,滿足內部要求之后,再去配置我們的接口。在時鐘完全通過之后再配置input delay 和output delays 。

時序例外是最后差不多要完工了再進行配置的。而且這個配置是要很小心。因為我們實際例外,比如說不用檢查,我們set false path這種情況,設置好就是表示不用檢查。如果在開始的時候,就設置好了,萬一中間又要改變,你改變的話,那你忘了把這個約束給干掉了,這種情況就會出現有錯誤也提示不出來的情況。所以說時序例外應該是最后情況下進行的。

這個順序是明德揚經驗的一個順序,我們的項目基本上是按照這個順序做的。但是不同的公司也會有不同的做法。例如說我一開始全部都不約束,到最后再生約束,這也是可以的。這種做法沒有統一標準,反正學明德揚的課程,你就按這個步驟做,去到其他公司,再根據公司要求去做就可以了。

本文章是基于賽靈思的一個時序約束,ALTERA也是相似的,甚至IC芯片設計領域,也是同樣的思路。

有句話講的很好,我們的時序是設計出來的,不是約束出來的。所以說時序重要還是不重要?當然重要。但是它不是非常重要,更重要的是假如說我時序出現例外,不滿足的時候,更重要是改變你的設計,而不是要求約束。

下一篇文章,我們將具體探討“時鐘約束”的內容,講解各種情況下的時序約束方法。需要更多更詳細的資料,可以找作者了解。

審核編輯:湯梓紅

電子發燒友App

電子發燒友App

評論