1、概述

智多晶EDA工具HqFpga(簡稱HQ),是自主研發的一款系統級的設計套件,集成了Hqui主界面、工程界面、以及內嵌的HqInsight調試工具、IP Creator IP生成工具、布局圖、熱力圖、時序分析等。HQ支持Windows、Linux操作系統利用HQ設計套件,設計人員能夠實現高效率的FPGA工程開發與調試驗證。

HQ在2025年升級迭代新增很多功能,本文將依次介紹HQ整體套件在各個模塊的主要重大進展。

2、增強易用性

2.1 AI助手-晶小助支持

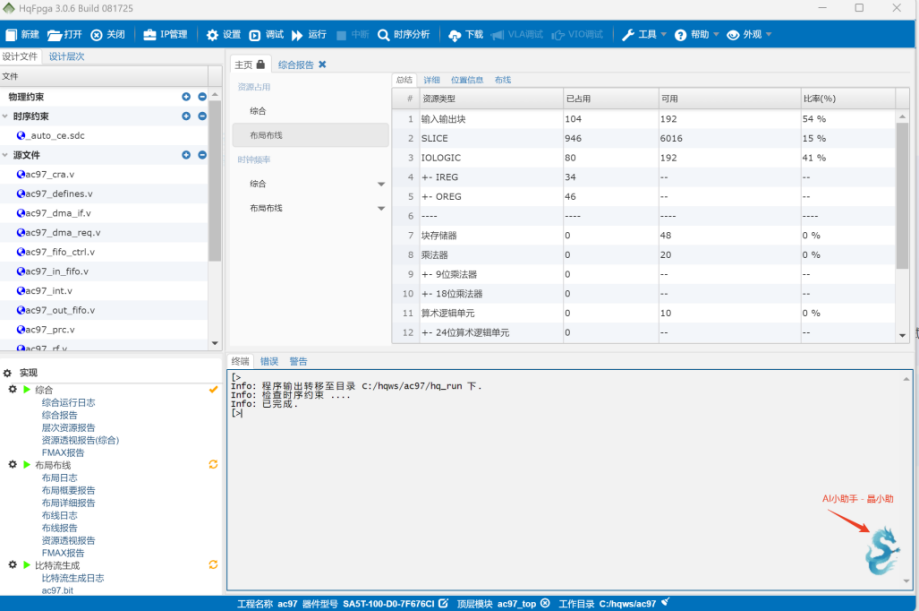

HQ2025接入DeepSeek 大模型,并推出 FPGA 設計專屬 AI 助手——晶小助,如下圖中的右下角。這是 FPGA 領域首次引入大模型 AI 助手,為 FPGA 工程師提供前所未有的智能交互體驗,讓開發更便捷、高效。

晶小助是基于 DeepSeek 大模型構建的智能助手,深度融合了智多晶多年積累的用戶文檔與技術知識。無論是用戶手冊查閱、工具使用、調試建議,還是約束配置與綜合優化,晶小助都能為用戶提供快速、準確的回答。

晶小助支持自然語言提問,內置智多晶知識庫,答案專業可靠,一鍵喚起,隨時隨地解疑答惑,可以避免翻閱手冊,節省查閱時間。

使用示例

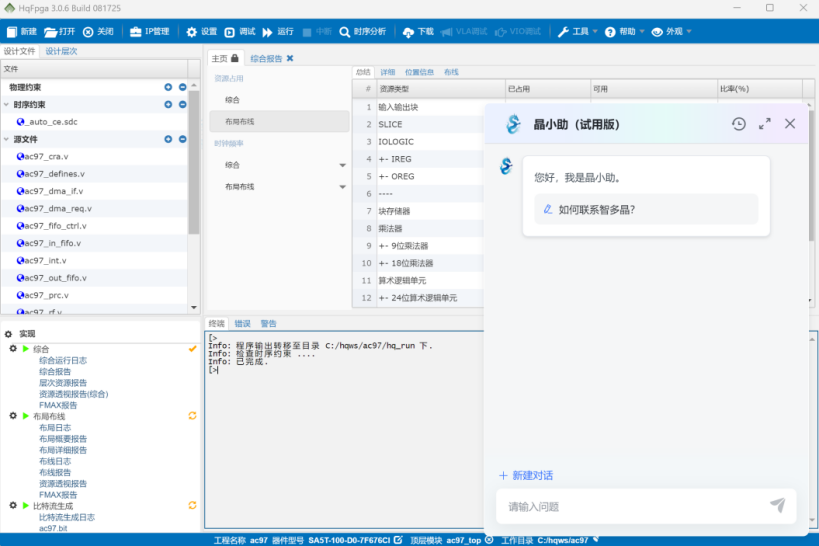

點擊晶小助圖標,彈出下面左圖的對話框,在編輯框輸入問題。比如輸入“HqFpga安裝指南”,晶小助會給出如下面右圖所示的安裝說明。

2.2設計報告

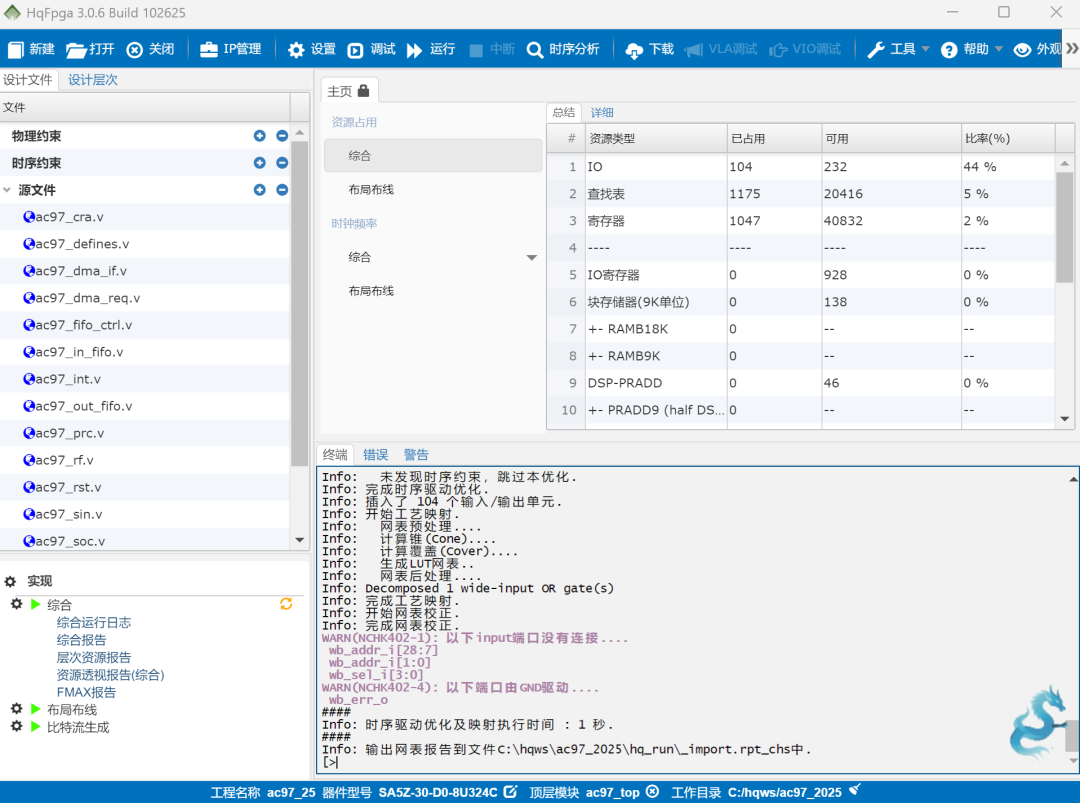

2.2.1資源透視報告

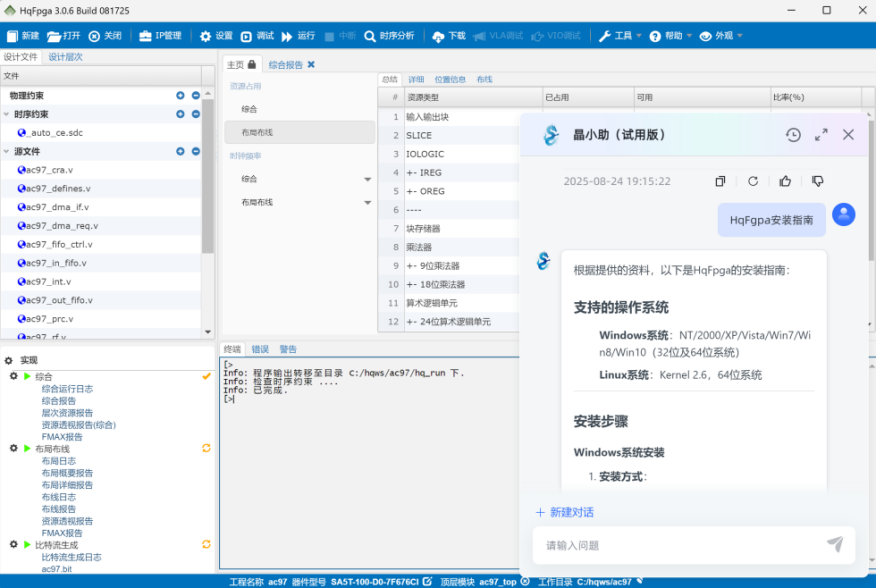

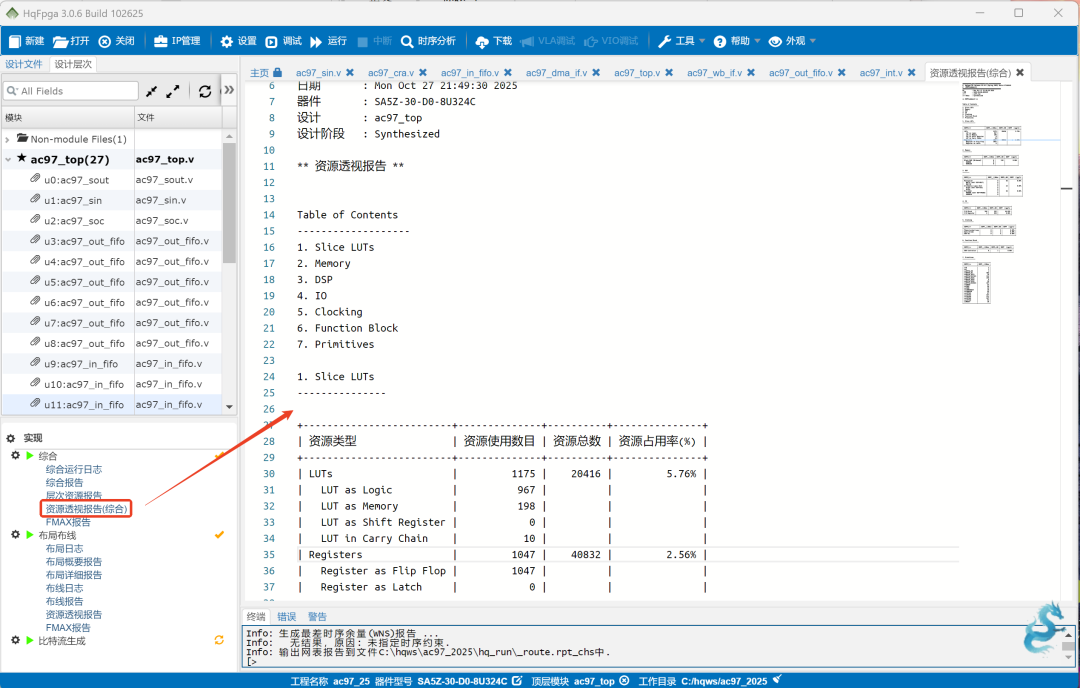

HQ2025新增資源透視報告,該報告功能旨在報告FPGA中被使用的可配置資源在應用中的底層配置結構信息,便于用戶分析設計實現。比如FPGA上的Register既可以配置為Flip-Flop,也可以配置為Latch,如果在舊版本上,只有資源報告,是看不出具體Register實現的配置邏輯;在新版上,可以看到各種配置和各自的數量。如下圖中,看到Register資源共使用1047個,其中配置為Flip-Flop共1047個,Latch為0個。

2.2.2層次資源報告分析器

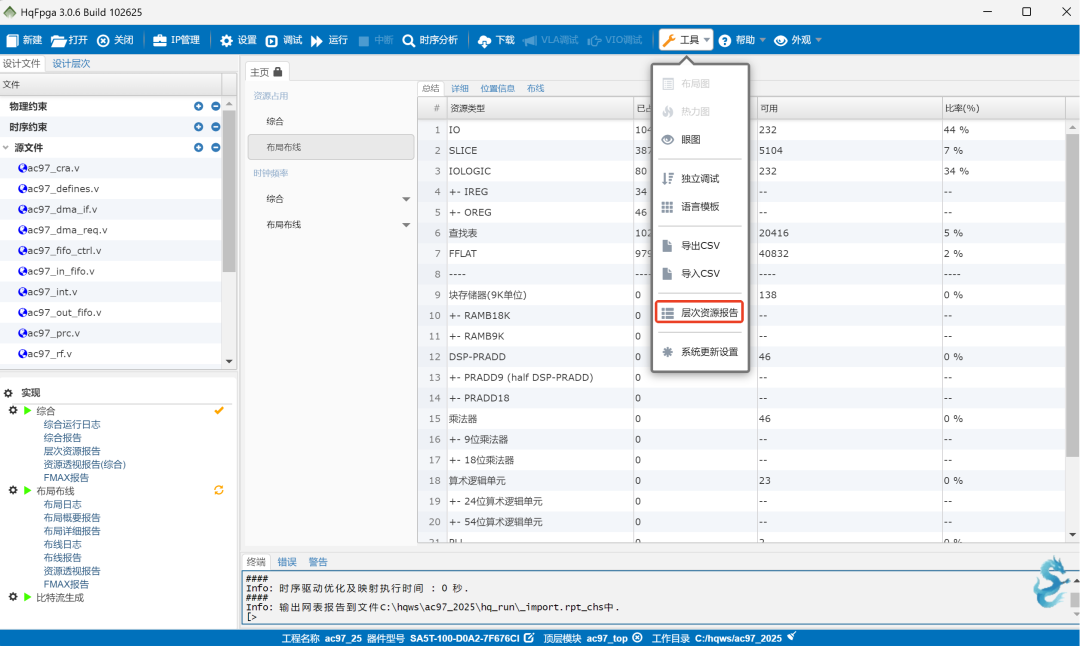

HQ2025新增層次資源報告分析器,內嵌到HQ套件主界面的【工具】-【層次資源報告】,如下圖。

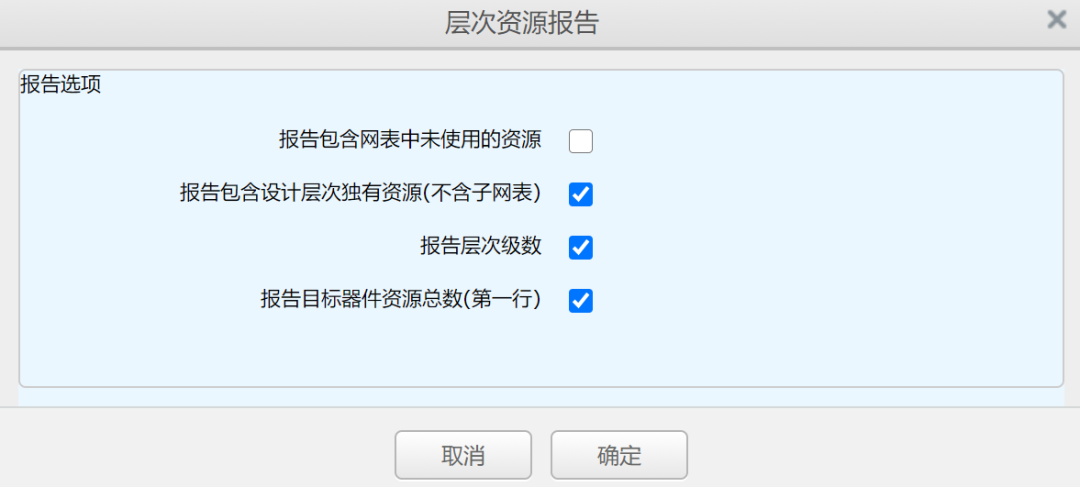

該功能可以按照用戶的定制選項輸出源設計綜合結果中的層次資源統計信息。單擊【層次資源報告】打開定制選項的對話框,如下圖,可以定制選擇:報告包含網表中未使用的資源、報告包含設計層次獨有資源(不含子網表)、報告層次級數、報告目標器件資源總數(第一行),輸出配置的層次資源信息。

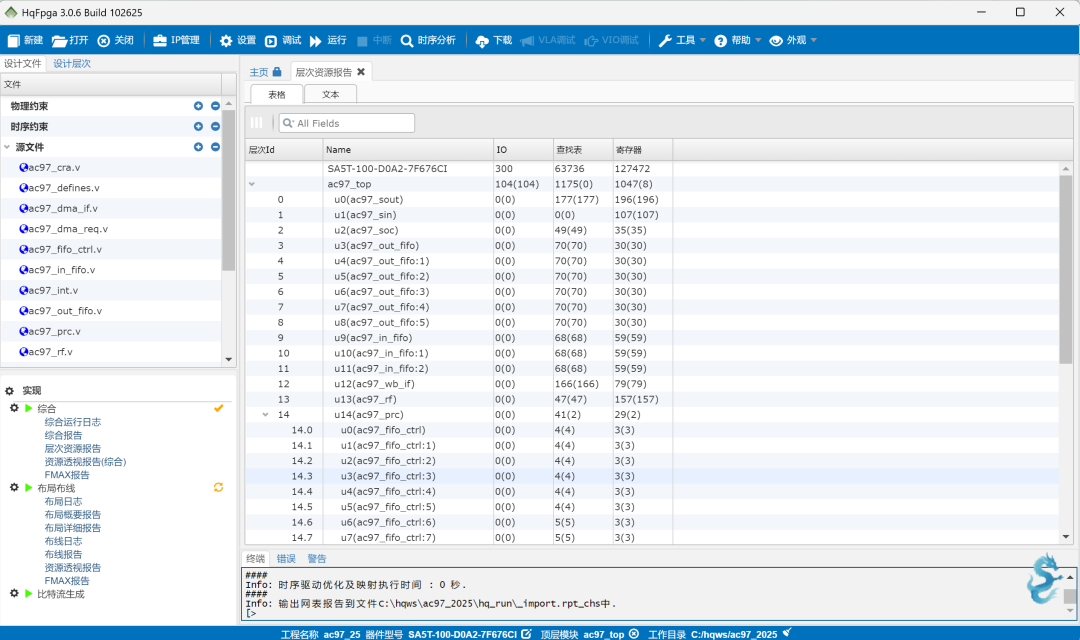

按照上圖的配置,打開定制的層次資源報告,該報告信息有兩種形式:表格、文本。具體如下圖的圖示。

2.3 IDE(集成設計管理)

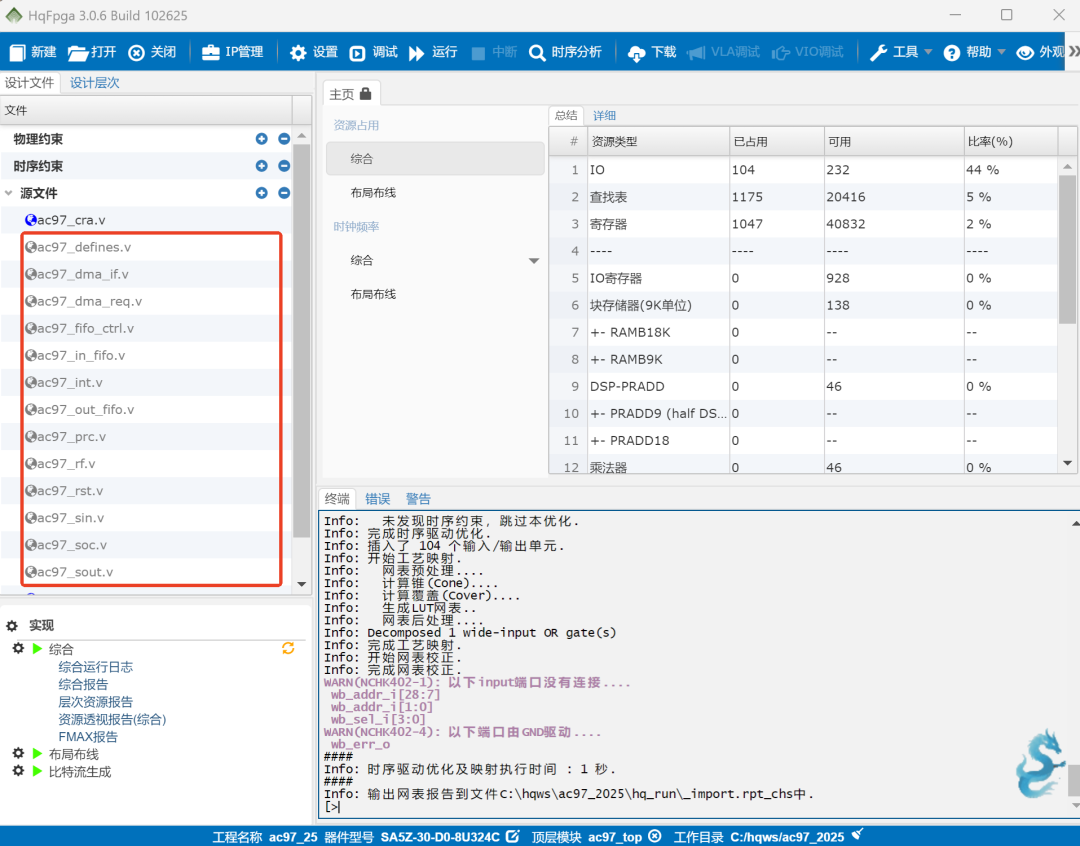

2.3.1 源文件啟用/禁用

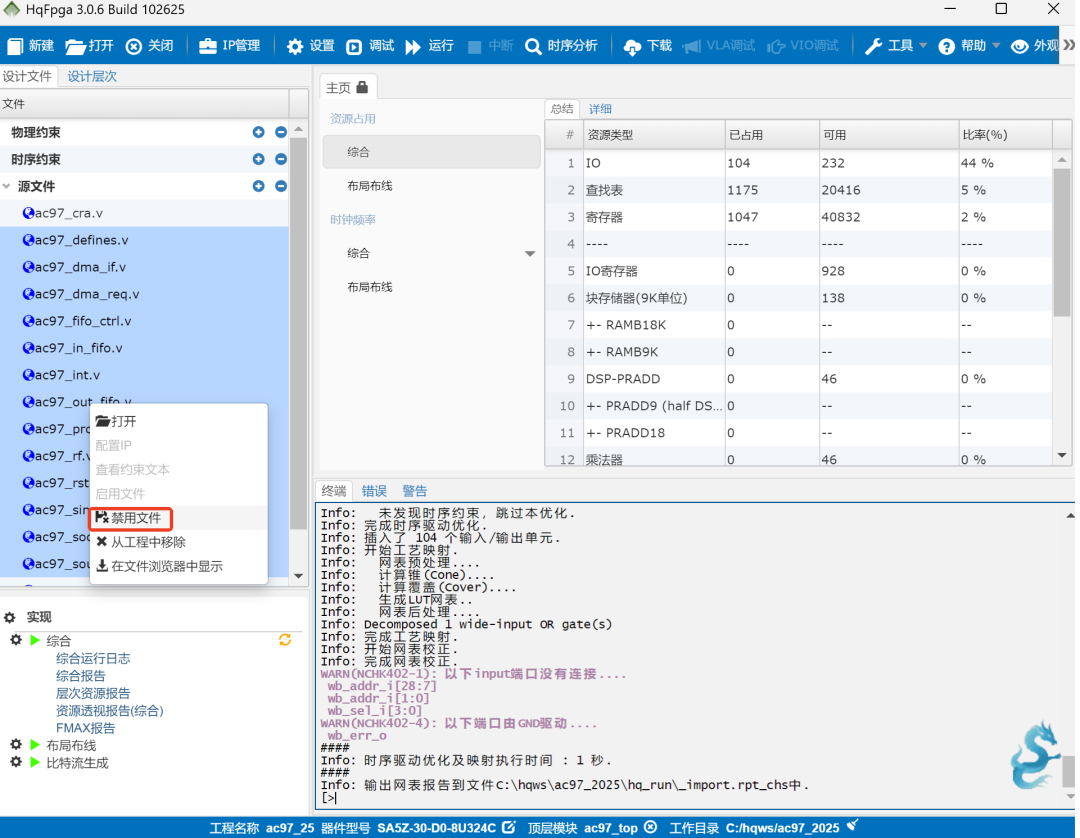

HQ2025新增源文件的啟用/禁用功能,方便用戶可以自由啟用和禁用當前工程的設計,進行所需的編譯和設計。該功能支持單文件,也支持多文件的啟用和禁用。如下面的左圖,選中【設計文件】區的多個文件,右鍵彈出菜單,選擇【禁用文件】,被禁用的文件如下面的右圖灰色顯示,不參與工程的編譯、運行和調試等。

如下面的左圖,選中【設計文件】區的多個禁用文件,右鍵彈出菜單,選擇【啟用文件】,被禁用的文件再次恢復原來的正常被使用狀態,如下面右圖。

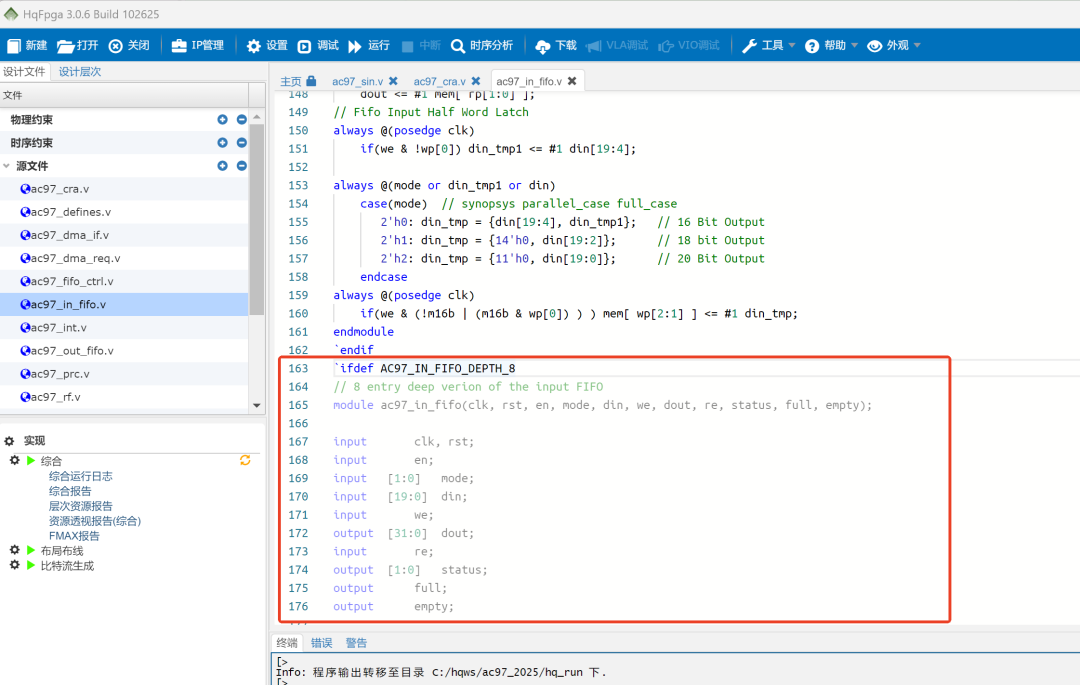

2.3.2編輯器ifdef差異化顯示

HQ2025的編輯器新增ifdef差異化顯示,對于條件為false的ifdef條件預編譯語句部分實現灰色顯示,即在當前設計中,灰色部分源碼不起作用,如下圖所示,AC97_IN_FIFO_DEPTH_8沒有define聲明,所以”`ifdef AC97_IN_FIFO_DEPTH_8”條件控制的部分是無效的,在編輯區的顯示為灰色。

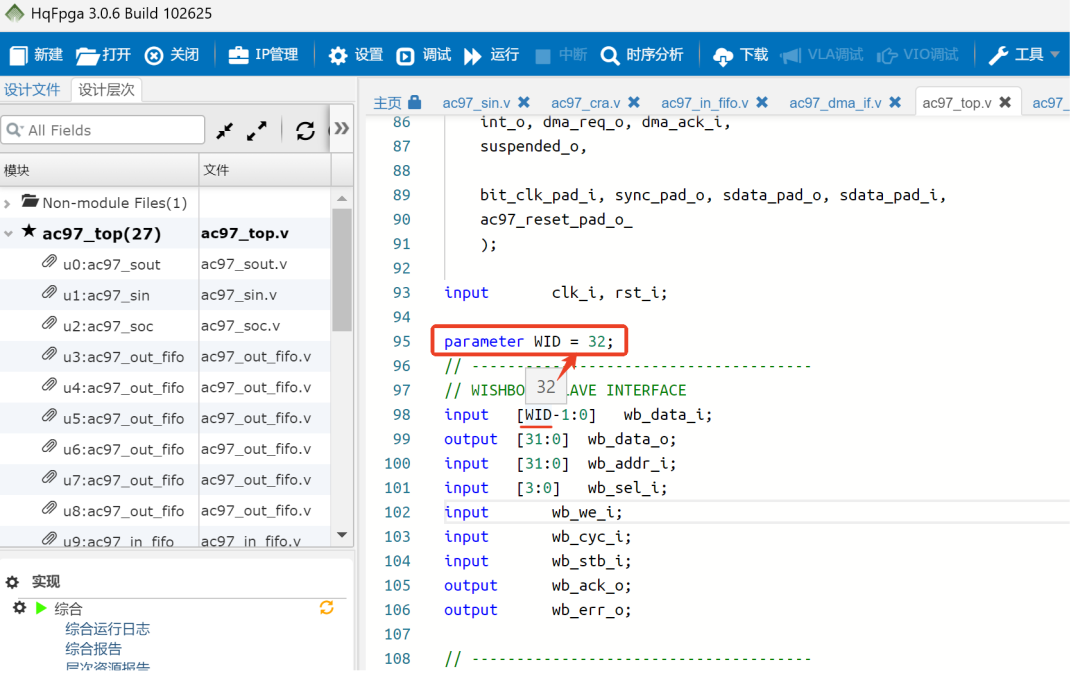

2.3.3編輯器參數值顯示

HQ2025的編輯器新增參數值顯示,對于宏參、parameter,鼠標放在參數名上,可以顯示值。如下圖示,定義了參數WID為32,當鼠標放在第98行的WID上,顯示出32。

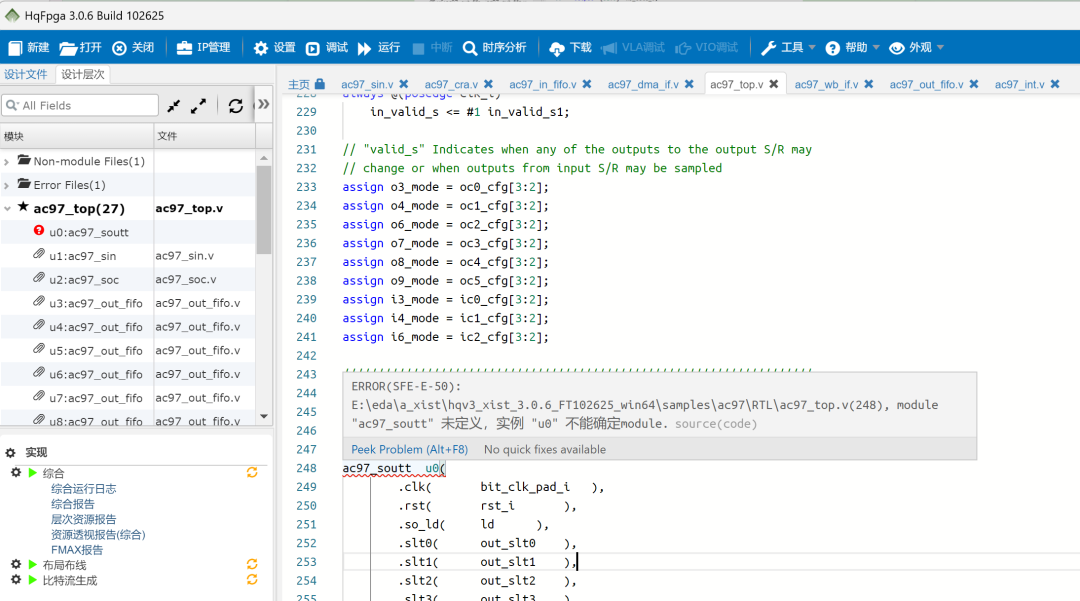

2.3.4 編輯器顯示源碼編譯錯誤信息

HQ2025的編輯器新增源碼編譯錯誤的信息顯示,如存在編譯錯誤,錯誤語句會有紅色波紋線提示,鼠標放在改語句上,會顯示出錯誤信息,同時存在錯誤的文件會在設計層次中以“紅色小問號”顯示出來,如下圖,ac97_soutt module沒有定義,例化語句存在語法錯誤,對應的錯誤信息,直觀的在錯誤語句上方顯示出來。

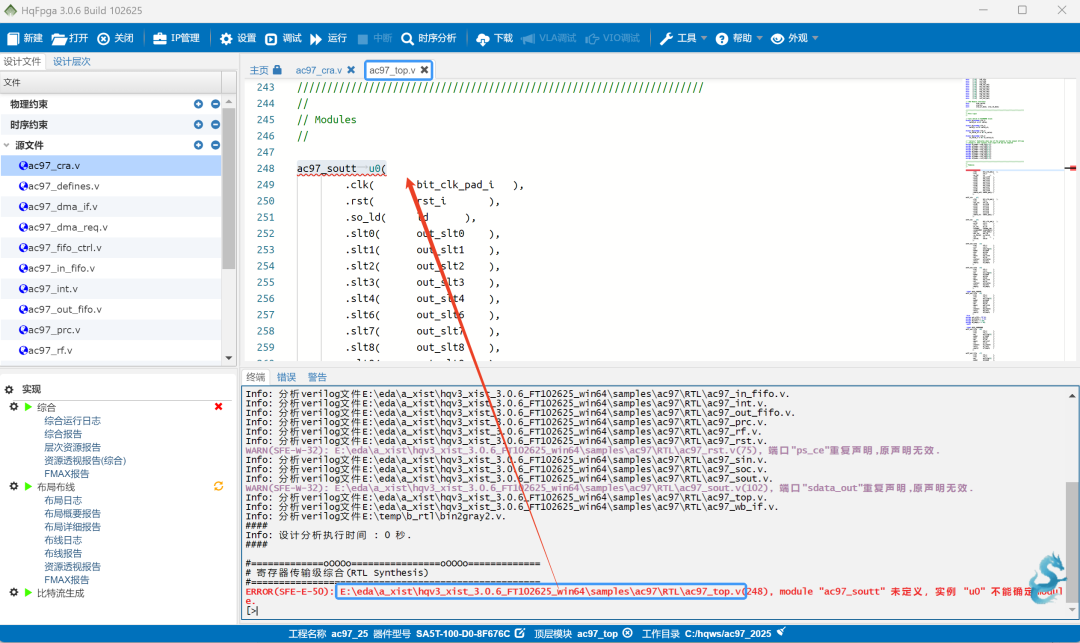

2.3.5 終端窗口輸出信息中文件超鏈接

HQ2025升級了終端文件識別,即識別出輸出信息中的文件并顯示超鏈接。如下圖中,終端窗口輸出的ERROR信息中包含了文件路徑信息:E:edaa_xisthqv3_xist_3.0.6_FT102625_win64samplesac97RTLac97_top.v(248),即文件的路徑和錯誤位置,雙擊這個路徑這一行,對應的錯誤文件ac97_top.v會在編輯區被打開,并且顯示出錯誤的位置,如下圖。

3、 眼圖(XSBERT-EYE-CHART)

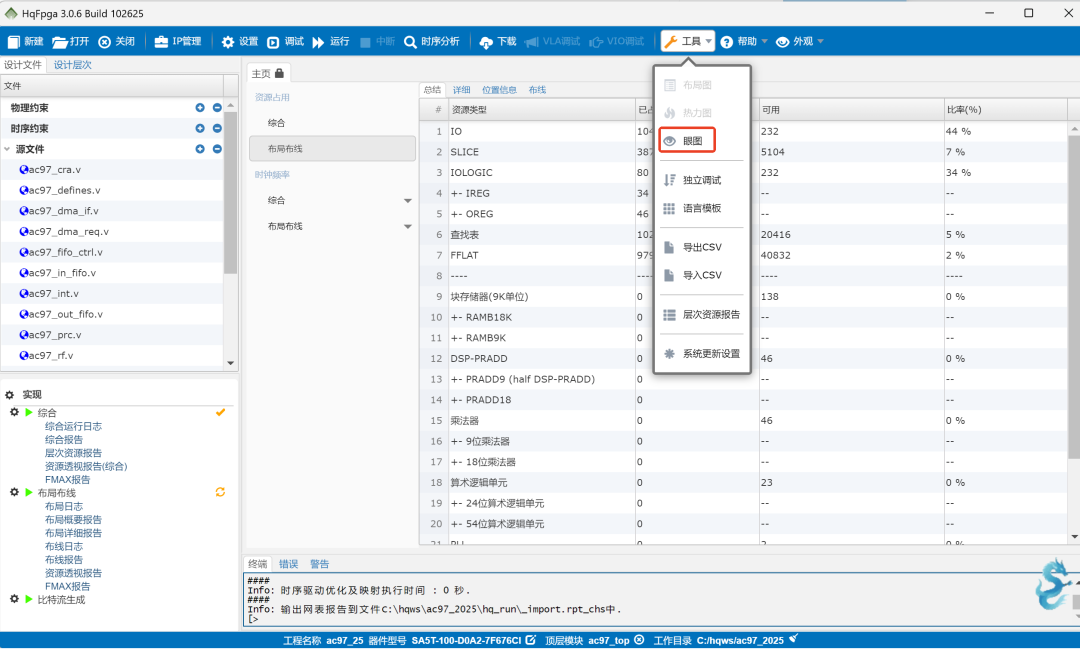

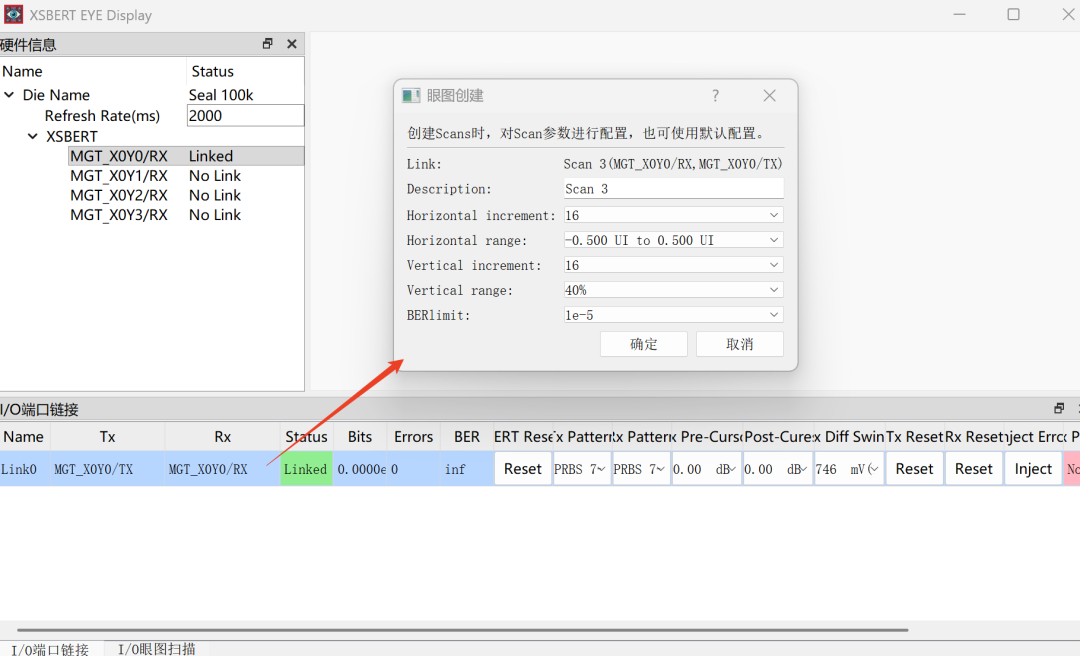

XSBERT(XiST Bit Error Ratio Test)是一種集成的測試工具,用于驗證和測試FPGA中的高速串行接口,如SERDES(串行解串器)。它能夠生成數據并進行誤碼率(BER)測試,提供鏈路性能的實時監控和診斷,幫助設計人員評估和優化串行接口的可靠性。通過使用XSBERT,用戶可以檢測信號質量問題、進行鏈路調試,并確保數據傳輸的穩定性,從而優化FPGA設計的整體性能。眼圖已內嵌到HQ套件主界面的【工具】-【眼圖】,如下圖。

眼圖分三個區

左上為芯片、鏈接信息界面,顯示器件信息及鏈接狀態,也可以設定鏈接狀態刷新時間。

下部為 I/O Links 與 I/O Scans 兩個頁面,用于顯示狀態和調整參數。

右上為眼圖顯示及信息總結界面。可以使用鼠標左鍵拖動顏色條(Color Bar),調節顯示效果。

使用示例

在 XSBERT bin/bit 文件下載完成后,點擊上圖中的【眼圖】,打開眼圖;點擊區1、2,選擇所需的 Tx 和 Rx創建鏈接,可以添加多組鏈接;點擊區2的I/O Links 窗口中,想要觀察眼圖的鏈接的【Name】欄,右鍵創建掃描,選擇所需掃描配置,點擊【ok】生成眼圖,如下圖左圖。眼圖生成后的效果如下圖圖右。

4 、調試器

4.1 支持調試器多LA

HQ2025調試器支持更多LA(Logic Analyzer,邏輯分析儀), 每個LA相當于一臺邏輯分析儀,最大支持16臺。

相較于之前單LA,只能選擇觀察一組信號。如果故障是由模塊間的復雜交互引起的,單次捕獲很難捕捉到全貌。多LA則允許開發者同時、獨立地捕獲和觸發多組不相關或弱相關的信號序列,從而高效地解耦和定位復雜系統中分散的、有依賴關系的故障。特別適用于復雜SoC、多核系統、高速互聯以及任何包含多個異步或并發進程的設計,是提高調試效率和解決復雜問題的強大武器。具體特性對比如下表。

可以在下圖的界面上點擊紅框加號增加。

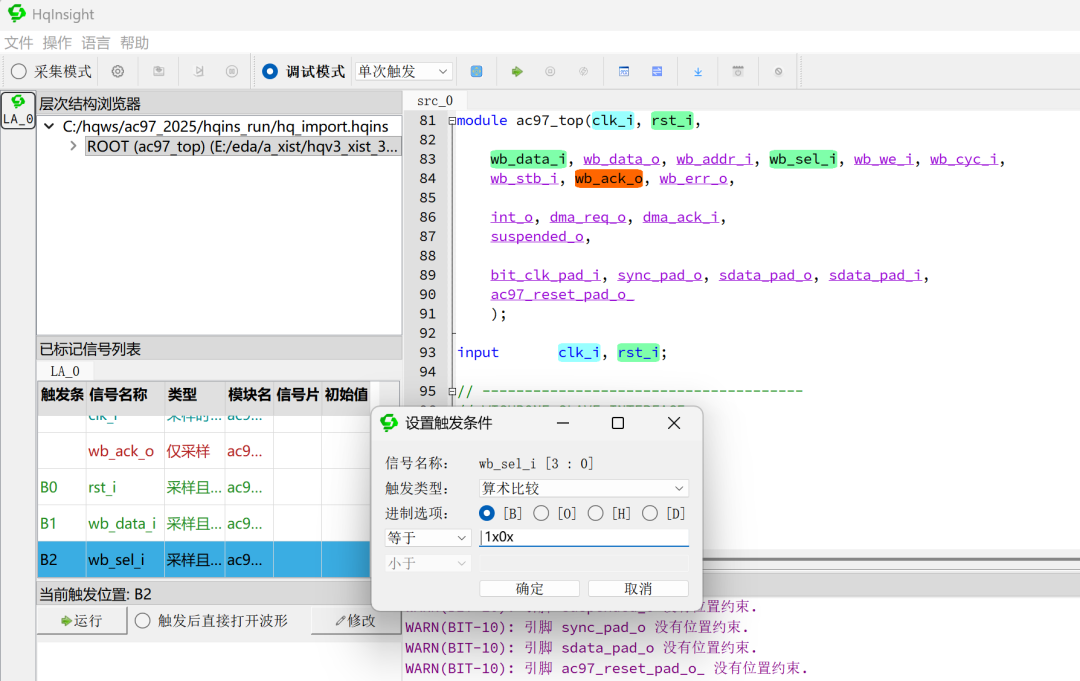

4.2 調試器觸發方式支持X值

HQ2025調試器新增觸發方式的X值,X值是don’t care(任意狀態),如a=4'bxx11,不關心高兩位([3:2],可以是00/01/10/11),只要低兩位[1:0]是11就觸發,該功能的主要用途用于解決未初始化寄存器、多驅動沖突、接口協議違規等深層設計問題。使用方式如下圖。

4.3其它

改進EDIF網表調試支持,例如采用VLA IP調試。

支持高速下載器。

提升易用性及穩定性,例如支持信號設置保存、啟用與禁用等。

5、 IP Creator

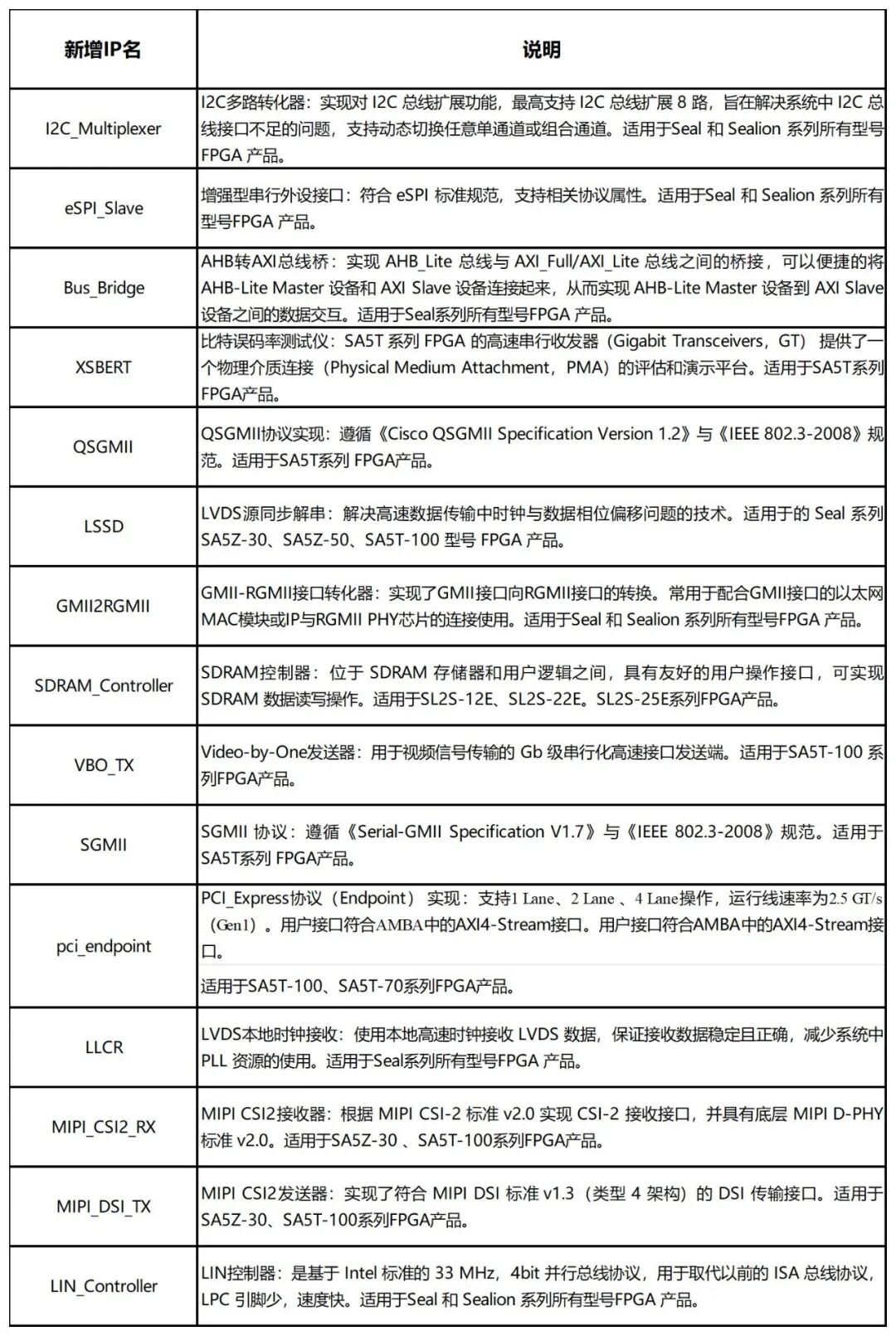

5.1豐富了IP品類

HQ2025的IP Creator新增較多品類的IP,方便項目高效開發。

* 具體詳情請見每個IP配置界面打開用戶手冊。

此外,對多個IP做了升級,如FIR_Filter,SerDes、DDRC, PLL,EBR、FIFO_Generator等。

5.2 改進IP Creator平臺的易用性和穩定性

例如增強異常處理。

HDL型IP生成flow可配置。

基于器件的配置。

增加浮點數range顯示等。

6 、軟件優化

HQ2025軟件(綜合~布局布線~下載)支持了更多的器件,如SA5T-70/SA5T-200/SA5T-420等,并做了多方面優化,功能、性能、魯棒性都得到了提升。

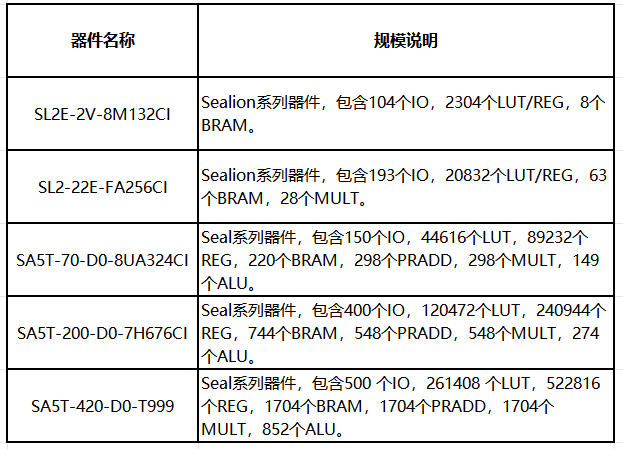

6.1新增器件的支持

HQ2025新增了多款器件的支持,如下表:

6.2綜合

FSM優化:改進識別支持更多描述方式的FSM、支持更多編碼方式等。

改進移位寄存器識別與映射,支持動態移位。

RAM/ROM推斷與映射改進:完整支持了memory OUTREG結構、地址寄存器結構、包含RESET控制的結構;支持了有選擇器鏈的BE-RAM;改進了可變字節寬度的BE-RAM支持。

支持跨層次資源合并,減少資源的消耗。

增強原語例化優化(例如不同IP網表中相同進位鏈合并)。

增強LUT合并功能。

總體資源占用率降低~5%,運行時間減少約10%。

6.3布局

改進Seal系列產品布局優化,時序性能提升~3%。

增強Packing,減少資源占用率約1%,減少運行時間~30%。

增加了DRC檢查,不僅檢查物理約束,而且檢查設計中的連接關系,幫助工程師方便快捷定位約束問題。

新增解析式布局算法,提高運行速度,較之前版本提升10%。

完整支持IO缺省狀態及IO統計等功能,IO是器件與外部交互的唯一接口。以前IO的缺省狀態交給硬件來控制,軟件沒有干預,導致客戶應用中有風險,而且很難排查。完整支持后,每一種器件的IO都有確定的狀態,既避免了應用中的風險,而且方便問題調試與排查。

6.4布線

提升seal系列產品布線的時序性能約5%,減少運行時間約30%。

內存使用比之前版本減少約25%。

更全面的進展,歡迎您試用最新發布版本,更歡迎您提出寶貴意見和建議。

-

FPGA

+關注

關注

1661文章

22440瀏覽量

637369 -

eda

+關注

關注

72文章

3117瀏覽量

183255 -

調試

+關注

關注

7文章

650瀏覽量

35770

原文標題:“芯”技術分享 | 2025年HqFpga軟件中的進展說明

文章出處:【微信號:智多晶,微信公眾號:智多晶】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

國產智多晶FPGA介紹及應用

國產FPGA智多晶叼

EDA Tools in FPGA

基于多種EDA工具的FPGA設計

光纖激光器市場前景廣闊,有望在傳感和醫療領域取得重大進展

eda工具軟件有哪些 EDA工具有什么優勢

智多晶FPGA設計工具HqFpga接入DeepSeek大模型

智多晶重磅發布HQPEP功耗評估工具

智多晶EDA工具HqFpga軟件的主要重大進展

智多晶EDA工具HqFpga軟件的主要重大進展

評論