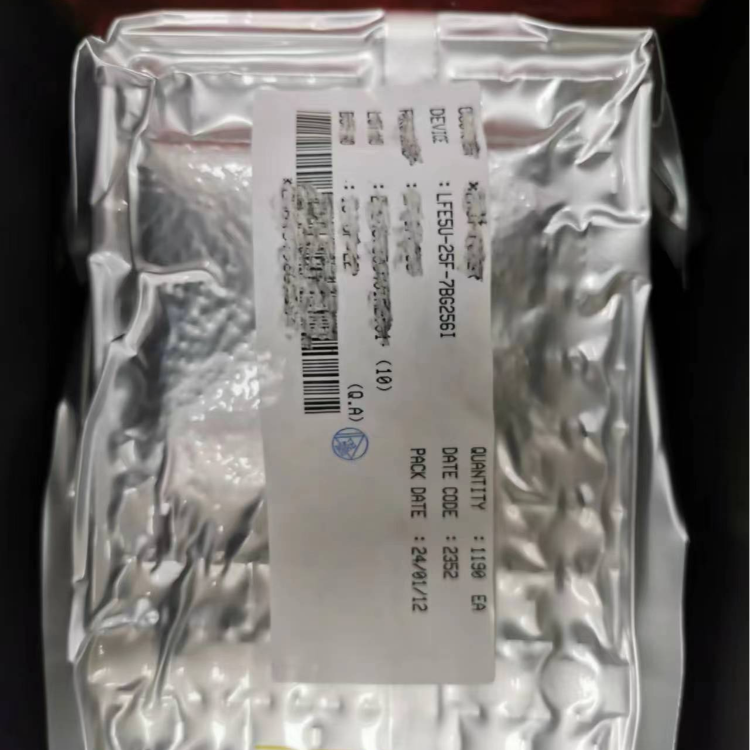

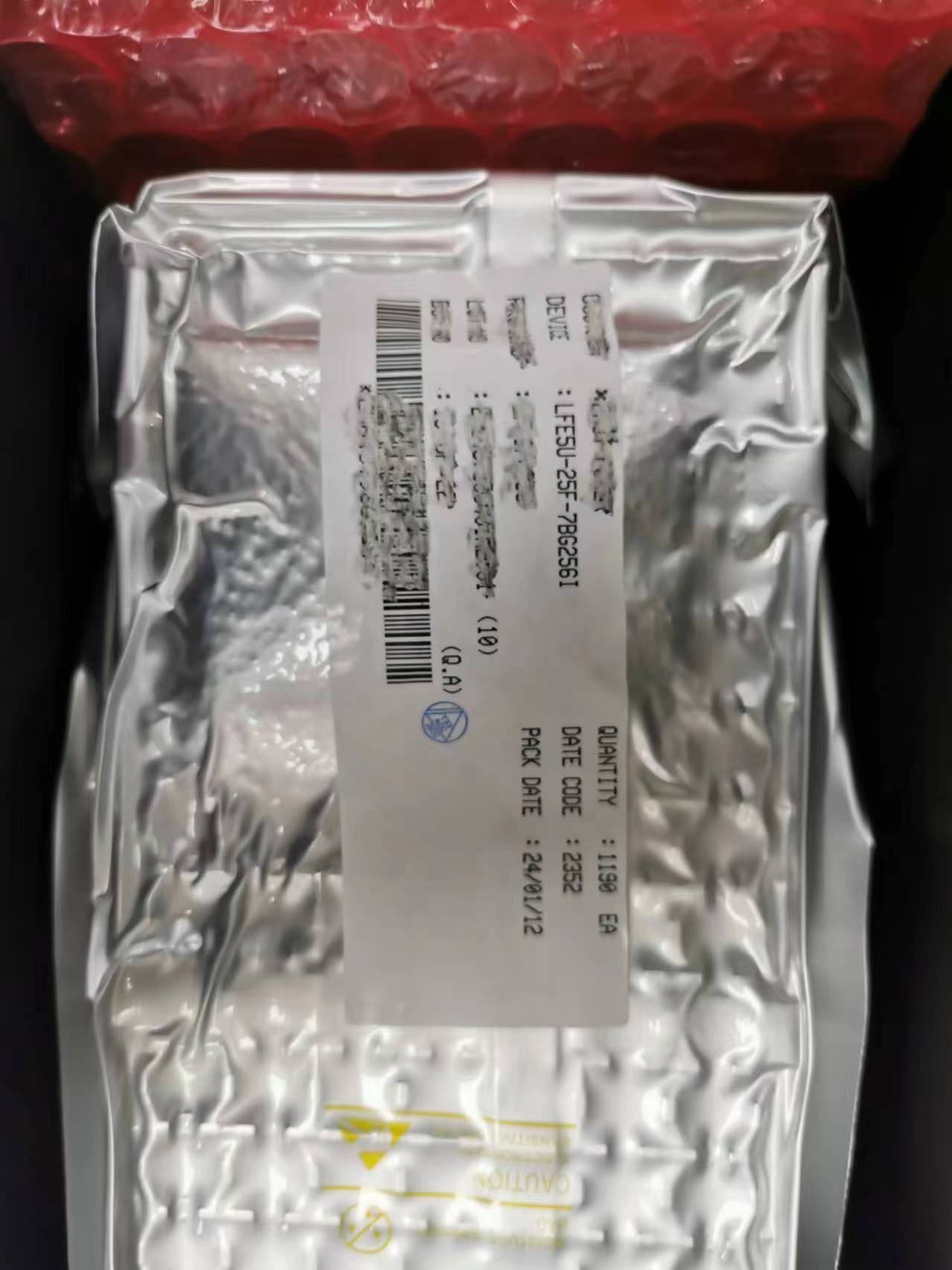

LFE5U-25F-7BG256I,LATTICE(萊迪思),FPGA器件

LFE5U-25F-7BG256I,LATTICE(萊迪思),危芯練戲:依叭溜溜寺山寺依武叭武

ECP5?/EP5-5G?系列FPGA器件經過優化,可在經濟的FPGA結構中提供高性能功能,如增強型DSP架構、高速SerDes(串行器/解串器)和高速源同步接口。這種組合是通過設備架構的進步和40nm技術的使用實現的,使設備適用于高容量、高速和低成本的應用。

ECP5/ECP5-5G設備系列可提供多達84k個邏輯元件的查找表(LUT)容量,并支持多達365個用戶I/O。ECP5/ECP-5G設備系列還提供多達156個18×18乘法器和廣泛的并行I/O標準。

ECP5/ECP5-5G FPGA結構優化了高性能,同時考慮到了低功耗和低成本。ECP5/ECP5-5G設備利用可重新配置的SRAM邏輯技術,并提供流行的構建塊,如基于LUT的邏輯、分布式和嵌入式存儲器、鎖相環(PLL)、延遲鎖定環(DLL)、預先設計的源同步I/O支持、增強的sysDSP片和高級配置支持,包括加密和雙引導功能。

ECP5/ECP5-5G設備系列中實現的預設計源同步邏輯支持廣泛的接口標準,包括DDR2/3、LPDDR2/3、XGMII和7:1 LVDS。

ECP5/ECP5-5G設備系列還具有具有專用物理編碼子層(PCS)功能的高速SerDes。高抖動容限和低傳輸抖動使SerDes加PCS塊能夠配置為支持一系列流行的數據協議,包括PCI Express?、以太網(XAUI、GbE和SGMII)和CPRI。具有前光標和后光標的傳輸去加重以及接收均衡設置使SerDes適合在各種形式的介質上進行傳輸和接收。

ECP5/ECP5-5G設備還提供靈活、可靠和安全的配置選項,如雙引導功能、比特流加密和TransFR現場升級功能。

與ECP5UM設備相比,ECP5-5G系列設備在SerDes中進行了一些增強。這些增強功能將SerDes的性能提高到最高5 Gb/s的數據速率。

ECP5-5G系列設備與ECP5UM設備引腳對引腳兼容。這為用戶提供了從ECP5UM到ECP5-5G設備的端口設計遷移路徑,以獲得更高的性能。

Lattice Diamond?設計軟件允許使用ECP5/ECP5-5G FPGA系列高效實現大型復雜設計。ECP5/ECP5-5G設備的綜合庫支持可用于流行的邏輯綜合工具。Diamond工具使用合成工具輸出及其樓層規劃工具的約束條件,將設計放置在ECP5/ECP5-5G設備中并進行布線。這些工具從布線中提取時序,并將其反向注釋到設計中,以進行時序驗證。

萊迪思為ECP5/ECP5-5G系列提供了許多預制IP(知識產權)模塊。通過使用這些可配置的軟核IP作為標準塊,設計師可以自由地專注于其設計的獨特方面,從而提高他們的生產力。

1.1. 特征

?更高的邏輯密度可提高系統集成度

?12k至84k LUT

?197到365個用戶可編程I/O

?嵌入式SerDes

?270 Mb/s,最高3.2 Gb/s,SerDes接口(ECP5)

?270 Mb/s,最高5.0 Gb/s,SerDes接口(ECP5-5G)

?支持RDR(1.62 Gb/s)和HDR中的eDP

(2.7 Gb/s)

?每個設備最多四個通道:PCI Express、以太網(1GbE、SGMII、XAUI)和CPRI

?sysDSP?

?完全級聯的切片架構

?12到160個切片實現高性能乘法和累加

?強大的54位ALU操作

?時分復用MAC共享

?舍入和截斷

?每個切片支持

?一半36×36,兩個18×18或四個9×9乘法器

?高級18×36 MAC和18×18乘法-乘法-累加(MMAC)操作

?靈活的內存資源

?高達3.744 Mb sysMEM?嵌入式塊RAM(EBR)

?194k至669k位分布式RAM

?sysCLOCK模擬PLL和DLL

?LFE5-45和LFE5-85中的四個DLL和四個PLL;LFE5-25和LFE5-12中的兩個DLL和兩個PLL

?預先設計的源同步I/O

?I/O單元中的DDR寄存器

?專用讀/寫調平功能

?專用傳動邏輯

?源同步標準支持

?ADC/DAC,7:1 LVDS,XGMII

?高速ADC/DAC設備

?專用DDR2/DDR3和LPDDR2/LPDDR3內存支持DQS邏輯,數據速率高達800 Mb/s

?可編程sysI/O?緩沖器支持廣泛的接口

?片上終端

?LVTTL和LVCMOS 33/25/18/15/12

?SSTL 18/15 I,II

?HSUL12

?LVDS、總線LVDS、LVPECL、RSDS、MLVDS

?subLVDS和SLVS,SoftIP MIPI D-PHY接收機/發射機接口

?靈活的設備配置

?用于配置I/O的共享庫

?SPI引導閃存接口

?支持雙啟動映像

?從SPI

?用于簡單字段更新的TransFR?I/O

?單一事件中斷(SEU)緩解支持

?軟錯誤檢測-嵌入式硬宏

?軟糾錯-不停止用戶操作

?軟錯誤注入–模擬SEU事件以調試系統錯誤處理

?系統級支持

?符合IEEE 1149.1和IEEE 1532

?Reveal Logic Analyzer

?用于初始化和一般用途的片上振蕩器

?ECP5的V核心電源,ECP5UM5G的1.2 V核心電源