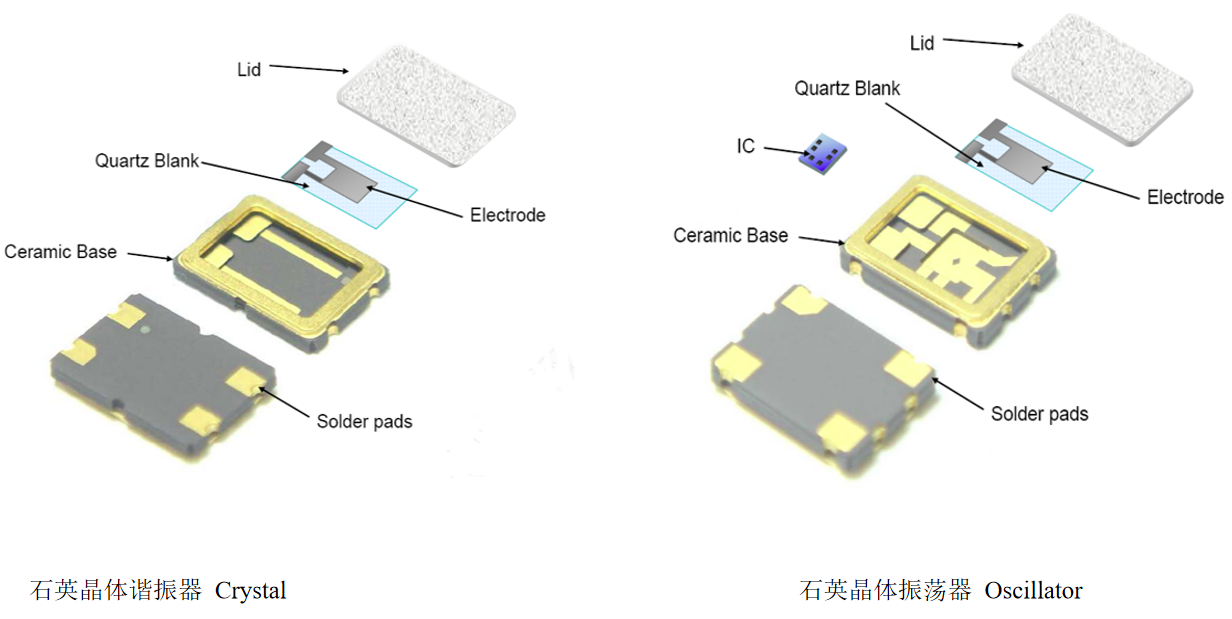

在現代高性能數字系統中,FPGA(現場可編程門陣列)憑借其并行處理能力和硬件可編程特性,成為通信、工業控制和數據中心等領域的核心處理器。FPGA主時鐘作為同步所有邏輯操作的"心臟",其信號質量直接決定系統性能、時序收斂性和數據可靠性。主流方案中,時鐘源需滿足納秒級抖動、百萬分之一(ppm)級頻率穩定性和嚴苛環境適應性。傳統無源晶體結合外部振蕩電路的設計存在明顯瓶頸:啟動延遲高、相位噪聲易受PCB布局影響,且溫度漂移可能導致時序違規。而有源晶振(Oscillator)通過集成石英晶體、振蕩電路和輸出驅動器于單一封裝,提供即用型時鐘信號,徹底規避外部匹配偏差。

在100MHz至156.25MHz頻段,有源晶振成為FPGA主時鐘的黃金選擇——該范圍覆蓋了從基礎邏輯同步到高速接口協議的全場景需求。以156.25MHz為例,其對應10G以太網和SFP+光模塊的精確時鐘基準,每1ppm頻率偏差可能導致萬兆鏈路每秒數比特誤碼。NDK日本電波的超穩定有源晶振通過三項技術突破賦能FPGA設計:其一,納米級溫度補償,采用雙集成電路架構實時校正溫度-頻率曲線,在-40℃~85℃范圍內將穩定性控制在±20ppm內,避免工業設備因溫升引發的時鐘漂移;其二,多協議自適應輸出,單芯片支持LVDS/HCSL雙模式切換,適配Xilinx UltraScale+或Intel Stratix 10等主流FPGA的差分時鐘輸入要求,減少外部電平轉換器;其三,抗振動結構設計,通過陶瓷基板與金屬蓋板復合封裝,抵抗50G機械沖擊,確保車載或無人機平臺在震動環境下仍維持 femtosecond 級抖動。實際測試中,156.25MHz有源晶振驅動FPGA收發器(GTX)時,其相位噪聲在100kHz偏移處低至-150dBc/Hz,使28Gbps串行鏈路誤碼率(BER)優于10?12。

NDK日本電波(Nihon Dempa Kogyo)作為全球頻率控制元件領導者,其NP3225SAD系列有源晶振以車規級可靠性重塑FPGA主時鐘標準。該產品采用3225緊湊封裝(3.2mm×2.5mm),頻率覆蓋100~156.25MHz,核心參數對比凸顯其差異化優勢:

參數 | ?NP3225SAD | 工業級競品典型值 | ?優勢 |

頻率穩定性 | ±20ppm (-40℃~85℃) | ±25ppm ~ ±50ppm | 時序裕量提升60% |

相位噪聲(@156.25MHz) | -150dBc/Hz (100kHz) | -140dBc/Hz | 高速串行鏈路BER降低10倍 |

電源電壓 | 1.8V/2.5V/3.3V可編程 | 3.3V固定 | 功耗降低40% |

啟動時間 | 2ms | 5ms ~ 10ms | 系統響應速度提升3倍 |

振動可靠性 | 50G(MIL-STD-883H) | 20G | 抗沖擊能力增強150% |

該器件內置多階溫度傳感網絡,通過數字算法實時補償晶體頻偏,使-55℃冷啟動仍保持±0.1ppm瞬時精度;其鍍金電極與氮化硅鈍化層結構確保10億小時平均無故障時間(MTBF),遠超FPGA設備生命周期需求。在FPGA主時鐘應用中,NP3225SAD承擔三大關鍵任務:一是參考時鐘生成,為PCIe Gen4/5、JESD204B/C接口提供低抖動源,使256位總線同步誤差<200fs;二是時鐘樹驅動,通過Fanout Buffer分發多路同相時鐘,消除多FPGA系統的偏斜問題;三是動態頻率切換,支持I2C接口實時調整輸出頻率(步進1Hz),滿足AI計算負載的動態調頻需求。

滿度科技作為NDK日本電波官方授權代理,為FPGA開發者提供全周期技術支持:基于Xilinx Vivado或Intel Quartus平臺定制時鐘樹分析報告,48小時交付《FPGA-晶振時序協同設計指南》;免費樣品支持-55℃~125℃三溫測試及TIA-455-222振動驗證;量產階段提供焊接曲線優化與信號完整性仿真,縮短研發周期40%。

在邊緣計算向200G互聯演進的時代,NDK NP3225SAD以"原子級精度、軍工級堅韌、生態級智能"三重優勢,成為FPGA主時鐘的終極解決方案。其全自主產業鏈相較美國競品價格低20%,交期穩定至6周,規避地緣供應鏈風險。滿度科技的本土服務網絡進一步降低集成門檻——失效分析實驗室可精準定位電源噪聲引發的抖動超標,高速數字團隊提供眼圖測試與端接優化,為每一片FPGA注入"零抖動時鐘、零誤差同步、零風險升級"的基因。當Chiplet技術要求多芯粒納秒級同步,當802.3dj以太網需突破200Gbps——選擇NDK,即是選擇以"時序確定性"定義數字世界的未來十年。

-

FPGA

+關注

關注

1661文章

22440瀏覽量

637404 -

有源晶振

+關注

關注

1文章

1003瀏覽量

22889 -

NDK

+關注

關注

0文章

20瀏覽量

15838

發布評論請先 登錄

NDK有源晶振與FPGA的協同設計

NDK有源晶振與FPGA的協同設計

評論