光伏設備“單一功能、適配性差”的局限,以“計算為核、通信為脈、可靠為基”構建架構體系。西格電力提供光伏策略控制服務器,了解詳情可咨詢:1.3.7-5.0.0.4-6.2.0.0。本文從計算單元的算力配置、通信接口的鏈路設計、可靠性的全場景防護三個維度,詳解光伏四可裝置硬件平臺的架構邏輯與實現路徑。

2026-01-04 15:40:14 830

830

一文詳解SN65HVD888:RS-485總線通信的得力助手 作為電子工程師,我們在設計工業通信系統時,常常會與RS - 485總線打交道。RS - 485憑借其長距離、高抗干擾能力等優點,在工業

2025-12-23 11:15:02 186

186 丹東的海水浴場是當地濱海文旅的金字招牌,但此前水質監測依賴定期抽檢,數據滯后不僅難以及時響應突發水質波動,也讓游客對浴場安全心存顧慮;而周邊海水養殖尾水的潛在影響,更讓浴場水質管護添了一層壓力。凱米

2025-12-19 17:48:58 160

160

一文帶你搞清楚藍牙 UUID ...... 矜辰所致

2025-12-18 11:23:35 3117

3117

和反序列化操作。

方便在本地儲存設備(如flash、eeprom等)保存/讀取二進制數據,甚至還可以跨設備傳輸使用

提供了兩種方式:

第一種:只需要提供參數數據保存/加載的回調函數,調用相關接口函數

2025-12-16 06:24:31

探索AMD XILINX Versal Prime Series VMK180評估套件,開啟硬件創新之旅 在電子設計的領域中,快速實現原型設計并確保高性能是每一位工程師的追求。AMD XILINX

2025-12-15 14:40:02 229

229 干擾其他設備易引發信道爭搶、上網卡頓。

傳統屏蔽箱吞吐量測試雖能反映實際體驗,但批量生產場景中存在效率低、占地廣的問題。RF功率耦合測試方案可實現1拖16批量測試,既保證射頻參數的真實性,又能高效完成產

2025-12-01 10:40:40

近日,迪文自主研發的多款自動化設備順利通過產線試運行壓力測試,即將正式投入使用。此次測試通過的設備包含液晶屏自動檢測、絲印機械手、掛扣組裝、背膠貼敷、工程燒錄及校準等等,覆蓋智能屏生產的多個工序,為

2025-11-22 09:25:41 800

800

UART 硬件 FIFO 深度是多少?如何避免數據溢出?

2025-11-21 06:59:21

Xilinx FPGA因其高性能和低延遲,常用于串行通信接口設計。本文深入分析了Aurora、PCI Express和Serial RapidIO這三種在Xilinx系統設計中關鍵的串行通信協議。介紹了它們的特性、優勢和應用場景,以及如何在不同需求下選擇合適的協議。

2025-11-14 15:02:11 2357

2357

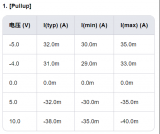

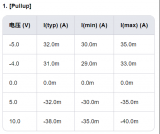

摘要隨著SiC、GaN等新型功率器件的廣泛應用,功率器件動態參數測試對系統響應速度、同步精度和靈活性提出了更高要求。本文基于LiquidInstruments的Moku平臺,提出一種可重構、高集成度

2025-10-31 14:09:44 324

324

近日,福州移動與華為聯合推出國內首個端到端智能化體驗經營系統,通過多智能管理系統協同,實現場景化體驗套餐的可預估、可保障、可保護、可評估,分層分級保障用戶在熱門景區、大型演唱會和體育賽事的流暢

2025-10-24 09:46:06 398

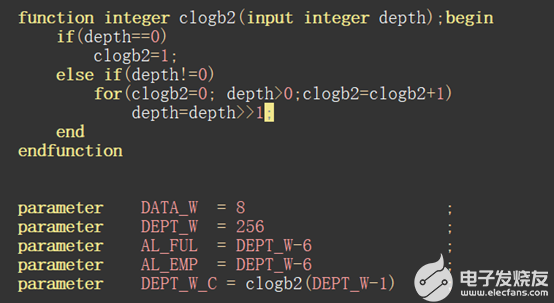

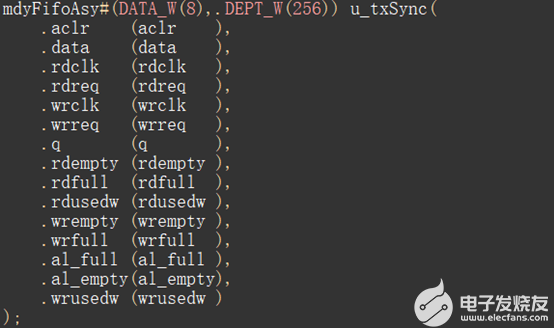

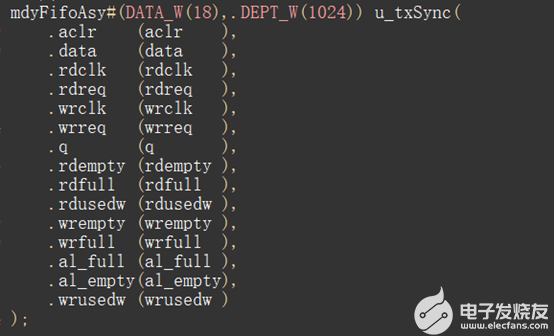

398 width代表數據位寬,depth代表數據個數

操作模式建議選擇寫優先,一般只有使用coe初始化后不再寫BRAM,才使用讀優先

RAM內存空間的初始化可以通過裝載.coe文件,格式如下

2025-10-24 06:10:15

種集成了多種傳感功能的一體化監測方案,它旨在為水文環境監測提供一種更緊湊、更高效的硬件解決思路。一、核心突破:多參數一體化硬件集成這款由金葉儀器推出的水文自動監測站,

2025-10-23 14:21:09 215

215

本文詳解淘寶圖片搜索接口開發全流程,涵蓋CNN特征提取、商品匹配、參數配置及400/429等高頻報錯解決方案,附合規避坑指南與可復用代碼,助你高效實現圖像搜商品功能。

2025-10-21 10:03:10 354

354 本文詳解淘寶開放平臺taobao.item_get接口對接全流程,涵蓋參數配置、MD5簽名生成、Python企業級代碼實現及高頻問題排查,提供可落地的實戰方案,助你高效穩定獲取商品數據。

2025-09-26 09:13:33 543

543

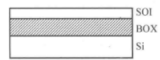

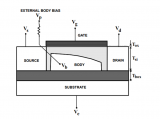

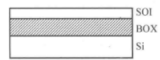

SOI(silicon-on-insulator,絕緣襯底上的硅)技術的核心設計,是在頂層硅與硅襯底之間引入一層氧化層,這層氧化層可將襯底硅與表面的硅器件層有效分隔(見圖 1)。

2025-09-22 16:17:00 6146

6146

在《恒流源驅動的低壓力傳感器SRT3000》一文中介紹了SRT3000壓力傳感器的基本參數,本期我繼續就SRT3000壓力傳感器上常見的幾個參數做簡單的介紹,因為理解這些參數有助于我們精確選擇合適

2025-09-22 12:14:21 784

784

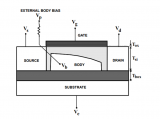

隨著半導體工藝進入納米尺度,傳統體硅(Bulk CMOS)技術面臨寄生電容大、閂鎖效應等瓶頸。SOI技術憑借埋氧層(BOX)的物理隔離優勢,成為航空航天、5G通信等領域的核心技術。本篇介紹一下業界SOI工藝模型BSIM-SOI模型。

2025-09-22 10:41:36 1622

1622

光纖通信里的“兩兄弟”CWDM和DWDM,名字只差一個字母,差別可大了去!今天一文講透核心差異,小易幫你快速分清~

2025-09-17 18:19:54 967

967

天然沙子里富含二氧化硅(SiO?),人們能夠從沙子中提取高純度單晶硅,以此制造集成電路。單晶硅對純度要求極高,需達到99.9999999%(即9個9)以上,且硅原子需按照金剛石結構排列形成晶核。當晶核的晶面取向一致時,就能形成單晶硅;若晶面取向不同,則會形成多晶硅(Polysilicon)。

2025-09-17 16:13:57 993

993

的一幀有300對字節,最少37字節,DMA模式為循環模式,緩沖buf,自己理解的是DMA的buf就是serial.c中的fifo buf,buf的size設置為2048;

問題:

1、數據接收存在粘包

2025-09-12 08:18:24

本文旨在通過講解不同模式的原理圖連接方式,進而配置用到引腳的含義(手冊上相關引腳含義有四、五頁,通過本文理解基本上能夠記住所有引腳含義以及使用場景),熟悉xilinx 7系列配置流程,以及設計原理圖時需要注意的一些事項,比如flash與FPGA的上電時序。

2025-08-30 14:35:28 9296

9296

主要用于高性能模塊(如CPU、DMA和DSP等)之間的連接,一個master可以有多個slave,AHB和APB之間通過一個AHB2APB橋轉接。這里是實現一個AHB_Lite協議,相較于AHB_APB

2025-08-27 09:23:13 2714

2714

晶棒需要經過一系列加工,才能形成符合半導體制造要求的硅襯底,即晶圓。加工的基本流程為:滾磨、切斷、切片、硅片退火、倒角、研磨、拋光,以及清洗與包裝等。

2025-08-12 10:43:43 4165

4165

會展中心舉行。大華股份應邀參加本次活動,以"科技賦能文旅融合"為主題,全面展示在推動文旅產業數字化轉型方面的技術實力與創新實踐。

2025-08-05 17:07:29 1017

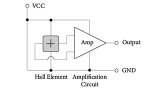

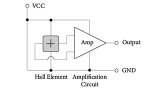

1017 全面認知·線性霍爾IC 線性霍爾IC,是一種rail to rail的模擬輸出傳感器,后端微控制器處理起來簡單方便,因此與霍爾IC一樣,適用于白色家電和工業設備。 線性霍爾IC進行模擬輸出,與數字

2025-07-24 17:59:26 2168

2168

一.串口輸入輸出測試1.1發送測試hal_entry.c中 初始化串口 err = R_SCI_UART_Open(&g_uart0_ctrl, &amp

2025-07-19 22:19:43

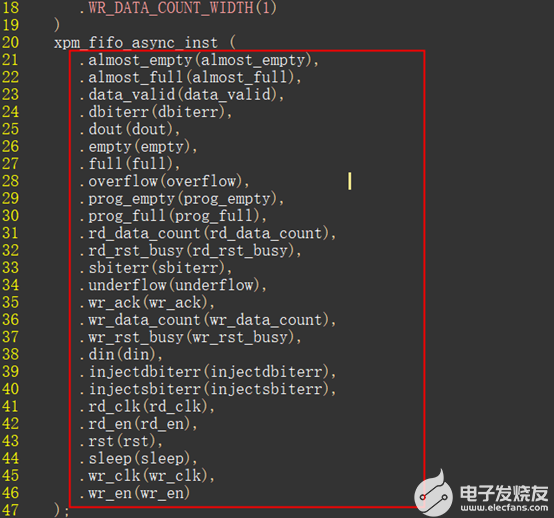

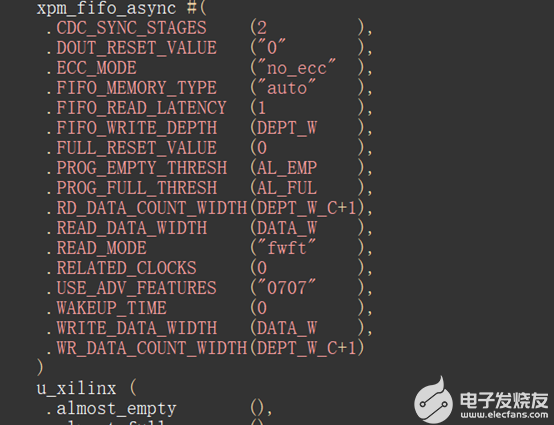

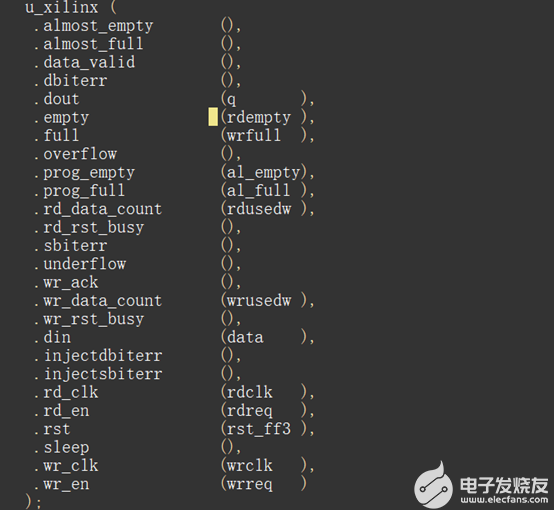

和功能均一致,不會像 PLL 那樣有動態配置以及內部反饋選項的選擇等之間的差異,所以是 RAM、ROM、FIFO 是通用的。

2.1. RAM 介紹

RAM 即隨機存取存儲器。它可以在運行過程中把數據

2025-07-10 10:37:35

特性、應用場景三方面詳解: 一、核心優勢:降本增效,重塑搬運邏輯 ?人力成本銳減? 叉車agv移動機器人替代人工叉車司機,實現24小時不間斷作業,大幅降低人力成本與培訓支出。 統計顯示,單臺自動叉車AGV機器人可替代2-3名人工司機,

2025-06-24 15:16:07 537

537 擠出機 PLC 全參數數據采集與遠程智能監控一體化系統方案

2025-06-20 17:36:07 622

622

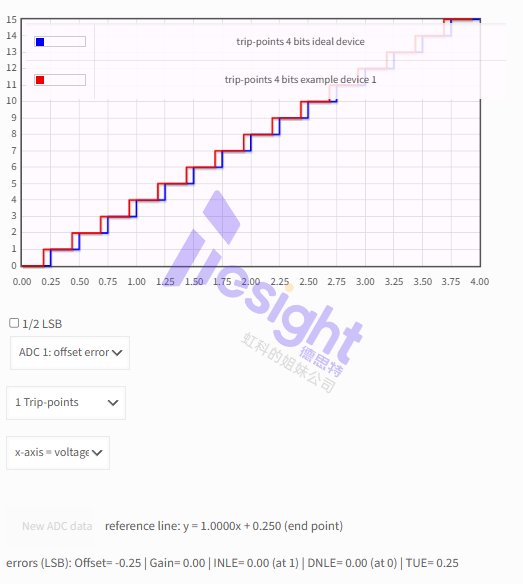

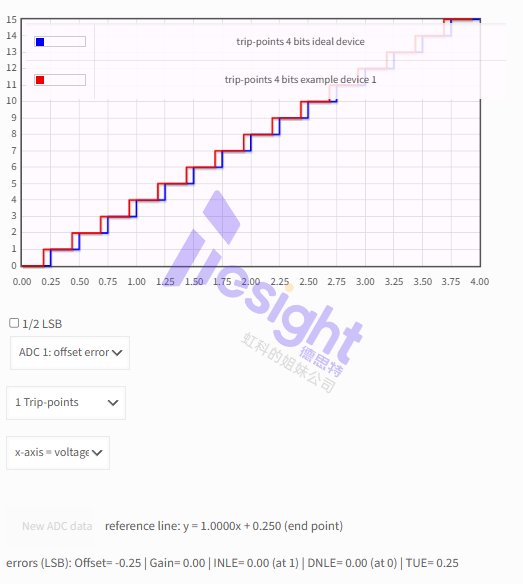

上一期我們詳解了DAC的核心術語,本期繼續深入探討DAC靜態參數計算!從偏移誤差、增益誤差到INL/DNL,再到未調整總誤差(TUE),一文掌握D/A轉換器的關鍵性能指標!

2025-06-20 11:49:54 1837

1837

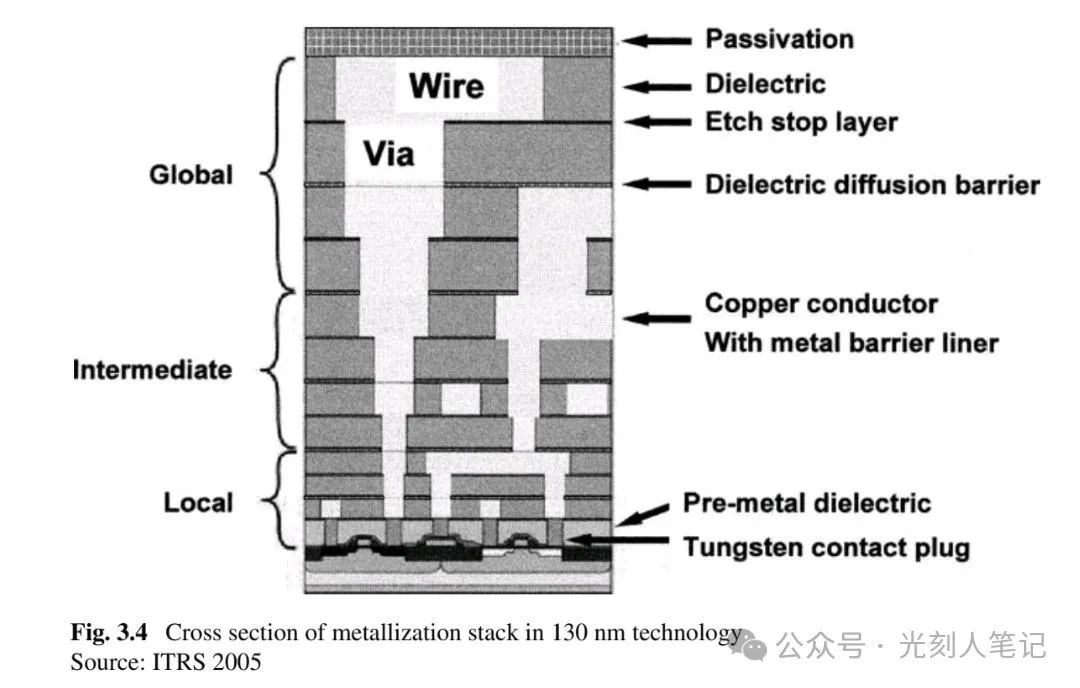

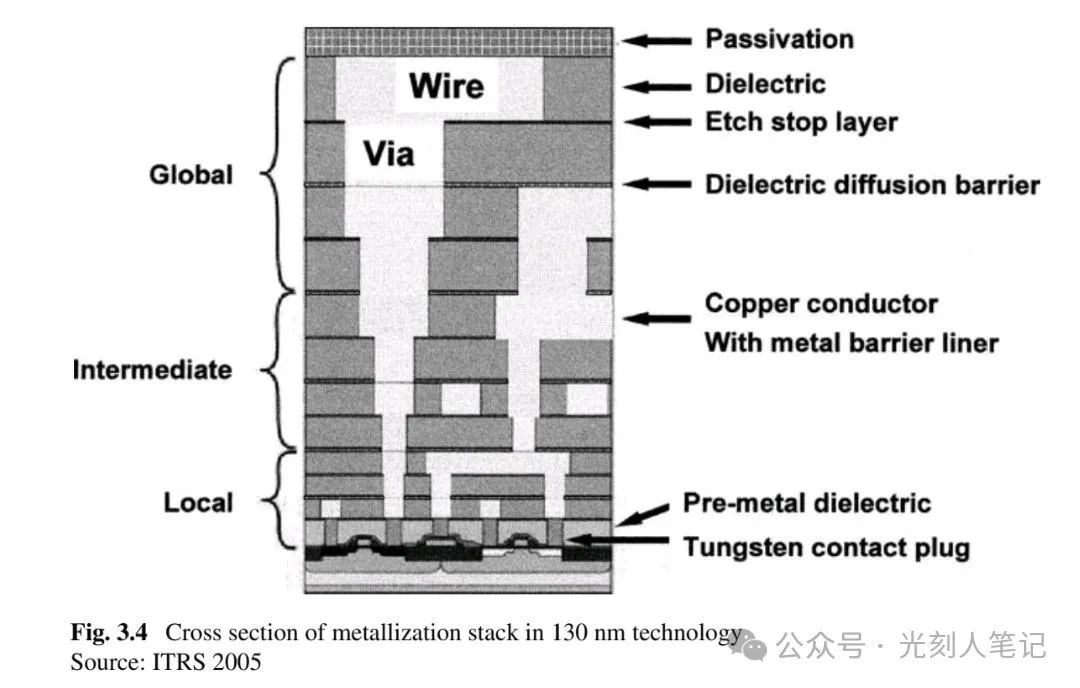

銅互連工藝是一種在集成電路制造中用于連接不同層電路的金屬互連技術,其核心在于通過“大馬士革”(Damascene)工藝實現銅的嵌入式填充。該工藝的基本原理是:在絕緣層上先蝕刻出溝槽或通孔,然后在溝槽或通孔中沉積銅,并通過化學機械拋光(CMP)去除多余的銅,從而形成嵌入式的金屬線。

2025-06-16 16:02:02 3559

3559

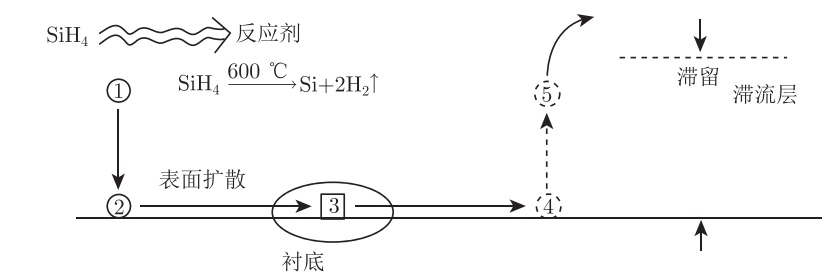

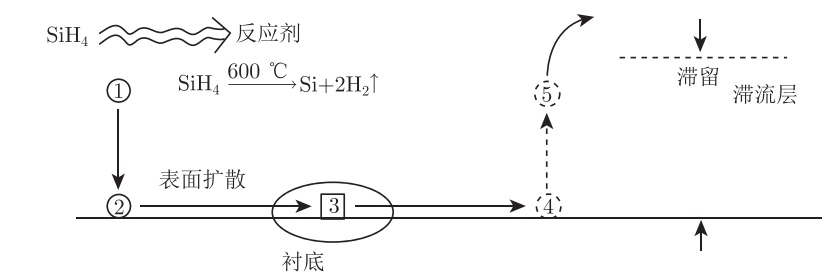

隨著半導體器件特征尺寸不斷微縮,對高質量薄膜材料的需求愈發迫切。外延技術作為一種在半導體工藝制造中常用的單晶薄膜生長方法,能夠在單晶襯底上按襯底晶向生長新的單晶薄膜,為提升器件性能發揮了關鍵作用。本文將對外延技術的定義、分類、原理、常用技術及其應用進行探討。

2025-06-16 11:44:03 2478

2478

【HarmonyOS 5】鴻蒙中的UIAbility詳解(三) ##鴻蒙開發能力 ##HarmonyOS SDK應用服務##鴻蒙金融類應用 (金融理財# 一、前言 本文是鴻蒙中的UIAbility

2025-06-14 22:32:59 603

603 就是遇到一個問題,我進入fifo模式+中斷,FIFO_STATUS1 和FIFO_STATUS1 獲取未讀數據,發現不會更新了,遠遠沒有到達我設定的水閾,所以不知道問題出在那里,有人遇到過這個

2025-06-08 15:08:09

近幾年,“國產化替代”成為各行各業繞不開的熱門話題,尤其是在AI、數據中心、智慧城市、工業自動化等領域,芯片國產化更是關鍵中的關鍵。而在眾多國產AI芯片中,昇騰310B頻頻被點名,不少企業的國產化方案都優先選擇它。那么問題來了,昇騰310B芯片參數到底怎么樣?為啥它在企業國產化大潮中脫穎而出?

2025-06-06 13:31:15 4337

4337

傳遞函數中的零點、極點,最終確定反饋補償網絡中各元件的參數,以便獲得穩定的帶寬適中的閉環控制系統,使DC-DC 、AC-DC變換器具有良好的抗干擾性能。

2025-06-05 17:02:28 3041

3041

ADC性能評估的關鍵指標如何計算?本文用ADC實例,詳解偏移/增益/INL/DNL/TUE六大參數的計算方法,帶您掌握從跳變點提取到誤差分析的全流程。通過典型ADC數據和交互式圖表,直觀理解參數間的關聯與影響,助您提升測試精度!

2025-06-05 14:50:24 817

817

應對這些挑戰提供了科學依據和技術支持。氣體腐蝕測試的基理與作用氣體腐蝕是指金屬表面在無液相條件下與腐蝕性氣體發生化學反應而導致的劣化現象。這種腐蝕過程主要受溫濕度、

2025-06-04 16:24:36 483

483

SSH常用命令詳解

2025-06-04 11:30:05 1841

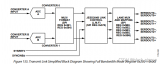

1841 本文主要介紹基于Xilinx UltraScale+MPSoC XCZU7EV的高速AD采集與高速DA輸出案例

2025-06-03 14:22:30 740

740

,一直循環 SLOE 低 SLRD 低讀數據 SLRD 高 SLOE高,是EP8,也設置了地址為11,但是flag 空標志一直也不會變回低,EP8FIFOBCH 的值也不會變回到0

請問大家,這個要檢查什么呢,要注意什么呢,謝謝。 有沒有哪里是介紹外部mcu異步讀寫 slave fifo的?

2025-06-03 10:49:04

電子發燒友網站提供《XILINX XCZU67DR FPGA完整原理圖.pdf》資料免費下載

2025-05-30 15:29:38 4

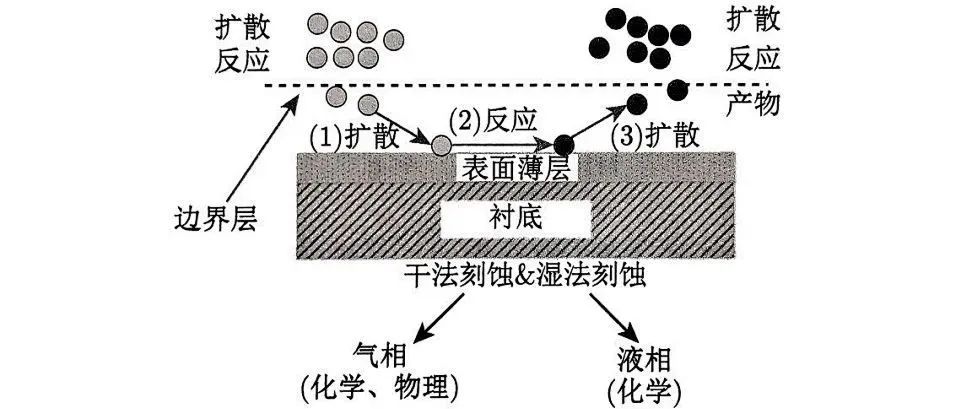

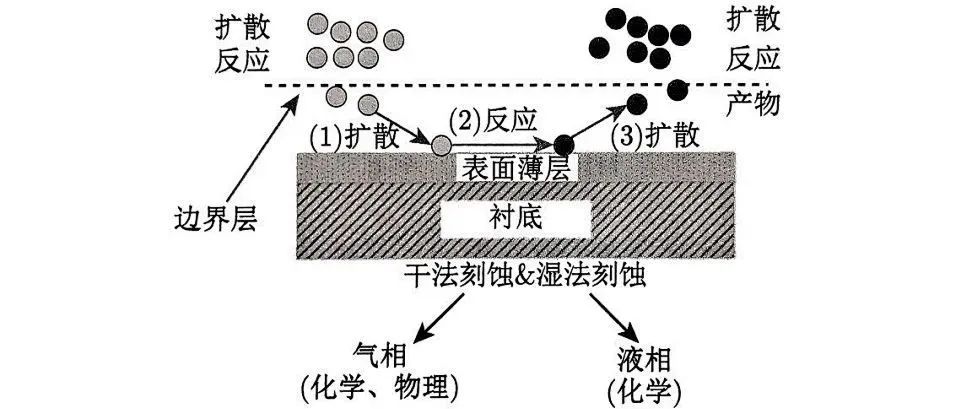

4 濕法刻蝕作為半導體制造領域的元老級技術,其發展歷程與集成電路的微型化進程緊密交織。盡管在先進制程中因線寬控制瓶頸逐步被干法工藝取代,但憑借獨特的工藝優勢,濕法刻蝕仍在特定場景中占據不可替代的地位。

2025-05-28 16:42:54 4247

4247

明渠雷達流量計作為現代水文監測領域的核心設備,基于先進的微波技術實現非接觸式流量監測,廣泛應用于河道、灌區、城市排水等場景。以下從多個維度對其技術參數進行詳細解析:?一、流速測量技術參數?1.測量

2025-05-24 16:13:15 670

670

在納米尺度集成電路制造領域,快速熱處理(RTP)技術已成為實現器件性能突破與工藝優化的核心工具。相較于傳統高溫爐管工藝,RTP通過單片式作業模式與精準的熱過程控制,有效解決了先進制程中熱預算控制、超淺結形成及工藝一致性的技術痛點。

2025-05-22 16:04:03 2205

2205

一般是以高穩定度參考源比如晶振所產生的頻率信號作為基準,經過必要的的加減乘除運算(對不同信號混頻可以看作對相應頻率的加減運算,倍頻和分頻看作乘除運算)得到需要的新的頻率,由于這樣產生的頻率是一

2025-05-20 14:05:25 16939

16939

問題 1)從機FIFO接口圖顯示支持DQ[31:0],但表格僅表明支持DQ[15:0]。 哪一個是正確的? 請詳細解釋一下。

問題 2) 從屬 FIFO 接口使用 A[1:0]、FLAGA 和 FLAGB,但 USB 通信也可以與所連接的電路配合使用。 我可以只使用 FLAGA 嗎?

2025-05-16 06:15:15

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個 LogiCORE IP 核,用于在 FPGA 中實現高效的移位寄存器(Shift Register)。該 IP 核利用

2025-05-14 09:36:22 912

912 開關電源的各個元器件怎么計算?損耗怎么估算?散熱器的大小怎么計算?

51頁圖文詳解,一文帶你弄懂!

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

2025-05-12 16:20:10

FIFO_Generator是智多晶設計的一款通用型FIFO IP。當前發布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比輸入輸出數據位寬支持和異步FIFO跨時鐘級數配置功能。

2025-04-25 17:24:24 1568

1568

Jenkins自動化部署是現代軟件開發中不可或缺的一部分,它不僅簡化了代碼的發布過程,還為整個團隊帶來了無與倫比的效率和協作力。想象一下,開發者們可以專注于編寫高質量的代碼,而不是為繁瑣的手動部署所

2025-04-23 10:50:18 2733

2733

目前遇到了幾個問題,問題分別是[FPGA]給的時鐘是250兆Hz,數據為40mhz正弦信號,ddr傳輸。不采用pll工作模式,dacclk采用1G,0x1c配置00,0x1d配置00,0x1e配置01,Fifo亂序,輸出也亂序,查了幾次fifo狀態。無規律亂跳。

2025-04-22 14:42:44

如果要在Xilinx的FPGA上使用萬兆以太網通信,大致有三種方法構建協議棧。第一種使用GTX等Serdes作為底層的PHY,上層通過HDL實現構建MAC和IP層,這種方式難度會比較大,底層需要完成PHY層的設計,最終我想通過這種方式實現萬兆以太網的搭建。

2025-04-18 15:16:30 1732

1732

芯片新關稅涉及的品牌/標簽/產地—詳解

2025-04-16 17:44:11 915

915

ITO薄膜的表面粗糙度與厚度影響著其產品性能與成本控制。優可測亞納米級檢測ITO薄膜黃金參數,幫助廠家優化產品性能,實現降本增效。

2025-04-16 12:03:19 824

824

目前遇到了幾個問題,問題分別是Fpga給的時鐘是250兆Hz,數據為40mhz正弦信號,ddr傳輸。不采用pll工作模式,dacclk采用1G,0x1c配置00,0x1d配置00,0x1e配置01,Fifo亂序,輸出也亂序,查了幾次fifo狀態。無規律亂跳。

2025-04-15 08:11:20

MCP 傳輸機制(Transport)是 MCP 客戶端與 MCP 服務器通信的一個橋梁,定義了客戶端與服務器通信的細節,幫助客戶端和服務器交換消息。

2025-04-14 14:03:28 3252

3252

多芯片堆疊技術的出現,順應了器件朝著小型化、集成化方向發展的趨勢。該技術與先進封裝領域中的系統級封裝(SIP)存在一定差異。

2025-04-12 14:22:05 2565

2565

波峰焊接是一種復雜的工藝過程,涉及到金屬表面、熔融焊料、空氣等多種因素。焊接質量受到多種因素的影響,如印制板、元器件、焊料、焊劑、焊接溫度、時間等工藝參數以及設備條件等。

因此,要獲得一個優良的焊接

2025-04-09 14:44:46

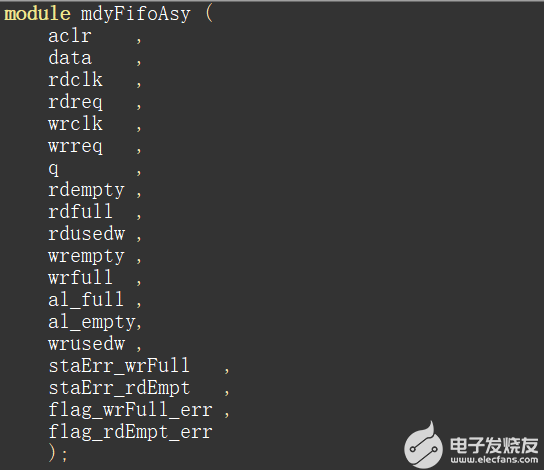

FIFO(First in First out)為先進先出隊列,具有存儲功能,可用于不同時鐘域間傳輸數據以及不同的數據寬度進行數據匹配。如其名稱,數據傳輸為單向,從一側進入,再從另一側出來,出來的順序和進入的順序相同。

2025-04-09 09:55:57 1292

1292

IAR正式發布全新云就緒平臺,為嵌入式開發團隊提供企業級的可擴展性、安全性和自動化能力。

2025-04-07 11:21:42 533

533 ,SG)功能還可以將數據移動任務從位于于處理器系統中的中央處理器(CPU)中卸載出來。可以通過一個AXI4-Lite從接口訪問初始化、狀態和管理寄存器。如圖4. 8展現了DMA IP的功能構成核心。

2025-04-03 09:32:24 2246

2246

在線監測管理系統的智能化功能詳解 多角色權限與多項目管理 多終端適配 在線監測管理系統采用基于BS架構設計,用戶可通過瀏覽器實現項目管理、數據查看與下載、曲線分析等操作。系統界面設計遵循簡約統一

2025-03-19 17:18:54 657

657 今天,我們看一下電路中電感和電容一起出現時會發生什么有趣的事情。

2025-03-19 09:47:00 15152

15152

Verilog HDL(Hardware Description Language)是一種硬件描述語言,用于從算法級、門級到開關級的多種抽象設計層次的數字系統建模。現實生活中多用于專用集成電路

2025-03-17 15:17:04 3996

3996

的依存關系。例如,在此示例中,我們使用參數耦合來確保用戶編程的傾斜光柵介質的z軸擴展長度與包含該結構的結構化層的厚度一致性。

2.參數運行的初始化

我們希望鏈接光學系統的兩個參數,以便它們自動取相同的值

2025-03-17 11:11:02

AXI接口FIFO是從Native接口FIFO派生而來的。AXI內存映射接口提供了三種樣式:AXI4、AXI3和AXI4-Lite。除了Native接口FIFO支持的應用外,AXI FIFO還可以用于AXI系統總線和點對點高速應用。

2025-03-17 10:31:11 1914

1914

入門》手冊。1.技術背景TSMaster的小程序模塊中提供了接收事件、發送事件以及預發送事件等回調事件,如圖1。相比于回調函數,fifo函數使用起來比較靈活方便,可

2025-03-14 20:04:21 1013

1013

,而且使直流母線電壓的利用率有了很大提高,且更易于實現數字化。下面將對該算法進行詳細分析闡述。

文章過長,請點擊下方可查閱*附件:SVPWM的原理及法則推導和控制算法詳解.pdf

2025-03-14 14:51:04

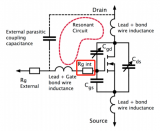

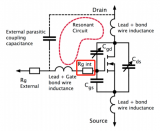

在現代電子電路設計和應用中,寄生參數是指那些并非設計者最初所期望的,但在電路或元器件中由于物理結構、材料特性或布局布線等因素而自然產生的非預期電氣參數。這些參數雖然不是設計之初所考慮的,但它們對電路的性能和行為有著不可忽視的影響。在本次研究中,重點探討寄生電感對柵極振蕩的影響,同時通過實驗來逐步驗證。

2025-03-14 13:47:57 22756

22756

抑制器,就如同電路的 “保護神”,挺身而出。今天,就讓我們深入了解 TVS 的參數奧秘。 01 TVS 管是什么? TVS 管,又稱瞬態電壓抑制二極管,是一種新型高效電路保護器件。它擁有極快的響應時間,能在亞納秒級的瞬間做出反應,同時具備相當高的浪涌吸收能力。其工作原理基于其特殊

2025-03-12 15:43:07 2363

2363

能夠改變光學系統的參數是任何設置分析的關鍵部分,以便更好地了解系統在從制造錯誤到組件潛在錯位的任何情況下的行為。設計一個在面對這些不可避免的偏離理想化預期設計時表現出魯棒性的系統,與找到一個完全滿足

2025-03-07 08:46:51

無法使用密度化參數構建OpenVINO?二進制

2025-03-06 06:51:11

前言 SDRAM控制器里面包含5個主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀模塊,SDRAM接口控制模塊,SDRAM指令執行模塊。 其中異步FIFO模塊解讀

2025-03-04 10:49:01 2301

2301

一、原理介紹

如上圖所示,文氏橋正弦波振蕩電路主要包括2個部分,與運算放大器正極相連的正反饋網絡,與負極相連的負反饋網絡。

1、正反饋網絡側的2個電容、電阻對應相等,起到了選頻的作用,頻率為1/(2

2025-02-27 18:48:43

因工作需求,自己寫的HFSS參數自動化建模工具,目前只實現了常用的四種模型,可定制化,如需可聯系 qq:1300038043

附件下載鏈接:https://pan.baidu.com/s/1TVeTTFiJw-pxSyT1AT8IQA 提取碼: kxup

2025-02-27 17:44:31

在現代高速數字電路設計中,電源完整性和信號完整性是確保電路性能的關鍵因素。為了準確評估這些參數,設計師們引入了Power-Aware IBIS模型。本文將介紹Power-Aware IBIS模型的概念、內容組成及其在實際仿真中的應用案例。

2025-02-27 17:00:32 1300

1300

電子發燒友網站提供《一文解析工業互聯網.pptx》資料免費下載

2025-02-20 16:42:51 1

1 電力電子中的坐標變換詳解 clark變換&park變換

2025-02-17 15:28:18 1

1 Kubernetes Pod常用管理命令詳解

2025-02-17 14:06:35 1088

1088

隨著文心大模型的迭代升級和成本不斷下降,文心一言將于4月1日0時起全面免費,所有PC端和APP端用戶均可體驗文心系列最新模型。

2025-02-17 13:44:49 856

856 夠免費使用DeepSeek和文心大模型的深度搜索功能。這一功能不僅融合了先進的搜索算法,還借助文心大模型的強大能力,實現了對信息的深度挖掘和精準匹配。用戶在進行搜索時,將能夠獲得更加全面、準確的結果,滿足多樣化的需求。 同時,文

2025-02-17 09:14:37 1034

1034 隨著文心大模型的迭代升級和成本不斷下降,文心一言將于4月1日零時起,全面免費,所有PC端和APP端用戶均可體驗文心系列最新模型。

2025-02-13 10:46:24 730

730 視覺語言模型(VLM)是一種多模態、生成式 AI 模型,能夠理解和處理視頻、圖像和文本。

2025-02-12 11:13:18 3467

3467

精密空調操作使用方法詳解

2025-02-10 14:44:07 2040

2040

一、 導讀? ? 前幾天一位搞電氣的朋友問S7-1200中如何做個先入先出的功能,說原來用S7-200SMART的時候有填表指令和FIFO指令可以實現該功能,現在S7-1200中找了一圈都沒有

2025-02-09 10:27:49 1251

1251

其實使用到ADI的東西,基本也就沒有太去關注協議這些東西,只是簡簡單單的有個了解就行,在實際調試的時候,用的也是Xilinx的評估版的JESD的IP,基本不需要自己做什么工作就能夠把整個系統運行起來了。

2025-02-08 13:45:55 3990

3990

ADC08200可工作在10M~230MHZ之間的頻率,

請問TI有沒有一款FIFO可以與ADC08200通信?好像最高速率的也只有166MHZ??

2025-02-08 08:37:23

請問下專家:為什么我在ADS822加FIFO測試的時候老是卡死,基本過程是這樣的,我外部提供一個時鐘,分別給ADS822做采樣時鐘與FIFO的寫時鐘,程序開始控制FIFO寫開啟,讀關閉,然后

2025-02-06 06:32:41

關于LD2410B/C那些你不得不知道的事?免費申樣、接線教程、參數解析、APP調參教程、上位機調參教程、常見異常情況自檢等等內容,一文匯總~不管是萌新小白還是資深玩家,都可以快速入門

2025-02-05 18:09:25 2810

2810

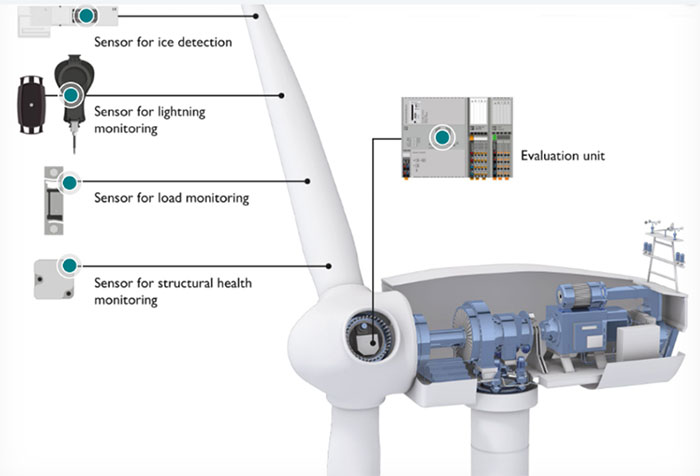

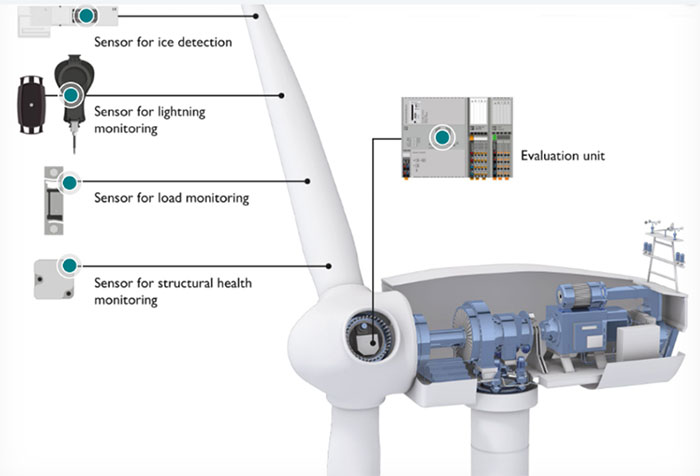

了一個名為“全電氣化社會”的概念,并以此作為未來十年的目標。在其愿景中,可再生能源是通過利用電氣化、網絡化和自動化技術打造智能化和網絡化系統而高效生成和利用的。 清潔、可持續的能源來自光伏、水電、風能和地熱資源。電池或綠色氫氣等儲能系統與發電過

2025-01-26 17:43:00 966

966

給FIFO的時鐘加個NOT門反相么?

因為AD的流水線結構會有6個時鐘延遲,那么上電后第一個時鐘,或者前六個時鐘過來的時候,AD輸出的是什么狀態?高阻態?全0?

CDCE925這個PLL的輸出

Y4,Y5是同相位的么??

2025-01-22 06:44:25

,成為核心競爭力所在。 智能座艙設計趨勢:用戶可自定義產品功能組合 按照智能座艙以人為本的用戶體驗設計,個性化智能座艙已成為一大發展趨勢,個性化自定義設置從車機系統、按鍵等基本的個性化自定義設置外,現在通過軟件架構等可實現車內

2025-01-17 16:46:57 3624

3624

? 通感一體化:擴展通信網絡業務邊界,提升網絡價值 通信引入感知構筑通感一體 一網多能:鏈接物理世界和數字世界 網絡通信+傳統感知+泛在感知+云...,形成一張網多種能力,網絡即服務;泛在的通感

2025-01-16 17:53:11 2946

2946

在工業自動化和精密測量領域,拉線編碼器以其高精度、長壽命和靈活的安裝方式,成為了眾多應用場合的首選。然而,面對市場上琳瑯滿目的拉線編碼器產品,如何挑選一款符合自己需求的編碼器,成為了許多工程師和采購人員面臨的挑戰。本文將詳細介紹拉線編碼器的關鍵參數,幫助您更好地理解和選擇。

2025-01-07 15:53:06 1275

1275 2024 年,全球科技蓬勃發展,無人駕駛技術成為熱門賽道,文遠知行進入了高速發展的快車道,在無人駕駛商業化的進程上取得了眾多突破。 2024年12月20日,“全球Robotaxi第一股”文遠知行

2025-01-07 10:45:44 808

808

BNC連接器,全稱為Bayonet Neill-Concelman連接器,是一種小型的可實現快速連接的卡口式射頻同軸連接器。其技術參數詳解如下:

阻抗特性:

BNC連接器的標準工作阻抗為50Ω或

2025-01-07 09:34:12 1347

1347

電子發燒友App

電子發燒友App

評論