文章來源:學習那些事

原文作者:前路漫漫

本文介紹了與SOI相關的技術。

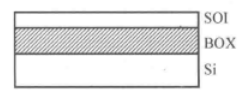

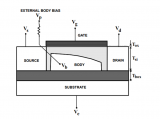

SOI(silicon-on-insulator,絕緣襯底上的硅)技術的核心設計,是在頂層硅與硅襯底之間引入一層氧化層,這層氧化層可將襯底硅與表面的硅器件層有效分隔(見圖 1)。借助在絕緣體上形成半導體薄膜的結構,SOI 材料具備體硅無法比擬的優勢:能實現集成電路中元器件的介質隔離,徹底根除體硅 CMOS 電路中的閂鎖(Latch-up)效應;基于該材料制作的集成電路還擁有寄生電容低、集成密度高、運行速度快、制備工藝簡化、短溝道效應弱等特點,尤其適配低壓低功耗電路場景,因此 SOI 有望成為深亞微米級低壓低功耗集成電路的主流技術方向。

SOI 的核心材料主要包括三類:通過注氧隔離制備的 SIMOX(separation by implanted oxygen,注氧隔離)材料、經硅片鍵合與反面腐蝕制成的 BESOI(bonding-etchback SOI,鍵合 - 回蝕 SOI)材料,以及融合鍵合與離子注入技術的 Smart Cut SOI 材料。在這三類材料中,SIMOX 適用于制備薄膜全耗盡超大規模集成電路,BESOI 材料更適配部分耗盡集成電路的制作;而后續發展的 Smart Cut(智能剝離)技術,整合了 SIMOX 與 BESOI 的優勢,屬于極具發展潛力的 SOI 材料,未來有望成為 SOI 材料的主流類型。

注氧隔離技術(SIMOX)

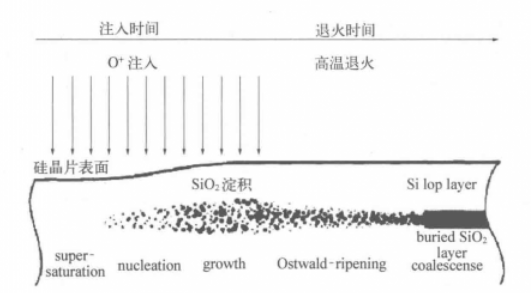

作為 SOI 圓片制備領域發展最早的技術之一,SIMOX 曾被認為有望實現大規模應用。該技術的核心步驟包含離子注入與高溫退火 —— 具體為高能量、高劑量的氧離子注入及后續退火處理,其中注入能量通常為幾十 keV,注入劑量約為 1×101? cm?2。在注入過程中,氧離子進入硅圓片內部并與硅發生反應,形成二氧化硅沉淀物;經過 1150℃下 2 分鐘的退火處理后,可在硅圓片表面下方 380nm 處形成厚度為 210nm 的 SiO?層,其工藝流程如圖 2 所示。

盡管 SIMOX 技術因發展歷史悠久而相對成熟,但長時間大劑量的離子注入,以及后續需進行的超高溫長時間退火工藝,導致 SIMOX 材料在質量穩定性與成本控制方面難以實現突破,這也是目前該技術尚未被產業界完全接納并大規模應用的根本原因。SIMOX 技術面臨的核心難點包括:顆粒污染控制、埋層(尤其低劑量 / 超低劑量埋層)的結構完整性、金屬雜質沾污、界面臺階控制、界面與表面粗糙度,以及表層硅中的缺陷問題,其中材料質量的穩定性更是難以保證。

薄膜全耗盡(FDSOI)

通常依據絕緣體上硅膜的厚度,可將 SOI 結構劃分為薄膜全耗盡(FD,fully depleted)與厚膜部分耗盡(PD,partially depleted)兩類。由于 SOI 具備介質隔離特性,制作于厚膜 SOI 結構上的器件,其正面與背面界面的耗盡層互不影響,兩層之間存在一個中性體區。該中性體區的存在會使硅體處于電學浮空狀態,進而產生兩種明顯的寄生效應:一是 “翹曲效應”(即 Kink 效應),二是器件源極與漏極之間形成的基極開路 NPN 寄生晶體管效應。若將該中性區通過體接觸接地,厚膜 SOI 器件的工作特性便與體硅器件幾乎一致。

而基于薄膜 SOI 結構的器件,因硅膜可實現完全耗盡,能徹底消除 “翹曲效應”;同時這類器件還具備低電場、高跨導、優異的短溝道特性,以及接近理想值的亞閾值斜率等優勢,因此薄膜全耗盡 FDSOI 被認為是極具前景的 SOI 結構類型。

鍵合技術(BESOI)

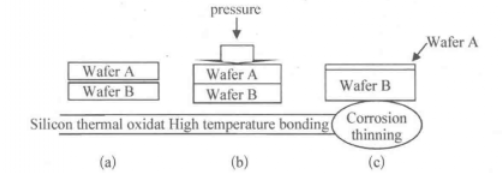

通過鍵合(bond)技術,可使硅(Si)與二氧化硅(SiO?)、或二氧化硅與二氧化硅之間的兩個圓片緊密結合,并在兩圓片中間形成 SiO?層作為絕緣層。BESOI 圓片的制備需在鍵合完成后,將其中一個圓片的一側削薄至目標厚度,整個過程分為三步(見圖 3)。

鍵合技術面臨的核心問題是表層硅厚度的均勻性控制,這也是限制該技術廣泛推廣的根本原因。除此之外,鍵合邊緣的控制、界面缺陷、圓片翹曲度與彎曲度的控制、滑移線抑制、顆粒污染防控、崩邊問題,以及界面沾污等,均是制約 BESOI 產業化制備的關鍵技術難題。而成品率與成本控制,則是決定鍵合類 SOI 產品能否被量產客戶接受的核心商業因素。另外,Wafer A(待減薄圓片)的減薄效率,也是影響 BESOI 技術實用化進程的重要因素,具體可參考圖 3(c)。

智能剝離法(Smart-cut)

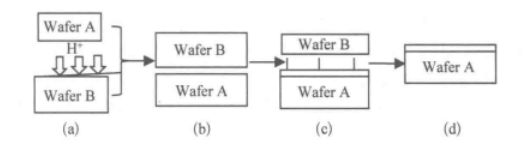

Smart-cut(智能剝離)技術是融合 SIMOX 技術與 BESOI 技術優勢的創新工藝,既繼承了兩者的核心特點,又克服了各自的不足,屬于當前較為理想的 SOI 制備方案。其技術特征體現在改進型 Smart-cut 制備 SOI 基底的流程中:通過該工藝制備 SOI 基底后,結合電子束光刻與深反應離子刻蝕技術,可制作具有二維周期結構的光子晶體,同時引入線缺陷構建光子晶體波導。該技術主要包含四個關鍵步驟,具體如圖 4 所示。

H?離子注入:在室溫環境下,以特定能量向硅片 A 注入定量 H?離子,使硅片表層下方形成一層富含 H?離子的硅層;與此同時,對支撐硅片進行熱氧化處理,在其表面生成一層氧化層,具體結構如圖 4(a)所示。

預鍵合:先對硅片 A 與另一硅片 B 進行嚴格的清洗與活化處理,隨后在室溫下將兩片硅片的拋光面貼合,實現初步鍵合,如圖 4(b)所示。需注意,硅片A 與 B 中至少有一片的鍵合表面需通過熱氧化法生長SiO?層,該層將作為 SOI 結構中的隱埋絕緣層。

熱處理:整體分為兩步進行:第一步,將鍵合后的硅片置于高溫環境中,注入的高濃度 H?離子層會發生成核并形成氣泡,氣泡急劇膨脹促使硅片在富含 H?離子的層位發生剝離,剝離后的硅層留存備用,剩余硅層則作為 SOI 結構的頂部硅層,如圖 4(c)所示;第二步,通過高溫熱處理進一步提升鍵合界面的結合強度,并消除 SOI 層中因離子注入產生的結構損傷。

化學機械拋光:對剝離后的硅片表面進行拋光處理,降低表面粗糙度,如圖 4(d)所示。斷裂面經輕度拋光后,即可達到體硅的表面光潔度,目前已能制備出頂層硅厚度為 200±4nm 的 4 英寸SOI 材料。

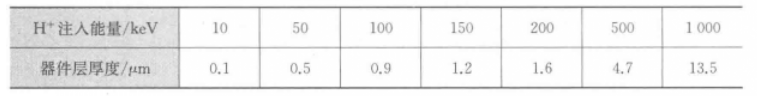

SOI 片頂層硅膜的厚度與 H?注入能量直接相關:H?注入能量越高,H?注入峰的深度越大,頂層硅膜的厚度也隨之增加。表 9-1 詳細列出了器件層厚度與 H?注入能量的對應關系。

相較于 SIMOX 與 BESOI 兩種 SOI 制備技術,Smart-cut 技術的優勢十分顯著:其一,H?注入劑量僅為 1×101? cm?2,比 SIMOX 低兩個數量級,可采用普通離子注入機完成,降低設備成本;其二,埋氧層通過熱氧化工藝形成,不僅 Si/SiO?界面質量優異,氧化層本身性能也更穩定;其三,剝離后的硅片可重新作為鍵合襯底循環使用,大幅降低原材料消耗,同時硅層減薄效率顯著提升。因此,Smart-cut 技術已成為 SOI 材料制備領域中競爭力最強、發展前景最廣的技術之一。自 1995 年開發以來,該技術發展迅速,法國 SOITEC 公司已能提供基于 Smart-cut 技術制備的商用 SOI 硅片,并擁有相關核心專利。

GaAs 和 Ge 有源襯底層

當互補型金屬氧化物半導體(CMOS)場效應管的柵極長度接近 10nm 后,傳統 CMOS 技術的縮放效應面臨根本性的物理限制。下表對比了幾類相關半導體材料的電學性質。

由于 GaAs 系列 Ⅲ-Ⅴ 族化合物半導體的電子遷移率遠高于硅材料,因此有望替代硅用于制作 nMOSFET。不過,Ⅲ-Ⅴ 族 MOSFET 的研發面臨兩大核心挑戰:一是如何在硅基平臺上集成高品質的 GaAs 系列 Ⅲ-Ⅴ 族溝道層材料;二是如何實現穩定的 Ⅲ-Ⅴ 族半導體 / 高 k 柵絕緣層界面,并規避常見的費米能級釘扎效應(Fermi Pinning Effect,該效應會導致金屬柵的費米能級被釘扎在半導體禁帶中央附近,無法滿足雙金屬柵 MOS 器件對閾值電壓的要求)。

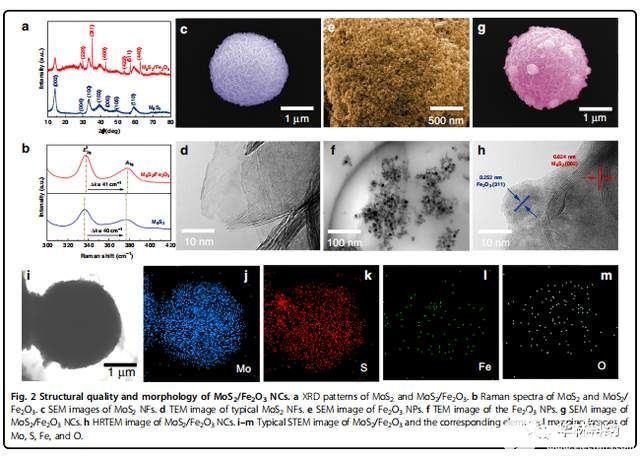

近年來,薄膜淀積技術取得顯著突破。H.J.Oh 團隊報道了在氧化硅上生長砷化鎵絕緣體的成果,成功實現硅基平臺上的 GaAs 異質外延層制備;結合金屬有機物化學氣相淀積(MOCVD)技術,進一步制作出 InGaAs/HfO?疊層結構,有效規避了界面費米能級釘扎問題,基于該結構的 NMOS 場效應管速度比傳統硅基器件快近 3 倍。

對于 pMOSFET 而言,鍺硅(GeSi)異質結系列半導體的空穴遷移率遠高于硅材料,因此可作為硅的替代材料制作 pMOSFET。由于鍺材料與硅材料的晶格匹配度較高,在硅基底上制備鍺硅系列 pMOSFET 的難度相對較低。MT.Currie 團隊與張雪鋒團隊通過在高 k 介質與 Ge 表面引入 HfO?/HfON 疊層柵介質,制作出的 pMOS 器件有效遷移率可達硅基器件的 2 倍左右。

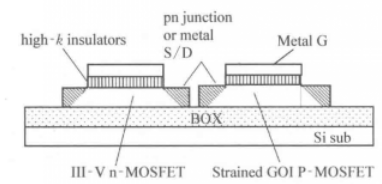

圖 5 展示了以 GaAs 為 nMOS、Ge 為 pMOS 的下一代硅基 CMOS 結構,該結構仍以硅基 SOI 為襯底材料,有望成為下一代集成電路(IC)中 CMOS 的首選電路單元。

?

-

集成電路

+關注

關注

5461文章

12634瀏覽量

375319 -

半導體

+關注

關注

339文章

31062瀏覽量

265681 -

鍵合

+關注

關注

0文章

104瀏覽量

8297 -

SOI

+關注

關注

4文章

83瀏覽量

18464

原文標題:SOI異質結襯底

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

常見幾種SOI襯底及隔離的介紹

異質結雙極晶體管,異質結雙極晶體管是什么意思

什么是雙異質結(DH)激光器

砷化硼異質結—潛在的光電薄膜和襯底材料

自清潔半導體異質結襯底說明

基于單一材料的新型維材料異質結的替代方法

什么是SOI襯底?SOI襯底的優勢是什么?

一文詳解BSIM-SOI模型

一文詳解SOI異質結襯底

一文詳解SOI異質結襯底

評論