本文主要介紹基于Xilinx UltraScale+MPSoC XCZU7EV的高速AD采集與高速DA輸出案例,適用開發(fā)環(huán)境如下:

Windows開發(fā)環(huán)境:Windows 7 64bit、Windows 10 64bit

PL端開發(fā)環(huán)境:Xilinx Unified 2022.2

硬件平臺:創(chuàng)龍科技TLZU-EVM評估板

方案介紹

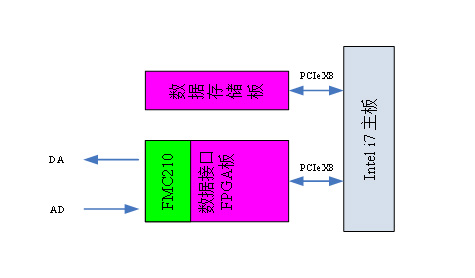

案例通過AD9613以175MSPS速率采集AD數(shù)據(jù)后,再通過PL端的ILA顯示AD數(shù)據(jù)波形,再將AD9613的A通道數(shù)據(jù)通過AD9706以175MSPS速率進行DA數(shù)據(jù)輸出。

程序功能框圖

程序功能框圖

該方案具有以下優(yōu)勢:

高速數(shù)據(jù)處理:支持175MSPS的高采樣率,適用于高頻信號采集與處理場景,同時驗證ADC和DAC功能,展示完整數(shù)據(jù)處理能力。

高精度驗證:通過集成ILA實時捕獲數(shù)字波形,并與示波器測量的模擬信號進行嚴格對比,確保信號轉換精度,為系統(tǒng)性能評估提供參考依據(jù)。

便捷開發(fā)調試:通過Vivado ILA邏輯分析儀功能,可直接觀察數(shù)字波形,支持模擬波形顯示模式,便于直觀分析信號特征。

平臺介紹

XCZU7EV是Xilinx UltraScale+ MPSoC系列高性能異構多核SoC處理器,集成PS端(四核ARM Cortex-A53+雙核ARM Cortex-R5)+PL端UltraScale+架構可編程邏輯資源。

創(chuàng)龍科技基于XCZU7EV設計的工業(yè)核心板(SOM-TLZU)支持4K@60fps H.264/H.265視頻硬件編解碼,并支持SATA大容量存儲接口。

此外,創(chuàng)龍科技基于XCZU7EV設計的工業(yè)評估板(TLZU-EVM)接口資源豐富,支持CameraLink、SDI、HDMI、DisplayPort、FMC HPC、PCIe、SATA、SFP+、Ethernet、USB3.0、CAN、RS422、Micro SD等接口,滿足用戶的項目評估需求!

Xilinx MPSoC典型應用領域

高速AD/DA案例演示

案例說明

案例實現(xiàn)了通過AD9613 ADC以175MSPS速率采集數(shù)據(jù),通過ILA顯示波形,并通過AD9706 DAC以相同速率輸出A通道數(shù)據(jù),驗證高速AD/DA功能。

案例演示

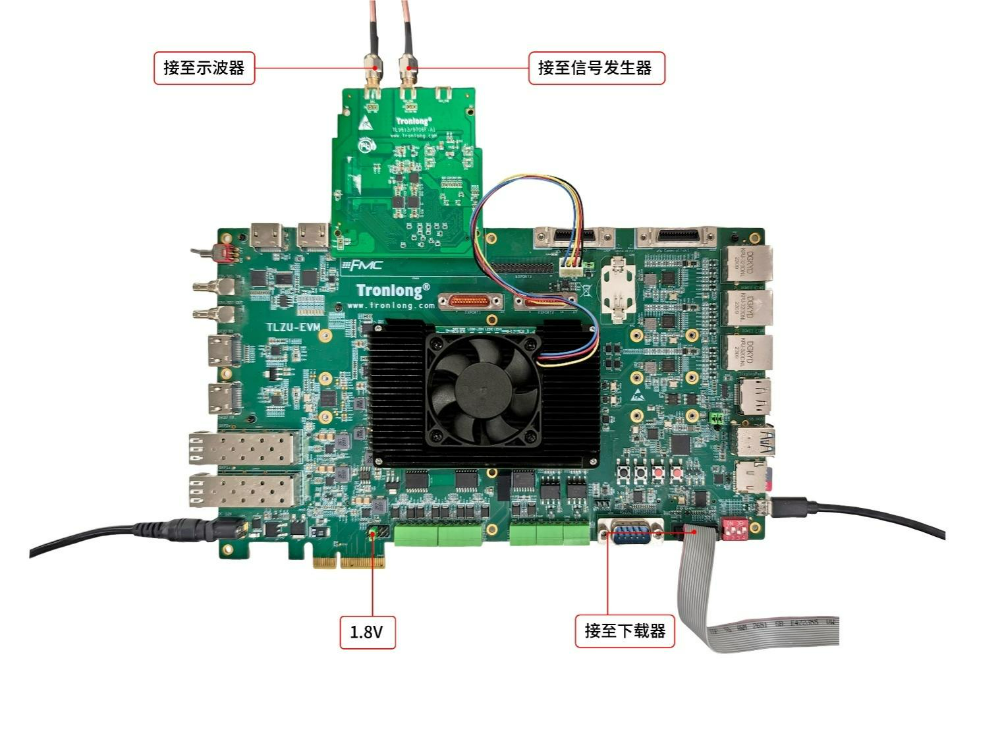

將創(chuàng)龍科技的高速AD/DA模塊TL9613/9706F連接至評估板FMC接口,評估板J1跳線帽選擇1.8V檔位。使用信號發(fā)生器向TL9613/9706F模塊的A通道(CON2)提供測試信號,信號發(fā)生器設置為一路正弦波輸出、頻率1.5MHz、峰峰值1.5Vpp、輸出負載50Ω,并使用示波器測試TL9613/9706F模塊的DAC接口(CON4)信號。

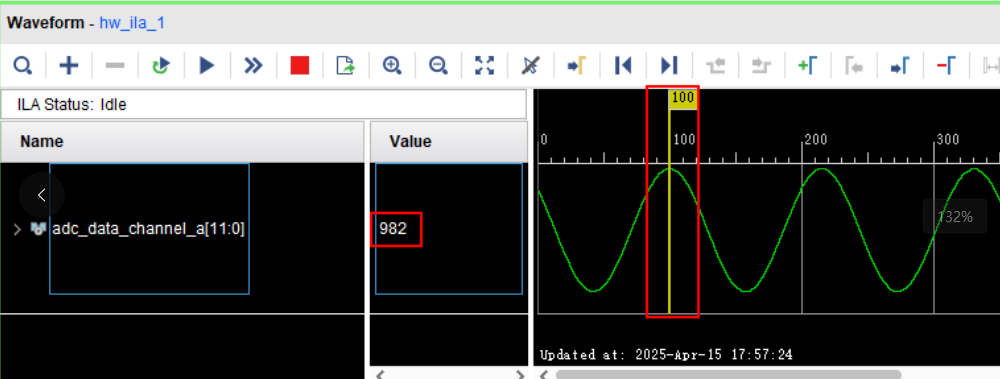

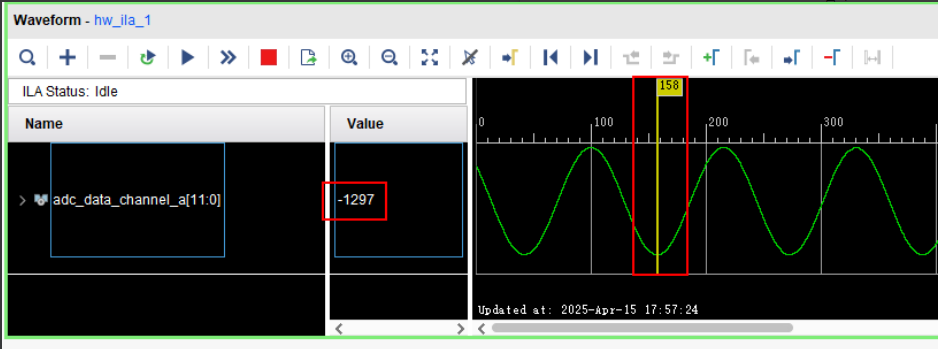

請運行程序,在Vivado工程中點擊圖標,查看到ILA觸發(fā)抓取AD數(shù)據(jù)波形。本次測得波峰值為982,波谷值為-1297,則峰峰值為982-(-1297)=2279。

實際測得信號發(fā)生器產生的測試信號的峰峰值為1.6910Vpp,根據(jù)AD9613數(shù)據(jù)手冊,理論幅值=峰峰值*增益/量程*4096=1.6910*0.511/1.75*4096=2022.49,與ILA結果基本一致。

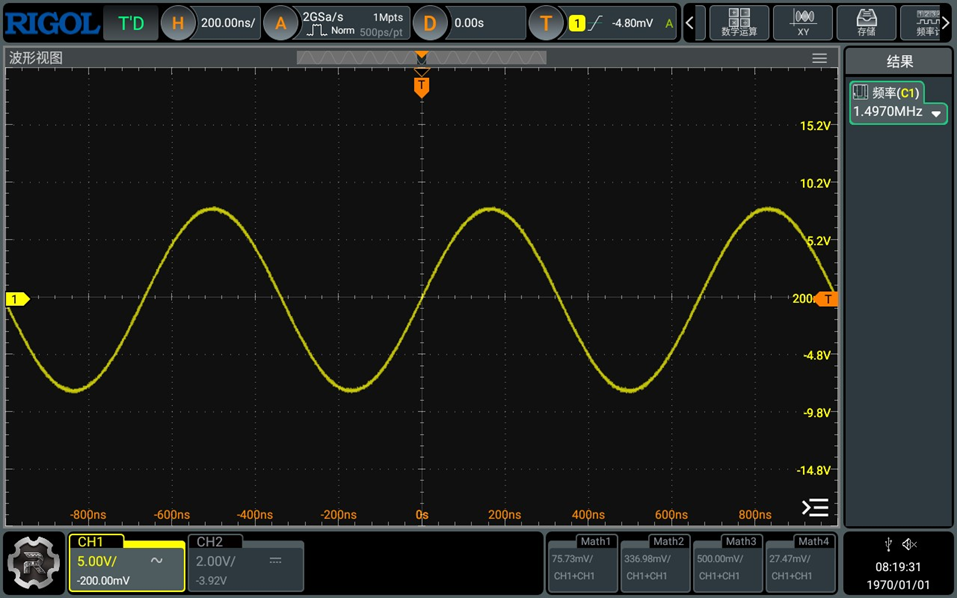

此時,可從示波器中看到DAC接口輸出頻率為1.4970MHz的正弦波,與信號發(fā)生器產生的信號基本一致。

到這里,我們的演示步驟結束。想要查看更多XCZU7EV相關的案例演示,歡迎各位工程師關注創(chuàng)龍科技微信公眾號或官網。

審核編輯 黃宇

-

Xilinx

+關注

關注

73文章

2202瀏覽量

131552 -

MPSoC

+關注

關注

0文章

203瀏覽量

25198

發(fā)布評論請先 登錄

Xilinx FPGA輸入延遲原語介紹

Xilinx FPGA中IDELAYCTRL參考時鐘控制模塊的使用

PCIe數(shù)據(jù)采集卡設計原理圖:138-1路1Gsps AD 1路1Gsps DA高速采集存儲回放設備

RDMA設計35:基于 SV 的驗證平臺

探索MAX9613:低功耗、高效能的單/雙路軌到軌I/O運算放大器

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

新品上市!AMD Zynq UltraScale+MPSoC EG異構多處理開發(fā)平臺

DA14695MOD:高效藍牙5.2模塊的全面解析

DA14535 USB開發(fā)套件硬件解析:開啟低功耗藍牙開發(fā)新征程

雙Zynq MPSoC PS側PCIe高速DMA互連解決方案

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

FMC子卡設計方案:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

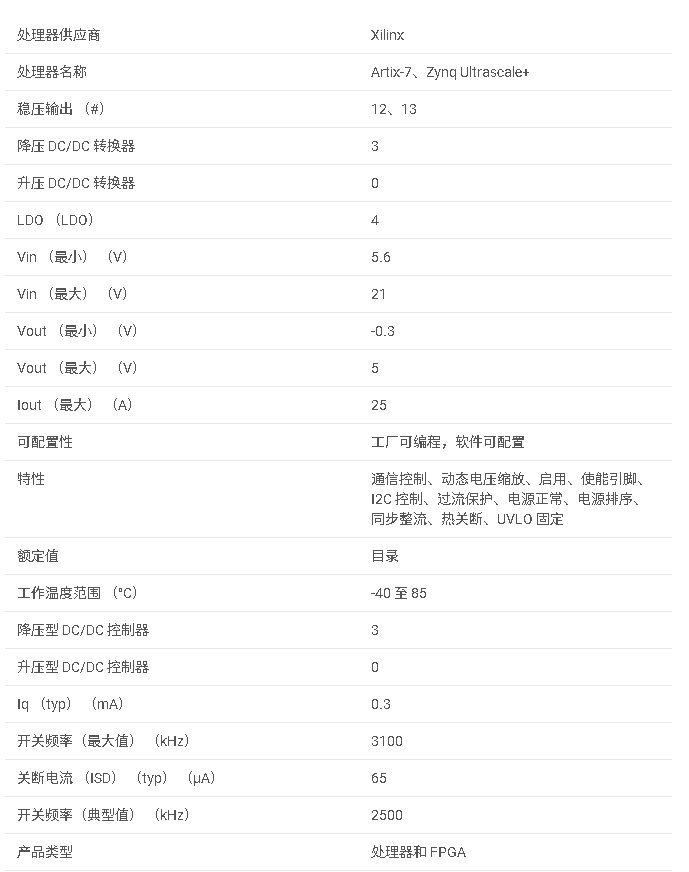

TPS650864 用于 Xilinx MPSoC 和 FPGA 的可配置多軌 PMIC數(shù)據(jù)手冊

基于AD9613與Xilinx MPSoC平臺的高速AD/DA案例分享

基于AD9613與Xilinx MPSoC平臺的高速AD/DA案例分享

評論